基于FPGA的大型LED显示屏系统设计

FPGA/ASIC技术

描述

随着平板显示技术的不断更新,大型LED显示系统利用发光二极管构成的点阵模块或像素单元组成大面积显示屏,主要显示字符、图像等信息,具有低功耗、低成本、高亮度、长寿命、宽视角等优点。近年来广泛应用在证券交易所、车站机场、体育场馆、道路交通、广告媒体等场所。

通常用单一单片机作为主控器件控制和协调大屏幕显示。由多片单片机构成的多处理器系统,其中一片作为主CPU,其他作为子CPU共同控制大屏幕的显示,该系统可以减轻主CPU 的负担,提高了LED点阵的刷新频率。但单片机的驱动频率有限,无法驱动等分辨率LED屏幕,尤其是对于多灰度级彩色大屏幕,数据送到显示屏之前要进行灰度调制重现图像的色彩,对数据的处理速度要求更高,单片机控制在速度上无法满足上述要求。因此该方案主要应用于实时性要求不高的场合,主要进行一些文字、图片等静态异步显示的控制。视频图像信号频率高、数据量大,要求实时处理,采用FPGA/CPLD设计控制电路,其中的同步控制、主从控制、读写控制和灰度调制等大量电路进行了集成,简化系统结构,便于调试且系统结构紧凑,工作可靠。与单片机控制电路相比,电路结构明显简洁,电路的面积减小,可靠性增强,调试也更为简单,由于FPGA/CPLD可以并行处理多个进程,比起单片机对任务的顺序处理效率更高,点阵的刷新频率也随之提高。

对实时性要求较高、数据量较大的场合下,可编程逻辑器件是首选的核心数据处理器。本系统考虑对于传输视频数据大小和驱动LED大屏幕刷新频率的要求,LED发送卡、接收卡均采用FPGA作为核心处理器,笔者选择Xilinx公司基于90nm工艺制造的XC3S250E-FTG256,内有25万逻辑门,最高频率可以达到600MHz,完全可以满足系统速度的要求在系统中作为扫描控制单元,同时以MCU芯片为主控制单元。采用该方案可以有效简化显示屏的电路结构,从而提高了整个控制系统的灵活性和可靠性。

1 系统的组成和工作原理

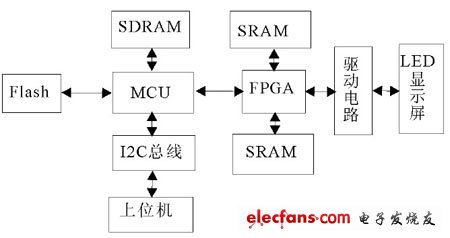

该系统采用89C51单片机和SDRAM 组成控制中心,由基于Xilinx公司的FPGA的90nm工艺制造的XC3S250E-FTG256和RAM 组成扫描控制模块,以FLASH作为存储器模块,采用以太网传输数据,组成LED屏的控制系统。系统结构如图1所示。其工作原理为:主机通过TFTP协议将图片传输给系统以太网接口模块,以太网接口模块解析协议,接收图片数据,然后将数据传输给MCU,MCU 将接收到的数据写入存储模块NAND Flash.在显示时,MCU读取FLASH 中的数据,通过SPI接口将数据传输给FPGA扫描控制模块,经扫描控制模块处理后传输到LED屏幕上显示。

图1 基于FPGA和MCU的LED显示屏控制系统框图

2 硬件系统设计

2.1存储器电路设计

本系统中需要用2片RAM 芯片作为缓存来存储视频数据,并以乒乓方式进行快速读写操作。目前主要有动态存储器(DRAM)和静态存储器(SRAM),SRAM 的读写时间短,静态功耗比较低,总线利用率高,它不需要刷新电路就能保存内部存储的数据,但是它的集成度较低,相同的容量占用体积大,价格较高,主要用于性能要求较高的领域。

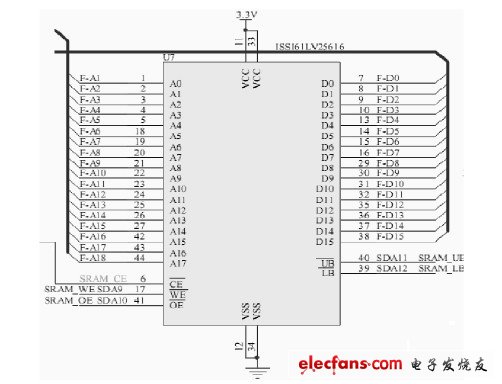

DRAM 只能将数据保持很短的时间,它使用电容存储,必须经常刷新电路来保存数据,它的读写过程比较复杂,时间较长,动态功耗较大,总线利用率比较低。不过DRAM 的存储容量大,价格便宜,被大量用在服务器和电脑中。由于DRAM 读写过程比较复杂,本系统要求存储器有快速的读写响应,所以设计中选用SRAM 作为存储器。本系统所用的LED屏大小为512×64,每个像素数据(RGB)占用24bit,则一场画面的数据量为512×64×24=768kbits.本设计选用ISSI公司的IS61LV25616芯片来存储视频数据。SAA7111输出16bit视频信号,16位数据线正好方便存储数据。它的容量为256×1 024×16bit,足够存储一场视频数据,并有留有充足的容量供系统以后的升级。SRAM 的电路设计如图2所示。

图2 SRAM 电路

2.2 FPGA的硬件设计

FPGA的硬件设计如图3所示。FPGA 需要提供大量的I/O引脚和高速的显示控制信号,所选用的基于Xilinx公司的FPGA 的90nm 工艺制造的XC3S250E-FTG256可以满足设计的要求。

图3 FPGA的硬件结构

2.3驱动电路

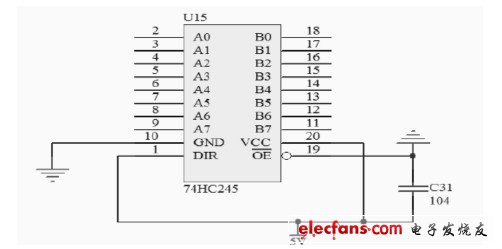

FPGA采用的电压是3.3V,而LED屏体显示电路的电压是5V的TTL逻辑电平,因此需要进行电平转换的电路。这个电路由74HC245构成,工作电压为5V,74HC245采用CMOS工艺,是一种三态输出、8组总线收发器,其输入电平兼容3.3V系统,使用外接的5V电源将输出电平提升到5V,同时为各种控制和数据信号提供驱动能力。74HC245的电路如图4所示。其中:OE为输出控制引脚,低电平为有效;DIR引脚用于控制转换方向,接高电平时表示从A向B转换,A0~A7用于输入数据信号,B0~B7用于输出转换后的数据信号。

图4 74HC245驱动电路

2.4显示板的驱动电路

LED显示板的面积很大,它的正面由LED 显示块级联而成,背面是驱动电路。由于LED的驱动电流相对较大,驱动电路应尽量和LED点阵模块靠近。因此行列驱动器一般都安装在屏体的背面。LED显示板的驱动电路中采用了74HC595芯片,是硅结构的CMOS器件,兼容低电压TTL电路,具有8位串入并出的移位、并行锁存和三态输出功能。移位寄存器和锁存器使用独立的时钟,数据SDATA 在SCLK的上升沿输入移位寄存器,在LT的上升沿进入的锁存器中去。当使能信号OE为低电平时,锁存器的数据输出到LED.74HC595芯片可以解决数据显示和数据串行传输在时间上的冲突问题,在显示1行各列数据的同时,可以准备下1列的LED数据。以1/16行扫描为例,LED显示板的驱动电路如图5所示。

CLK是移位寄存器时钟,每个脉冲将引起1位数据移入74HC595中,当1行的数据全部移完后,锁存信号LT控制数据从74HC595的寄存器移入锁存器。A、B、C、D是行扫描信号,其中A是最低位,通过4/16译码器控制LED屏的行扫描。OE是消影信号,它可以选择控制行信号或列信号,用于LED点阵是否能被点亮和控制整屏的亮度。如果OE控制列信号,它接74HC595芯片的OE端,因为只有当OE为低电平时74HC595的输出才有效,否则输出三态。如果OE控制行信号,它接到4/16译码器的使能端,低电平时行扫描不起作用。

图5 LED显示板的驱动电路

3 系统软件设计

整个系统的软件包括2部分:上位机应用软件和嵌入制单元软件。上位机软件编辑在LED显示屏上显示的数息,并实现与下位机的通信;嵌入式控制单元软件实现了接收和存储、数据输出和图像显示方式变换,从而实现LED屏的控制。

3.1上位机应用软件

上位机应用软件用Visual C++编写,主要实现显示的编辑与通讯的功能。该软件运行于WindowsXP环境中,方便用户使用。完成的功能有:(1)对显示信息进行编辑、修改功能,也可以直接调用Windows中的256色画图文件(*.bmp);(2)在上位机上对显示的内容进行预览,以保证有较好的显示效果;(3)依照上位机与I2C接口模块的协议,将信息传输给系统以I2C接口模块,从而实现显示数据的更新。

3.2嵌入式控制单元的软件

嵌入式控制单元的软件实现以下3大功能:数据接收和存储、数据输出和图像显示方式变换。(1)依照显示屏与上位机之间的通讯协议,与上位机进行通讯,接收显示数据,存入Flash存储器。(2)将待显示的数据从Flash存储器中取出,对数据进行处理,实现上移、下移、左移、右移等丰富多彩的图像显示效果。(3)通过SPI接口将数据传输给扫描控制模块,FPGA通过串并转换等将数据转换成适合LED屏驱动电路格式的数据,然后传到LED屏幕上显示出来,仿真如图6,7所示。

图6 软件模拟显示效果

图7 LED显示屏实际显示效果

4 结语

与传统的基于单片机的LED屏控制系统相比较,该系统在不增加系统成本的情况下,可支持256灰度级的全彩图文信息的显示,可以播放全彩动画;可存储较大容量的数据(64MB);通过I2C接口快速传输数据,为显示区域较大、显示内容切换频繁的大屏幕LED显示控制系统提供良好的解决方案。

-

LED显示屏设计方案2024-04-03 1483

-

Led显示屏控制系统怎么使用 led显示屏控制器怎么设置2024-02-03 15248

-

LED显示屏同步系统与异步系统的区别2023-06-12 2552

-

常规全彩LED显示屏与舞台LED显示屏的区别2023-05-16 2458

-

基于FPGA的LED显示屏灰度控制2022-11-21 1000

-

大型户外LED显示屏有着广泛应用,它的特点都有哪些2020-08-14 2425

-

如何使用FPGA和MCU进行大型LED显示屏系统设计2018-12-25 2006

-

led显示屏控制软件有哪些_九个led显示屏控制软件介绍2018-03-21 213094

-

基于STM32+FPGA的全彩LED显示屏系统的设计2017-12-28 14701

-

【NanoPi2申请】大型LED显示屏控制系统2015-12-02 2131

-

基于FPGA的LED显示屏设计2015-10-29 793

-

基于ARM和FPGA的LED显示屏控制系统的设计2011-04-17 925

-

LED显示屏,LED显示屏是什么意思2010-03-10 14163

-

LED显示屏防光衰的应用2009-11-27 1007

全部0条评论

快来发表一下你的评论吧 !