芯片内部有多小呢?芯片内部为什么能这么小?

描述

芯片藏身于城市中随处可见的电子设备,智能手机、电脑、家电等都离不开它的控制。

小小的芯片集成了庞大规模的电路****。

把芯片放大,可以看到其内部存在着密密麻麻的线路排布,就像密集交织的高速公路,仿佛在极小的尺寸上建造了一座井然有序的电路城市。

芯片内部有多小呢?如今我们在工业上运用的芯片最小制程,也就是我们人类能创造出的微小尺寸,已经达到3nm,芯片内部可以集成上百亿个晶体管。

芯片制造的“多层”思路

无数纳米级的电子元件在芯片上错落排布,是将每一个元件事先制好,再一个一个安放上去吗?

不是!我们可以换个角度看待这个问题,在纵向仔细观察,可以发现芯片是由一层层带有不同图案的片状结构纵向垒叠而成 。 如果我们将每一层事先制好,再纵向累加,二维结构能叠加成三维器件,最后形成功能丰富的芯片。

现在我们的目标变成了如何制成有特定图案的片状结构。首先我们要有能够用来印上电路图的片状材料,也就是我们常听说的硅晶圆,这是一种纯度极高的硅,经过加工后被切割成光滑、极薄的圆片。

接着,我们就像木匠,需要找到称手的工具来雕刻图案,要制成内部结构复杂且极其微小的芯片,对加工工具的尺寸要求极高。

聪明的我们找到了光这把刻刀,正是由于光具有丰富的波长,我们可以利用短波长的光来实现极其精细的加工。

我们希望通过光学曝光将图纸上设计好的电路图案转移到硅晶圆上,但是光不能对硅材料产生影响,所以需要借助一个中间材料,也就是能直接和光相互作用的光刻胶。

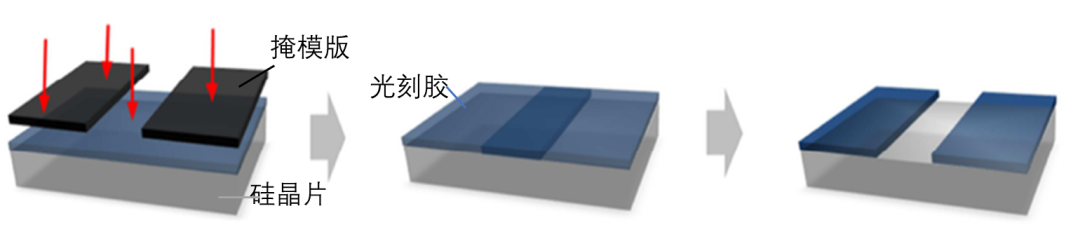

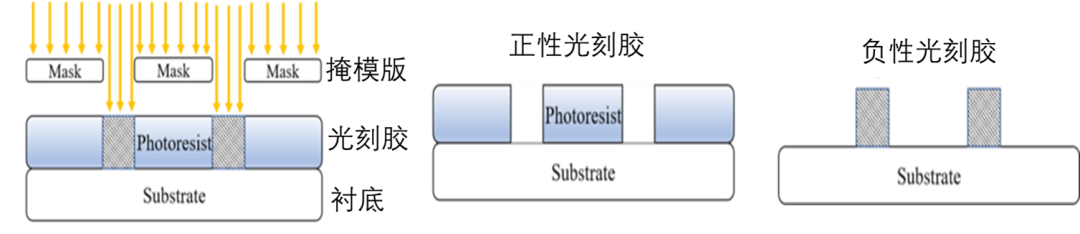

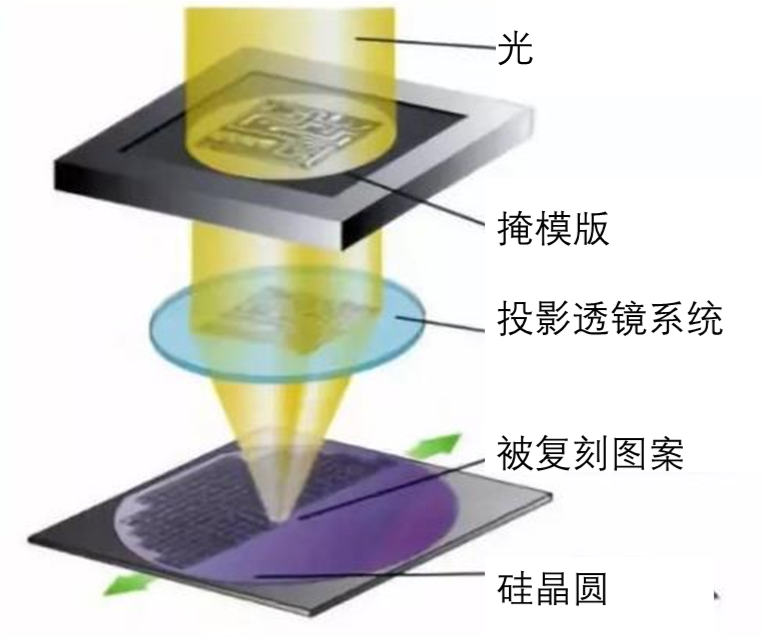

要让光实现图案的信息的传递,可以利用将光完全挡住或完全通过的方式产生明暗图案。光通过 带有电路图案的挡光板 ( 掩模版 ),可以复制掩模版的图案信息,最后和硅晶圆表面上均匀覆盖的光刻胶相互作用后,硅晶圆上出现了我们需要的图案信息。

光刻成像曝光过程 | 图源Searchmedia - Wikimedia Commons

光刻胶是光刻成像的主要承载介质,分为正胶和负胶,曝光区域更容易在显影液中溶解的为正性光刻胶,曝光区域更不易在显影液中溶解的是负性光刻胶。

曝光过程的两种结果(正胶和负胶)|图源Searchmedia - Wikimedia Commons

假设使用的是正性光刻胶,当曝光过程结束后,显影液能够溶解暴露在光下的光刻胶。接着再用化学物质溶解裸露的硅晶圆,遗留在硅晶圆表面的光刻胶能起到保护硅晶圆的作用,这就是刻蚀过程。

现在我们完成了目标,获得了带有特定电路图案的硅晶圆。在这整个过程中,大致思路其实比较流畅,但芯片制造这项代表人类巅峰智慧的精密工程包含了无数严苛的要求。

芯片内部尺寸受到什么限制?

芯片的主要元件是晶体管,一块大型芯片能有上百亿个晶体管,当我们能制造越小的晶体管,芯片能容纳的元件数越多,晶体管的功耗也会越低。

在芯片制造中,我们希望利用光在小尺度范围中创造电路图案,那么为什么光能实现这个效果呢?光的雕刻极限又在哪呢?

衍射

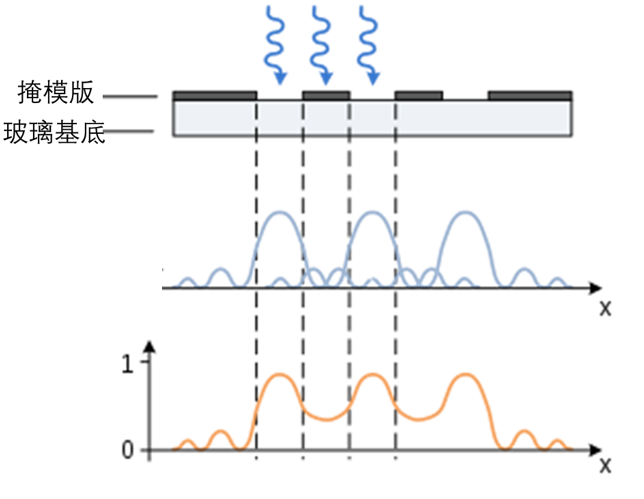

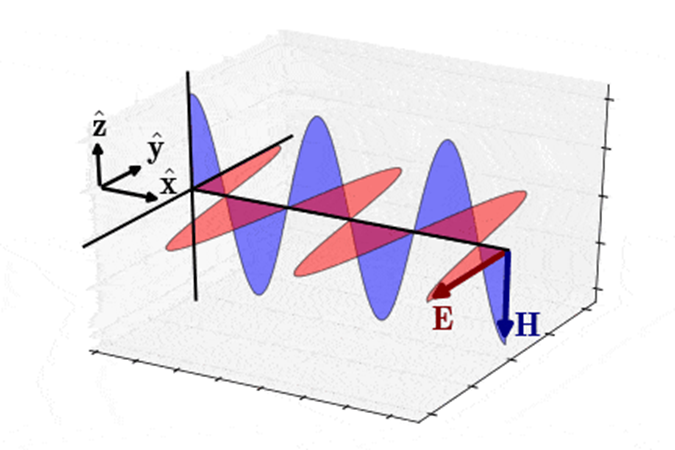

影响光的雕刻水准的主要原因是光的衍射效应。光是一种电磁波,在光刻传播过程中衍射不可避免,曝光范围就有了最小特征尺度。光的分辨率,也就是光刻胶依据光辐照来重建图形的能力有了限制。

曝光过程的衍射 | 图源Searchmedia - Wikimedia Commons

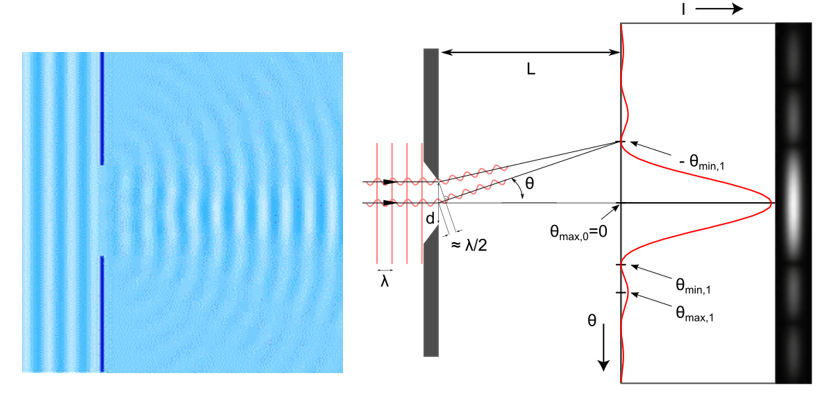

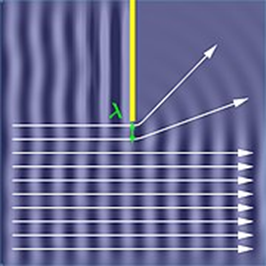

如下图所示,当一束平行光经过一个狭缝,光会以无数子波的形式在传播过程中相互干涉,形成 明暗相间的衍射图样 。

单缝衍射 | 图源Searchmedia - Wikimedia Commons

也就是说在微小尺度上考虑光的传播,有光区域不再和无光区域泾渭分明,而是出现了模糊地带,一个理想物点发出的光经过障碍物边缘后,会 偏离几何光学直线传播的特点,不再形成一个理想像点 。

这正是因为狭缝宽度和光波长尺度相当时,光的波动效果迎来了舞台,光可以利用波动效果绕开障碍物,在空间中弥散开来,形成了光发散的衍射效果,导致曝光区域范围不再精准,光的分辨率有了极限。

光的波动效果图(对比直线传播和波动效果) | 图源Searchmedia - Wikimedia Commons

分辨率

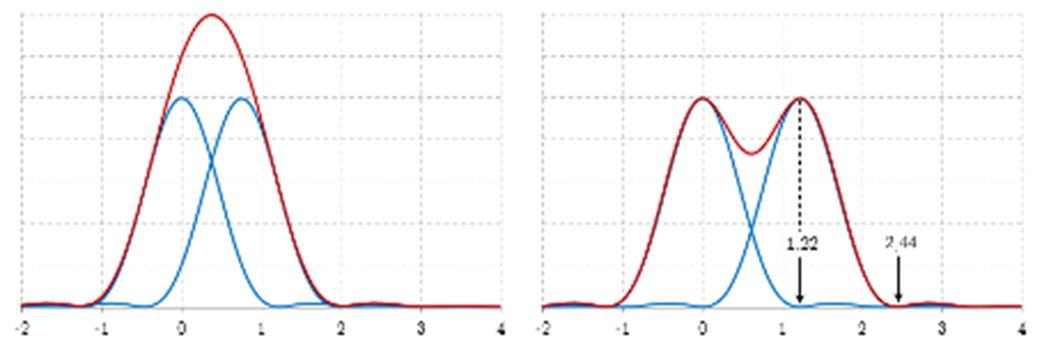

在光学成像领域,分辨率是衡量分开相邻两个物点的像的能力。理想情况下,我们希望每个物点都能产生锐利的像点,但由于衍射,实际结果为有一定大小的光斑。如果两个光斑(衍射图样)重叠程度过大,则像点难以分辨。

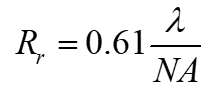

瑞利提出了一个有效的判据,分辨率计算公式为:

该分辨率表达式描述了两个光斑时恰好能分辨的极限位置——当一个光斑的极大位置与另一个光斑的第一个零值点重合。其中,λ为照明光波长。

光斑不可分辨和恰好可分辨的极限情况 | 图源Searchmedia - Wikimedia Commons

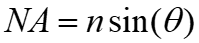

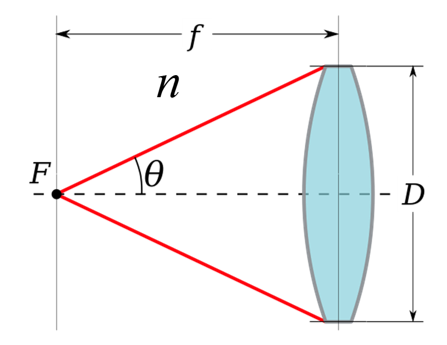

NA为数值孔径,它描述了透镜对光的汇聚能力,具体表现为平行光入射后的偏折程度(汇聚到焦点),计算表达式为:

数值孔径(n为折射率)| 图源Searchmedia - Wikimedia Commons

瑞利判据常用来评价成像质量,而光刻系统是在光刻胶中成像的。光刻胶是一种高对比度的成像介质,在某些曝光条件下,虽然光学分辨率已经达到了瑞利判据的分辨极限以下,但光刻胶 仍然可以呈现较好的成像结果,实现加工的目标 。

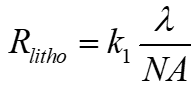

光刻成像的分辨率为:

Rlitho为光刻系统可分辨的图形周期;k1为工艺因子****。

光刻

芯片制造中光刻是最复杂、昂贵且关键的工艺,通常使用投影式光刻系统 将掩模版的电路结构图投射到硅晶片的表面 。

光学透镜可以聚集衍射光提高成像质量,在光刻技术中为得到尽可能小的图案,在掩模板和光刻胶之间采用了一种具有缩小倍率的投影成像物镜。

投影式光刻系统 | 图源网络

如何打磨光这把刻刀?

我们现在知道了:光的最小加工尺度(分辨率)决定了芯片能小到什么程度。如何来让芯片变得更小呢?我们需要让分辨能力更强,让芯片上的电路城市功能更精进。

根据光刻分辨率公式中的三项,我们有了三种方案来打磨光这把刻刀。

增大光刻系统的数值孔径

光刻成像系统中的投影物镜的数值孔径越大,分辨能力就越优越。具体操作是设计 浸润式光刻机 ,即在晶圆和投影物镜最后一面镜头之间填充高折射率的介质。

缩短波长

光刻过程的光波长已经经历了G线(432nm)、I线(365nm)、KrF(248nm)以及ArF(193nm)的深紫外波段的发展历程,目前**13.5nm波长的极紫外光刻机(EUV)**已经投入使用。

减小工艺因子

通过优化光刻工艺参数也能提高光刻分辨率,如改善光照条件、光刻胶工艺和掩模版设计等,这些方法都能减小工艺因子k 1 ,被称为分辨率增强技术(RET)。

电磁波 | 图源网络

光是电磁波,因此包含了振幅、相位、偏振态和传播方向等信息。光刻分辨率增强技术就是通过调控光的以上四种信息,让光刻胶上获得更细小的图形结构。例如离轴照明技术可以改变振幅和相位,光学邻近效应修正技术可以改变光波振幅,光源—掩模联合优化可以改变光波的传播方向、振幅和相位。

各个工艺节点和光刻技术的关系表 | 来源:萨科微半导体官网,ASML,中泰证券研究所

纵览光刻机的发展历程,我们的确在沿着不断缩小波长的途径上奔跑。观察表中数据,当光源波长相同时,我们依然在不断缩小制程,这是数值孔径、工艺因子以及其他复杂技术的功劳。

审核编辑:刘清

-

ADS1298芯片内部有无时钟源呢?2025-02-08 449

-

芯片内部的组成有哪些YS YYDS 2023-06-28

-

请问高手们STM32F105芯片的内部flash能快速擦除吗?2015-04-13 8096

-

芯片外围电路不集成进入芯片内部的原因是什么2021-10-25 1489

-

浅析芯片的内部构造2021-12-18 6122

-

2nm芯片有多牛 2nm芯片何时量产2022-07-06 3421

-

设计好的芯片内部是怎样的2022-07-08 7163

-

芯片的内部线路图如何设计2022-08-29 10157

-

TL494芯片内部原理框图2022-12-05 1693

-

芯片内部RTC与外部RTC有何区别?2023-05-26 7975

-

芯片内部电路的基本组成部分2023-11-06 3496

-

系统内部电路中 主芯片内部电源提供 EOS 防护2023-12-29 1940

-

提供系统内部电路中 主芯片内部电源提供 EOS 防护方案应用2024-01-24 1470

-

集成芯片内部组成2024-03-20 2395

-

集成芯片内部引脚排列原理2024-03-21 4480

全部0条评论

快来发表一下你的评论吧 !