RISC-V开源指令集全面指南与解析

描述

RISC-V 是一个最新的,清晰的,简约的,开源的 ISA,它以过去 ISA 所犯过的错误为鉴。RISC-V 架构师的目标是让它在从最小的到最快的所有计算设备上都能有效工作。遵循冯诺依曼 70 年前的建议,这个 ISA 强调简洁性来保证它的低成本,同时有着大量的寄存器和透明的指令执行速度,从而帮助编译器和汇编语言程序员将实际的重要问题转换为适当的高效代码。 本文来自“RISC-V手册开源指令集指南”。RISC-V(“RISC five”)的目标是成为一个通用的指令集架构(ISA):

它要能适应包括从最袖珍的嵌入式控制器,到最快的高性能计算机等各种规模的处理器。

它应该能兼容各种流行的软件栈和编程语言。

它应该适应所有实现技术,包括现场可编程门阵列(FPGA)、专用集成电路(ASIC)、全定制芯片,甚至未来的设备技术。

它应该对所有微体系结构样式都有效:例如微编码或硬连线控制;顺序或乱序执行流水线; 单发射或超标量等等。

它应该支持广泛的专业化,成为定制加速器的基础,因为随着摩尔定律的消退,加速器的重要性日益提高。

它应该是稳定的,基础的指令集架构不应该改变。更重要的是,它不能像以前的专有指令集架构一样被弃用,例如AMD Am29000、Digital Alpha、Digital VAX、Hewlett Packard PA-RISC、Intel i860、Intel i960、Motorola 88000、以及Zilog Z8000。

RISC-V的不同寻常不仅在于它是一个最近诞生的指令集架构(它诞生于最近十年,而大多数其他指令集都诞生于20世纪70到80年代),而且在于它是一个开源的指令集架构。与几乎所有的旧架构不同,它的未来不受任何单一公司的浮沉或一时兴起的决定的影响(这一点让许多过去的指令集架构都遭了殃)。它属于一个开放的,非营利性质的基金会。

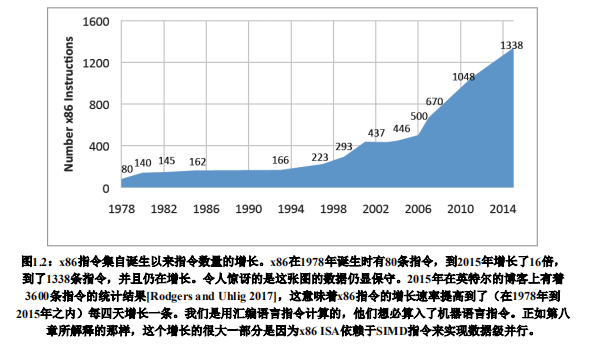

RISC-V基金会的目标是保持RISC-V的稳定性,仅仅出于技术原因缓慢而谨慎地发展它,并力图让它之于硬件如同Linux之于操作系统一样受欢迎。 计算机体系结构的传统方法是增量ISA,新处理器不仅必须实现新的ISA扩展,还必须实现过去的所有扩展。目的是为了保持向后的二进制兼容性,这样几十年前程序的二进制版本仍然可以在最新的处理器上正确运行。这一要求与来自于同时发布新指令和新处理器的营销上的诱惑共同导致了ISA的体量随时间大幅增长。 例如,图1.2显示了当今主导ISA80x86的指令数量增长过程。这个指令集架构的历史可以追溯到1978年,在它的漫长生涯中,它平均每个月增加了大约三条指令。

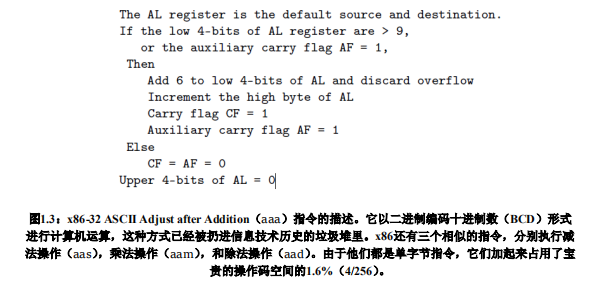

这个传统意味着x86-32(我们用它表示32位地址版本的x86)的每个实现必须实现过去的扩展中的错误设计,即便它们不再有意义。例如,图1.3描述了x86的ASCII Adjust afterAddition(aaa)指令,该指令早已失效。

作为一个类比,假设一家餐馆只提供固定价格的餐点,最初只是一顿包含汉堡和奶昔的小餐。随着时间的推移,它会加入薯条,然后是冰淇淋圣代,然后是沙拉,馅饼,葡萄酒,素食意大利面,牛排,啤酒,无穷无尽,直到它成为一顿大餐。食客可以在那家餐厅找到他们过去吃过的东西,尽管总的来说这样做可能没什么意义。这样做的坏处是,用餐者为每次晚餐支付的宴会费用不断增加。

RISC-V的不同寻常之处,除了在于它是最近诞生的和开源的以外,还在于:和几乎所有以往的ISA不同,它是模块化的。它的核心是一个名为RV32I的基础ISA,运行一个完整的软件栈。

RV32I是固定的,永远不会改变。这为编译器编写者,操作系统开发人员和汇编语言程序员提供了稳定的目标。模块化来源于可选的标准扩展,根据应用程序的需要,硬件可以包含或不包含这些扩展。这种模块化特性使得RISC-V具有了袖珍化、低能耗的特点,而这对于嵌入式应用可能至关重要。RISC-V编译器得知当前硬件包含哪些扩展后,便可以生成当前硬件条件下的最佳代码。

惯例是把代表扩展的字母附加到指令集名称之后作为指示。例如,RV32IMFD将乘法(RV32M),单精度浮点(RV32F)和双精度浮点(RV32D)的扩展添加到了基础指令集(RV32I)中。 在介绍 RISC-V 这个 ISA 之前,了解计算机架构师在设计 ISA 时的基本原则和必须做出的权衡是有用的。如下的列表列出了七种衡量标准。页边放置了对应的七个图标,以突出显示 RISC-V 在随后章节中应对

审核编辑:黄飞

-

浅谈RISC-V指令集架构的来龙去脉2020-01-24 7261

-

【RISC-V开放架构设计之道|阅读体验】RISC-V基础整数指令集2024-01-31 871

-

RISC-V指令集的特点总结2024-08-30 1210

-

RISC-V和arm指令集的对比分析2024-09-28 1741

-

RISC-V的指令集位宽的几点学习心得2024-10-31 1870

-

RISC-V指令集概述2024-11-30 1165

-

RISC-V指令集架构微控制器相关知识2021-12-16 1468

-

RISC-V-Reader-Chinese-v2p1 RISC-V手册(中文) RISC-V开源指令集的指南2022-04-22 13062

-

印度确立RISC-V为国家指令集 中国CPU指令集还在孤芳自赏2017-12-19 8224

-

RISC-V指令集的起源与发展历史2021-05-02 9152

-

为什么做开源高性能RISC-v核,香山开源高性能RISC-V处理器开发流程2021-06-22 3539

-

RT-Thread全球技术大会:RISC-V指令集开源软件生态介绍2022-05-27 1858

-

简单讲讲RISC-V指令集CPU的参数2022-08-07 5082

-

基于精简指令集的RISC-V内核的单片机2022-10-17 3588

-

一个基于精简指令集原则的开源指令集架构RISC-V2023-01-30 4794

全部0条评论

快来发表一下你的评论吧 !