CPLD实现DDS正弦信号发生器设计

嵌入式设计应用

134人已加入

描述

本文实现了DDS正弦信号的发生,限于CPLD的128宏单元不够用也不知道怎么优化,后来就干脆把按键、频率显示、频率控制字交给单片机控制产生,再由单片机讲频率控制字传送给CPLD,这样就实现了频率的控制。最终产生的正弦信号频率范围为1HZ~30KHZ,频率可步进1HZ也可通过单片机预置,也可以自动扫频信号。起先出来的频最大误差达到2HZ多,觉得不对劲出来的频率应该很精确不会有这么大的误差,后来发现原来是晶振不准有点误差,后来经程序修改使输出最大频率误差在0.1HZ以内,经过这几天的努力总算感到了一点的欣慰。

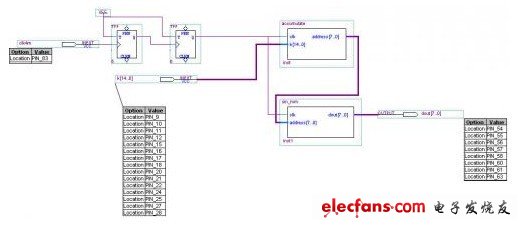

这是VHDL顶层模块:

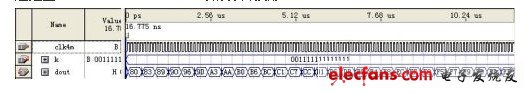

这是当k=001111111111111时的仿真波形:

单片机控制6个数码管显示当前的频率,P1口接4个功能按键,分别是+、-、选择和扫频,再用两片574向CPLD输出频率控制字。限于时间暂时做到这么多。

由于是用DAC0832转换的(转换时间1us)所以晶振就限制在1M之内了,出来的最大频率,根据奈奎斯特采样定理也就限制在0.5MHZ之内了(不过失真很大的,取小点好了),最后对出来的波形再做滤波就可以了。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于FPGA 的DDS正弦信号发生器的设计和实现2024-03-24 932

-

怎么实现基于FPGA+DDS的正弦信号发生器的设计?2021-05-11 1768

-

如何利用FPGA和DDS技术实现正弦信号发生器的设计2021-04-28 1337

-

正弦波信号发生器基本原理与设计2018-01-14 86326

-

DDS工作原理及基于AD9854的信号发生器的设计2017-11-16 1949

-

基于DDS的信号发生器设计2016-01-11 1143

-

基于ARM与DDS的高精度正弦信号发生器设计2016-01-04 1031

-

信号发生器原理_DDS芯片及应用_DDS信号发生器设计2015-06-23 8159

-

一种新型的正弦信号发生器的设计与实现2012-05-23 3470

-

基于AD9851的正弦信号发生器设计2010-12-27 1754

-

DDS数字移相正弦信号发生器的设计2010-10-20 723

-

基于DDS技术的信号发生器研究与实现策略2010-04-23 3079

-

AD9851的正弦信号发生器设计2010-03-29 4612

-

基于DDS技术的高频正弦波发生器的设计2009-08-10 1264

全部0条评论

快来发表一下你的评论吧 !