Nvidia芯片工艺先进封装演进洞察

处理器/DSP

描述

半导体工艺演进洞察

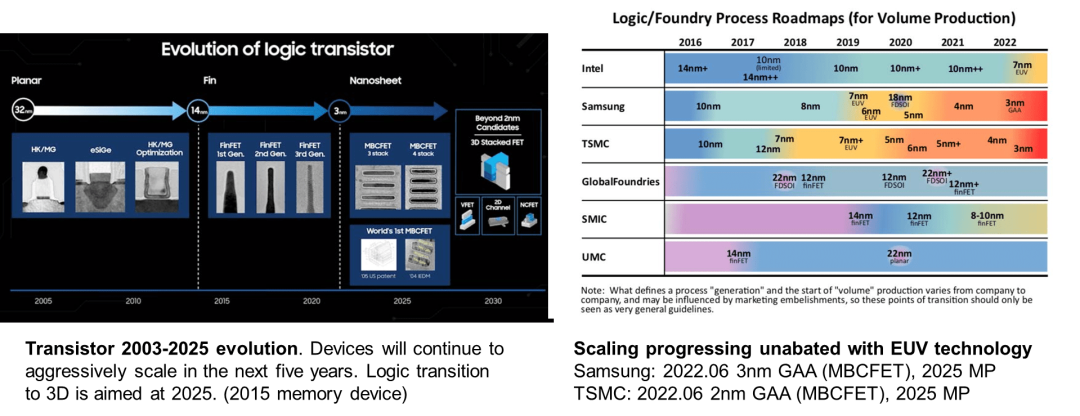

根据IRDS的乐观预测,未来5年,逻辑器件的制造工艺仍将快速演进,2025年会初步实现Logic器件的3D集成。TSMC和Samsung将在2025年左右开始量产基于GAA (MBCFET)的2nm和3nm制程的产品 [17]。

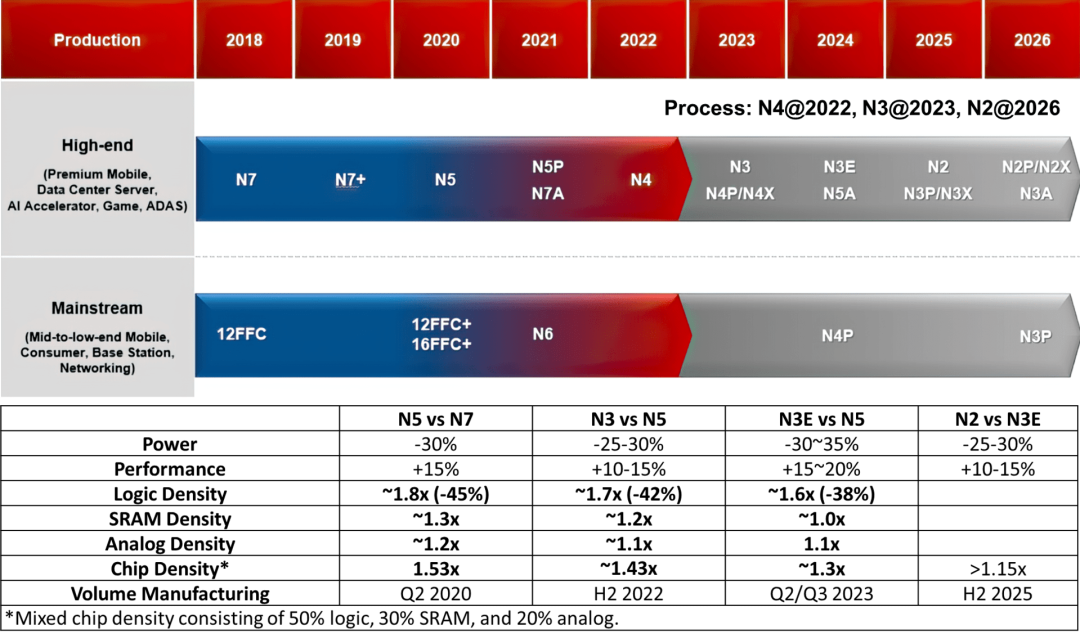

按照TSMC给出的工艺演进路标,2023~2025年基本以3nm工艺为主,2nm工艺在2025年以后才会发布。3nm技术已经进入量产阶段,N3工艺和N3E版本已经于2023年推出。2024年下半年开始生产N3P版本,该版本将提供比N3E更高的速度、更低的功耗和更高的芯片密度。此外,N3X版本将专注于高性能计算应用,提供更高的时钟频率和性能,预计将于2025年开始量产 [18]。工艺演进的收益对于逻辑器件的收益小于50%,因此,未来单芯片算力提升将更依赖于先进封装技术。

先进封装演进洞察

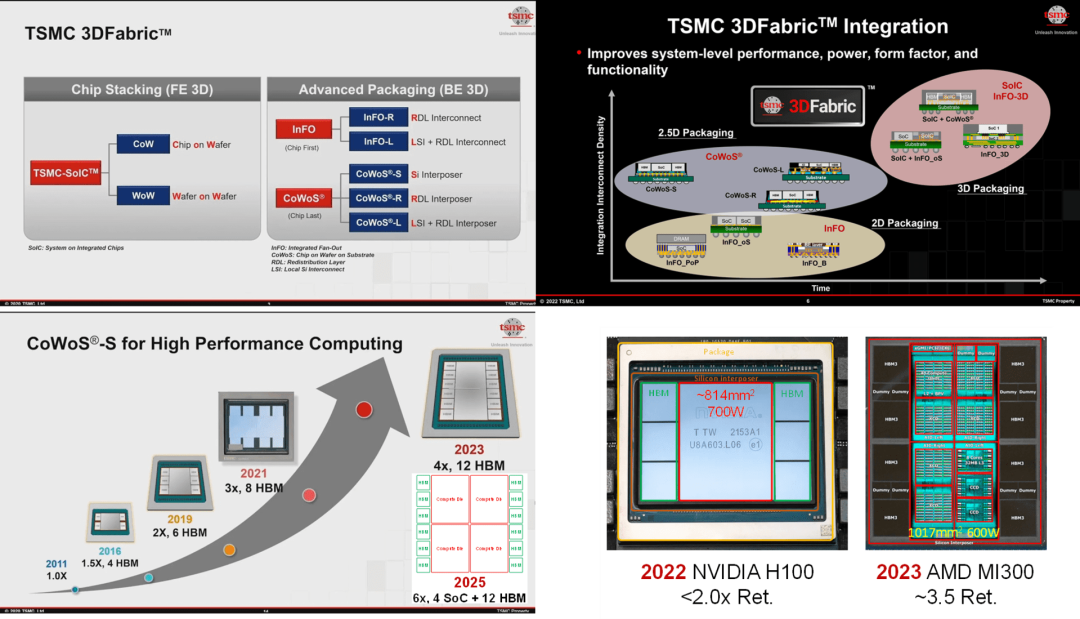

TSMC的CoWoS先进封装工艺封装基板的尺寸在2023年为4倍Reticle面积,2025年将达到6倍Reticle面积 [19]。当前Nvidia H100 GPU的封装基板尺寸小于2倍Reticle面积,AMD的MI300系列GPU的封装基板尺寸大约为3.5倍Reticle面积,逼近当前TSMC CoWoS-L工艺的极限。

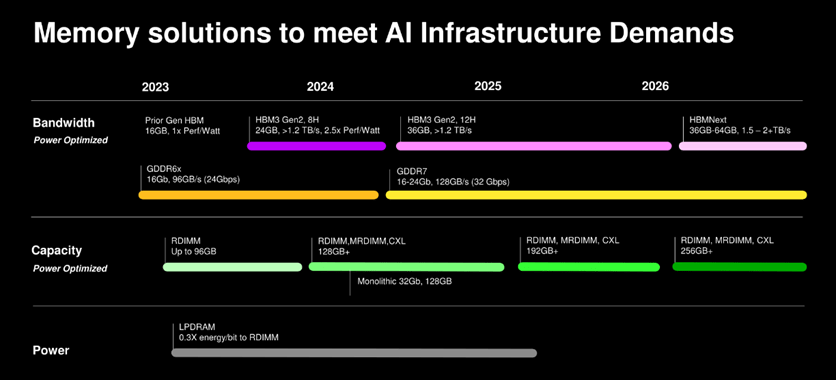

HBM内存演进洞察

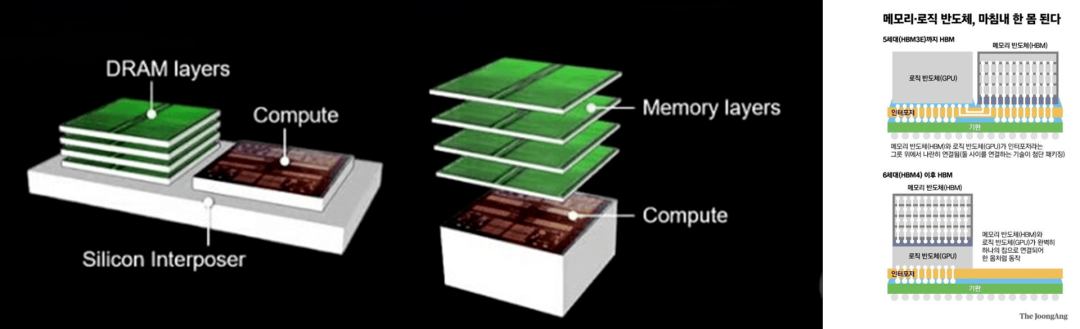

HBM内存的容量预计将在2024年达到24GB,并在2025年进一步增长至36GB [20]。HBM4预计将带来两个重要的变化:首先,HBM接口位宽将从1024扩展到2048;其次,业界正在尝试将HBM内存Die直接堆叠在逻辑Die的上方 [21][22]。这两个变化意味着HBM内存的带宽和单个封装内能容纳的容量都将持续增长。

据报道,SK海力士已经开始招聘CPU和GPU等逻辑半导体的设计人员。该公司显然正在考虑将HBM4直接堆叠在处理器上,这不仅会改变逻辑和存储器设备的传统互连方式,还会改变它们的制造方式。事实上,如果SK海力士成功实现这一目标,这可能会彻底改变芯片代工行业 [21][22]。

推演假设

本文基于两个前提假设来推演Nvidia未来AI芯片的架构演进。首先,每一代AI芯片的存储、计算和互联比例保持大致一致,且比上一代提升1.5到2倍以上;其次,工程工艺演进是渐进且可预测的,不存在跳变,至少在2025年之前不会发生跳变。到2025年,工艺将保持在3nm水平,但工艺演进给逻辑器件带来的收益预计不会超过50%。同时,先进封装技术预计将在2025年达到6倍 Reticle面积的水平。此外,HBM内存容量也将继续增长,预计在2024年将达到24GB,而在2025年将达到36GB。

作者:陆玉春

审核编辑:黄飞

-

盘点先进封装基本术语2023-07-12 2020

-

HRP晶圆级先进封装替代传统封装技术研究(HRP晶圆级先进封装芯片)2023-11-30 4335

-

先进封装技术的演进过程2023-12-06 2058

-

其利天下技术开发|目前先进的芯片封装工艺有哪些2025-01-07 2572

-

中美贸易战,国产芯片发展艰难,先进封装助力中国芯突围!#芯片封装 #先进封装 #华芯邦 #孔科微电子 2025-01-20

-

中国芯片被美国“卡脖子”?先进封装Chiplet或许就是破局关键!#先进封装 #芯片封装 #华芯邦 #孔科微电子 2025-01-22

-

多芯片整合封测技术--种用先进封装技术让系统芯片与内存达到高速传输2009-10-05 7512

-

怎样衡量一个芯片封装技术是否先进?2011-10-28 2940

-

芯片封装测试工艺教程教材资料2012-01-13 62427

-

开年首会再创新高!先进封装与键合技术同芯创变,燃梦赢未来!2023-02-28 2331

-

先进封装演进,ic载板的种类有哪些?2023-09-22 5334

-

FCBGA先进封装演进趋势 FCBGA基板技术趋势2023-12-12 3197

-

芯和半导体将参加2024集成电路特色工艺与先进封装测试产业技术论坛2024-11-27 1583

-

先进封装中RDL工艺介绍2025-01-03 7040

-

芯片封装工艺详解2025-04-16 3190

全部0条评论

快来发表一下你的评论吧 !