Chiplet封装用有机基板的信号完整性设计

描述

引 言

摩尔定律在设计、制造、封装3个维度上推动着集成电路行业发展。随着硅工艺节点的逐代更新,每平方毫米的晶体管数量从1.8万个增加到5000万个,芯片功能也从单纯的数字逻辑扩展到集数模转换、FPGA、存储器件、高速接口于一体,这一进程推动了片上系统(SoC)的产生,从而将电子信息系统的发展推向了新的高度[1]。

随着SoC的发展,其高复杂度、长周期、低良率的特点导致制程微缩的研发投入和加工成本急剧攀升。为了解决这些问题,将不同功能的模块从大规模单芯片上解耦成为新的发展方向。通过将多个单功能或多功能的IP核芯片化,再通过中后道技术对其进行复用和集成,以形成1个完整的系统,即芯粒(Chiplet)架构技术[2-4]。相较于传统的SoC技术,Chiplet架构技术的各计算单元和接口可以选择不同的工艺制程,以满足不同器件的异构集成需求。由于单颗Chiplet的面积小,其制造过程中的良率得以提升,从而可以降低制造成本。同一款Chiplet可以在不同产品中重复应用,不同款Chiplet可以根据市场需求灵活组合,以缩短产品上市时间。2022年初,Intel发布了UCIe标准[5-7],该标准对Chiplet协议层、芯片间适配、物理层、接口等内容进行了规范性描述,并更新了时钟结构、功率噪声、电源效率等内容。2022年12月,由国内集成电路领域的相关企业和专家制定的《小芯片接口总线技术要求》团体标准发布。2023年初,中国Chiplet产业联盟牵头发布《芯粒互连接口标准》。在中美贸易摩擦升级、技术制裁加剧的背景下,国内正不断研究UCIe的兼容和替代方案,以不断提升自身的技术实力和竞争力。

本文围绕UCIe中关于电气物理层的相关内容,对不同封装类型和互连通道的电气指标进行解读,并结合有机基板工艺,从设计和仿真的角度探讨了应对Chiplet互连的标准封装方案的技术可行性,有助于推动国内芯粒互连集成技术的发展。

01

Chiplet封装方案及模型

1.1 典型Chiplet封装方案

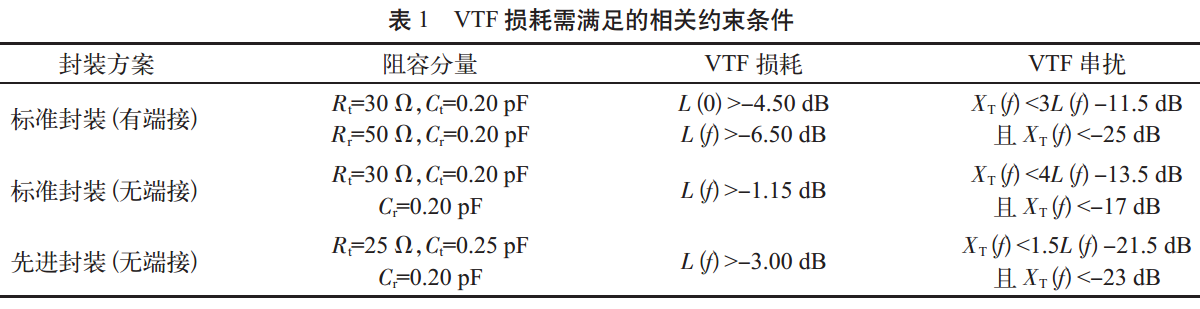

按照封装结构,系统集成技术可分为2D、2.5D和3D封装;按照封装材料,基板可分为硅基板和有机基板;在UCIe中,Chiplet封装方案分为先进封装方案和标准封装方案。

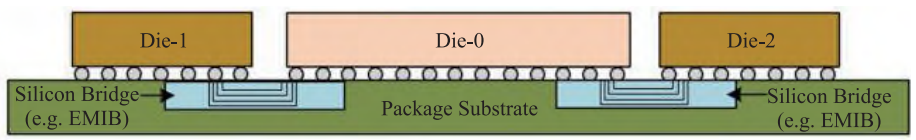

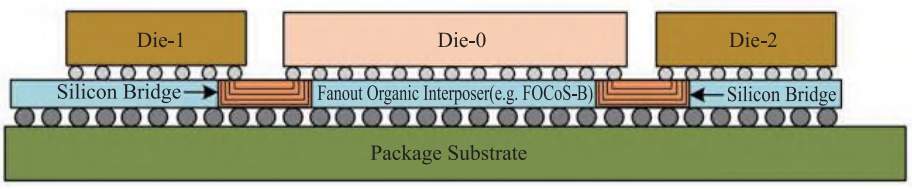

在UCIe中,采用先进封装方案的模块被称为先进封装模块,1个先进封装模块应当包含1对时钟,64个单端数据通道(用于发送和接收数据的有效通道)以及1个跟踪通道。典型的先进封装技术包括Intel的嵌入式多芯片互连桥接(EMIB)技术、台积电的CoWoS(Chip on Wafer on Substrate)技术[9]以及日月光的FOCoS-B(Fan-Out Chip on Substrate Bridge)技术,不同先进封装方案的结构如图1所示。以上3种先进封装技术的共同特点是采用2.5D异构集成方式,将硅基板埋嵌在有机基板中以实现混合使用,利用硅基板实现高密度、短互连,利用有机基板完成剩余互连。先进封装方案适用于具备多引脚和高带宽需求的产品,如高带宽存储(HBM)接口,其由1 024个I/O引脚组成,并需要满足100 GB/s以上的带宽要求,其缺点是加工成本很高,难以实现长距离互连,在灵活性方面存在不足。

(a) 嵌入桥接芯片基板(EMIB)

(b) 硅转接板2.5D集成(CoWoS)

(c) 有机转接板2.5D集成(FOCoS﹣B)

图1 不同先进封装技术结构

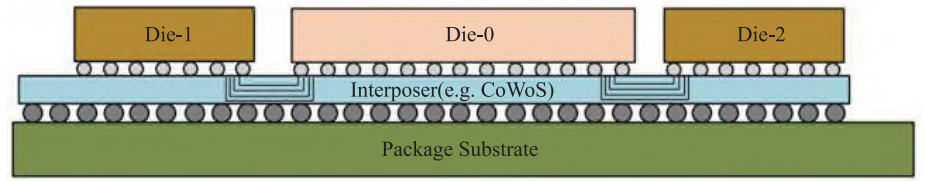

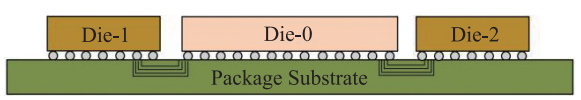

在UCIe中,标准封装方案依托于2D结构,通过有机基板实现互连,采用标准封装方案的结构如图2所示。每个标准封装模块由1对时钟、16个单端数据通道以及1个跟踪通道组成。典型的集成Chiplet的标准封装技术,其代表是AMD公司提出的IF(Infinity Fabric)技术,其分布式架构由可扩展数据结构和可扩展控制结构组成,已经在第一代和第二代的霄龙处理器中得到应用。标准封装方案的技术成熟且成本较低,有机基板具有较低的介质损耗,能够满足高频率、高速、长距离的信号传输需求,布线灵活度高,适用于各种集成方案。标准封装方案的主要缺点是互连密度低,导致带宽受限。

图2 采用标准封装方案的结构

1.2 Chiplet封装电气互连验证

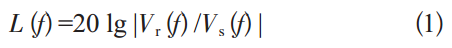

在UCIe中,针对标准封装和先进封装方案中的电气互连通道,采用电压传递函数(VTF)作为衡量电气互连通道损耗和串扰的指标。VTF可以基于发送端(TX)/接收端(RX)的阻容分量(Rt、Ct、Rr、Cr)对无源通道的微波散射参数(S参数)进行转换。相较于使用S参数,使用VTF可以综合地评估电气互连通道的性能。将VTF损耗定义为L(f),L(f)为TX电压Vr(f)与RX电压Vs(f)的比值,单位为dB,其计算公式为

在直流情形下,将直流耗损定义为L(0),其与通道寄生电阻Rchannel相关,L(0)的计算公式为

其中,Rt为TX的电阻,Ct为TX的电容,Rr为RX的电阻、Cr为RX的电容。

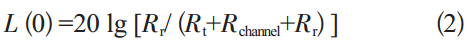

将VTF串扰定义为XT(f),其为非预期接收端与发送端功率比的叠加,XT(f)的计算公式为

其中,n为非预期接收端数量,Vai(f)为对应非预期接收端观测电压。

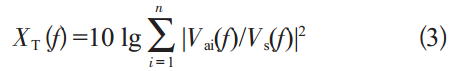

在两端阻容作用下,VTF曲线与S参数在描述传输通道的频域特性方面存在明显的不同。因此,在UCIe中,在16 Gbit/s的速率下,VTF损耗需要满足一定的约束条件,相关约束条件如表1所示。

表1 VTF损耗需满足的相关约束条件

市面上暂时没有用于VTF仿真的专用工具,为进一步解读UCIe中的指标,采用Keysight ADS仿真工具中的传输线模组,通过交流仿真模块的转换,对比3种阻容配置下的VTF损耗和VTF串扰,如图3所示,同时比较特定驱动能力下的RX眼图。

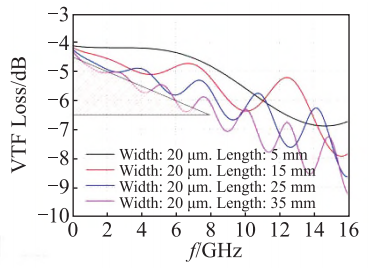

(a)线长对VTF损耗的影响(标准封装50 Ω端接)

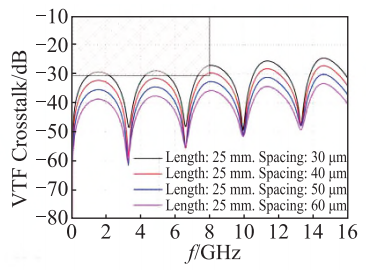

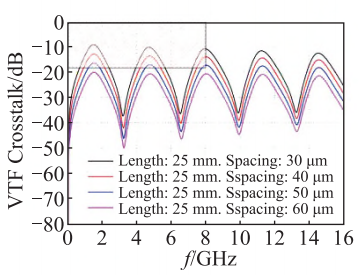

(b)线距对VTF串扰的影响(标准封装50 Ω端接)

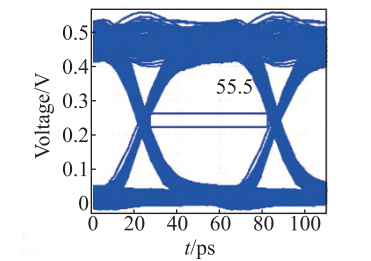

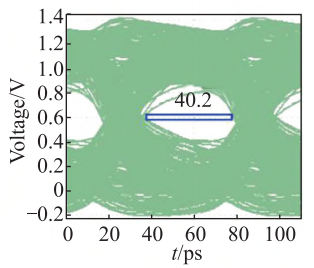

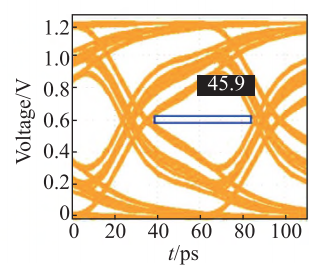

(c)线长25 mm、线宽20 μm、线距40 μm条件下的眼图(标准封装50 Ω端接)

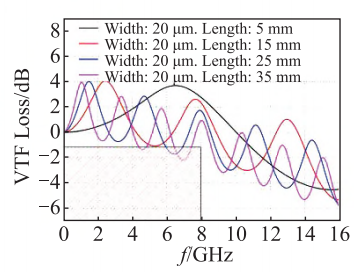

(d)线长对VTF损耗的影响(标准封装无端接)

(e)线距对VTF串扰的影响(标准封装无端接)

(f)线长25 mm、线宽20 μm、线距40 μm条件下的眼图(标准封装无端接)

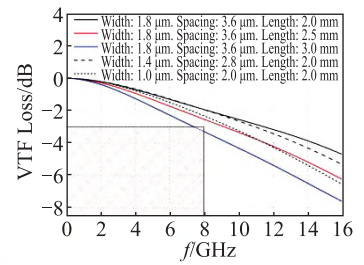

(g)线长对VTF损耗的影响(先进封装无端接)

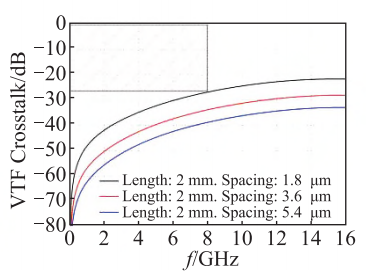

(h)线距对VTF串扰的影响(先进封装无端接)

(i)线长2 mm、线宽1.8 μm、线距3.6 μm条件下的眼图(先进封装无端接)

图3 16 Gbit/s速率下3种阻容配置的VTF损耗、VTF串扰及对应眼图

按照无锡中微高科电子有限公司的有机基板设计标准进行设计,使用的介质材料的相对介电常数DK=3.2、介电损耗角正切DF=0.006,将线宽设计为20 μm,以匹配50 Ω的特征阻抗。与端口匹配的插入损耗相比,VTF损耗曲线呈现随频率和线长的增加而增大的趋势。RX端接50 Ω电阻时,直流损耗偏离0点,而VTF损耗呈现与线长相关的振荡周期。在UCIe中,当频率为0~8 GHz时,要求VTF损耗不侵入mask区域(评估VTF损耗是否符合要求的阈值)。从图3(a)可知,当线长大于25 mm时,VTF损耗会超出限定范围。从图3(b)可知,当线距为40 μm时,红色曲线在8 GHz附近侵入mask区域,此时常规的封装设计无法满足VTF串扰的限定范围,因此,当线宽为20 μm时,线距应大于40 μm,即大于2倍的线宽。在实际设计中,需要进一步确保布线和过孔的回流效果。通过使用具有9 mA等效驱动能力的TX缓冲器,能够在50 Ω端接条件下驱动RX,实现450 mV的电压摆幅。从图3(c)可知,眼高为40 mV,眼宽为55.5 ps(0.89 UI),满足UCIe要求。

在无端接条件下,标准封装的互连线性能受到寄生电感和RX电容的影响。从图3(d)可知,直流损耗为0,在寄生电感与RX电容共同作用的储能振荡下,VTF损耗在0~8 GHz甚至更宽的频段内出现大于0的现象,为了避开前几个VTF损耗波谷,互连线长度需要被限制在15 mm以下。从图3(e)可知,当线距与线宽比为2.5时,蓝色曲线侵入mask区域,无法满足VTF串扰要求,这说明反射叠加进一步加重了串扰问题。在相同的驱动条件下,眼图的塌陷和抖动变得严重,眼宽仅为40.2 ps(0.64 UI),如图3(f)所示。

在UCIe中,先进封装方案要求的通道互连长度仅为2 mm,标准封装方案要求的通道互连长度为25 mm,该标准主要考虑到在先进工艺条件下,通道互连长度会受到50 Ω阻抗偏离和微小尺寸的寄生效应限制。在1.8 μm线宽工艺中,寄生电阻的量级达到了10 Ω/mm。从图3(g)可知,随着线长的增加,VTF损耗快速增大。在理想模型下,3 mm的通道互连长度已超出标准。同时,线宽变小同样会导致VTF损耗的增大,这成为先进封装方案中提升布线密度与保障传输质量之间的主要矛盾之一。先进封装方案未配置电阻性端接,较短的通道互连长度下信号反射的影响变小,薄介质层导致传输线与回流平面紧密耦合,线距小于等于2倍的线宽也可以满足VTF串扰的要求,线距对VTF串扰的影响如图3(h)所示。从图3(i)可知,在相同驱动下,线路的寄生电阻导致电平转换边沿塌陷严重,眼宽为45.9 ps(0.73 UI)。

基于相对理想的传输模型,针对UCIe中对不同封装方案和阻容配置的约束条件进行验证。结果表明,先进封装(无端接)和标准封装(无端接)方案能够实现更优的空间配置,而标准封装(有端接)方案在常规端接配置下最大限度地保留了通道性能完整性。在此基础上,以无锡中微高科电子有限公司的有机基板工艺为依托,对标准封装方案的布局进行设计,本团队进一步考虑了实际布线中过孔、焊盘、绕线等工艺结构对通道性能的具体影响,最终目标是为了达到UCIe的设计要求。

02

Chiplet标准封装方案设计与信号完整性仿真

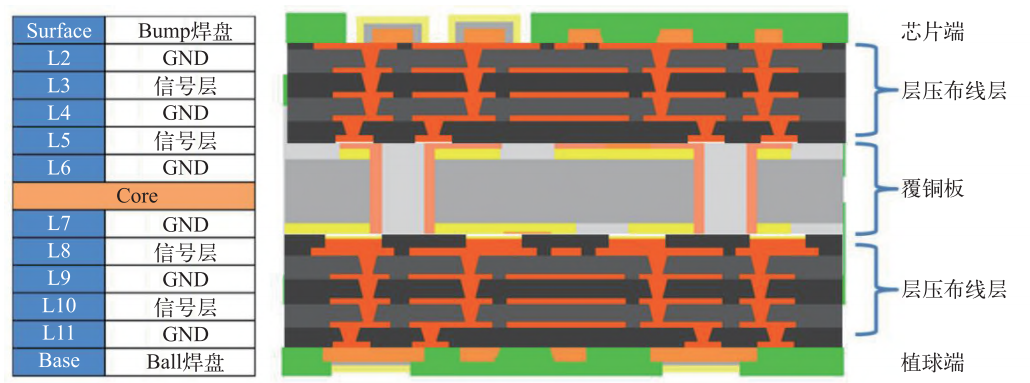

本文提出的高密度基板工艺是通过在覆铜板的两面实施电镀通孔铜柱、介质层压合、表面研磨、图形化布线的重复流程,实现多层布线。有机基板工艺的最小线宽/线距为20 μm/20 μm,在芯片倒装区域,线宽/线距可进一步缩小为15 μm/15 μm。高密度基板的层叠结构与高速信号层的分布如图4所示,在最高12层的布线结构下,为了确保高速信号的完整性,采用电源/地-信号-电源/地的带状线布局,将L3/L5/L8/L10层作为高速信号的布线层。

图4 高密度基板的层叠结构与高速信号层的分布

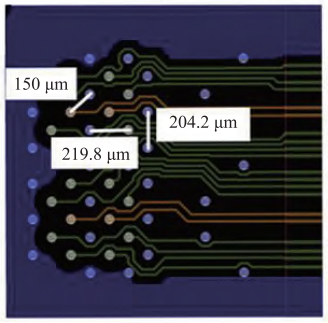

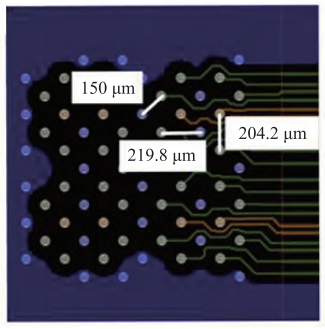

在UCIe中,理想的凸点节距是100~130 μm,以确保所需的互连带宽密度。制造商可以根据自身的实际工艺能力进行调整,联华电子股份有限公司采用了146 μm的凸点节距。本团队在有机基板设计过程中,遵循加工规范要求的节距(150 μm),根据UCIe要求的凸点布局方式,计算出垂直互连引线方向上单个TX/RX模块的边缘宽度为612.6 μm。若在单层上实现20个通道(含时钟、有效信号、跟踪信号)的布线,通道的平均宽度仅为30.6 μm,因此,在芯片的倒装区域实现合理的布线设计非常困难。采用双层布线通道的设计,通道的平均宽度增加为61.3 μm,有助于实现合理的布线设计。

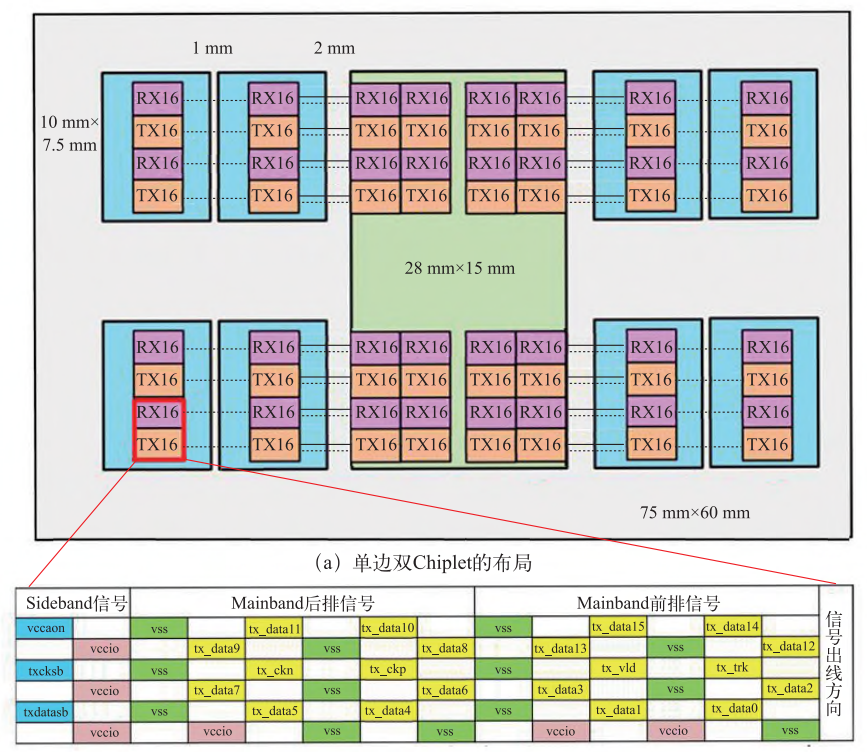

参照AMD公司IF技术的分布式架构设计,采用单边双Chiplet的布局,主Chiplet的尺寸为28 mm×15 mm,主Chiplet周围分布8个小Chiplet,每个尺寸为10 mm×7.5 mm。TX/RX接口被有序地排列在小Chiplet的中央区域和主Chiplet的长边边缘位置,这些接口通过4层走线实现了全通道的互连。将常规区域的线宽/线距设置为20 μm/40 μm,其中近端Chiplet的前、后排信号分别在L3、L5层进行布线设计,信号线长约为10 mm;远端Chiplet的前、后排信号分别在L8、L10层进行布线设计,信号线长约为25 mm。实际的互连密度为每毫米60个通道。在单通道数据传输速率为32 GT/s的条件下,每毫米的带宽达到了240 GB/s,该设计满足UCIe的带宽要求。Chiplet集成布局模型如图5所示。

(b)Chiplet的TX/RX接口布局

(c)单元后排引脚布线设计

(d)单元前排引脚布线设计

图5 Chiplet集成布局模型

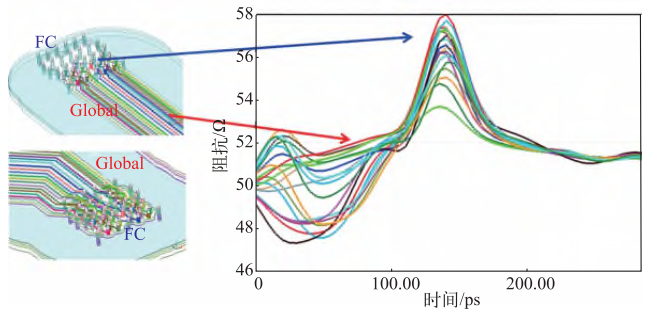

采用高频电磁仿真工具Ansys HFSS对互连模型中的无源通道进行模拟和分析。使用Ansys HFSS的时域反射阻抗(TDR)分析功能对常规走线(Global)区域的特性阻抗进行测量,走线区域的特征阻抗为50~52 Ω,其与预期设计相符。在Chiplet倒装区域,由于线宽变小并且通孔对应位置的回流平面被挖空,导致局部的特征阻抗偏高,基板互连的结构模型与TDR仿真曲线如图6所示。

图6 基板互连结构模型与TDR仿真曲线

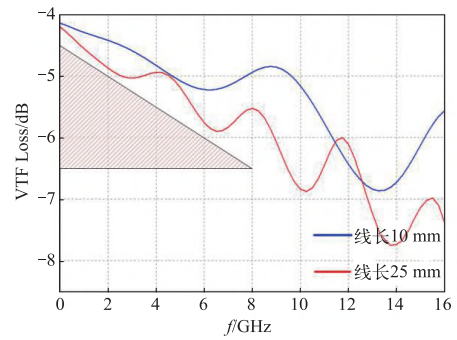

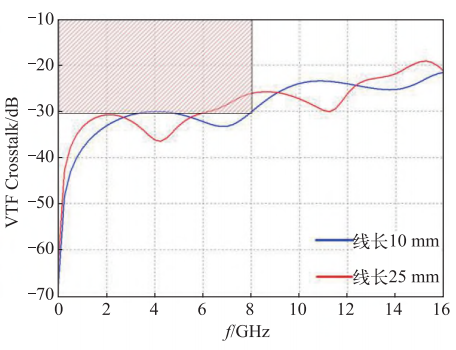

使用Ansys HFSS提取了S参数,将其转换为VTF。近端Chiplet(互连线长为10 mm)和远端Chiplet(互连线长为25 mm)的VTF损耗如图7(a)所示。当频率为8 GHz时,近端Chiplet的VTF损耗为-4.94 dB,远端Chiplet的VTF损耗为-5.56 dB,均符合UCIe要求。两者之间的差异主要来源于两端阻容负载产生的反射振荡。尽管倒装区域的局部阻抗有所突变,但其对整体性能的影响相对有限。近端Chiplet和远端Chiplet的VTF串扰如图7(b)所示,当频率为8 GHz时,近端Chiplet的VTF串扰为-30.16 dB,远端Chiplet的VTF串扰为-26.12 dB。产生串扰的主要原因为当参考地平面回流能力不足时,邻近信号之间的能量发生耦合。

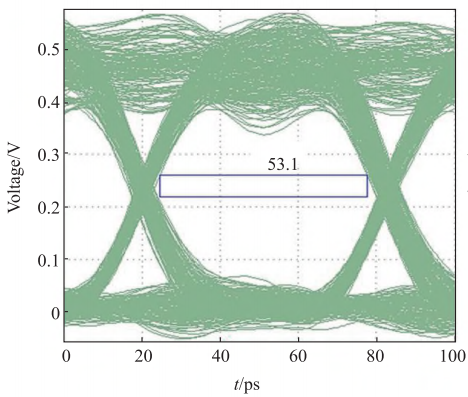

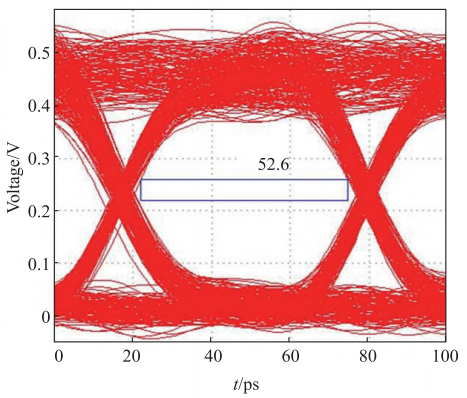

在长距离布线中,需要特别注意减小信号线之间的耦合强度,以降低潜在的串扰。得益于RX良好的端接匹配,两种长度的互连线在9 mA的TX驱动下都能得到良好的信号质量。图7(c)(d)为近端Chiplet和远端Chiplet的眼图,近端Chiplet的眼宽为53.1 ps(0.85 UI),远端Chiplet的眼宽为52.6 ps(0.84 UI),这说明线长差异导致的信号边沿退化及串扰对眼图抖动的影响有限。在缺少特定电源噪声模型的情况下,本文未针对基板的同步开关噪声进行建模或分析,但得益于有机基板的空间布局灵活性,信号通道在合理的端接配置下可以满足UCIe的设计要求,这一结果有望为Chiplet应用提供重要的设计和加工支持。

(a)近端Chiplet和远端Chiplet的VTF损耗

(b)近端Chiplet和远端Chiplet的VTF串扰

(c)近端Chiplet眼图

(d)远端Chiplet眼图

图7 Chiplet集成模型的VTF损耗和眼图

03

结 论

本文基于国内有机基板工艺,完成了Chiplet的标准封装布局设计,并对信号完整性进行了仿真分析。结果表明,该设计在单通道速率为32 GT/s的条件下,可实现每毫米240 GB/s的边缘带宽密度。同时,近端Chiplet和远端Chiplet的VTF损耗与VTF串扰及眼宽均满足UCIe的设计要求。本文对VTF指标的仿真方法进行了确认,并深入研究了国内有机基板在Chiplet应用方面的设计加工潜力,证明国内有机基板在Chiplet应用方面具有良好的前景,为推动Chiplet通用协议的国产应用转化提供了有价值的参考。有机基板的尺寸所导致的延迟和能效问题仍然是其相对短板,因此需要与上下游单位进行更深入的合作与探讨,以寻求解决方案。

-

听懂什么是信号完整性2024-12-15 1385

-

信号完整性与电源完整性-电源完整性分析2024-08-12 3275

-

信号完整性分析科普2023-08-17 9238

-

什么是信号完整性?2023-06-27 3604

-

什么是电源和信号完整性?2021-12-30 2111

-

信号完整性与电源完整性的仿真2021-09-29 1648

-

信号完整性系列之“信号完整性简介”2021-01-23 2599

-

信号完整性系列之信号完整性简介2021-01-20 2590

-

电地完整性、信号完整性分析导论2016-02-22 1357

-

信号完整性与电源完整性的仿真分析与设计2015-01-07 7034

-

信号完整性与电源完整性仿真分析2011-11-30 2109

-

信号完整性原理分析2009-11-04 1287

-

什么是信号完整性2009-06-30 5874

全部0条评论

快来发表一下你的评论吧 !