Delta-Sigma A/D转换器原理及其PSpice仿真

模拟技术

描述

近年来,因数字化产品对高分辨率A/D,D/A转换器需求的激增而得到广泛地应用。Delta-Sigma A/D转换器的构想出现已有很多年了,早期因受集成电路制造技术的限制,未在产品中广泛使用,随着集成电路制造成本不断降低,该技术的应用渐多,目前已成为高精度ADC的主流技术。随着该技术的趋热,有更多人想了解其工作原理,但目前国内的教材对其涉及还不多,期刊论文多侧重数学演绎,文献中未见有详尽的仿真实例。

除了制造专用ADC,该技术还易于用FPGA实现,逻辑电路可以完全集成在FPGA内部,只需要很少的外围元件,就可以用FPGA直接进行混合信号处理。由于FPGA可扩展和可重配置的特性,特别适合产品研发和小规模生产的场合,另外用FPGA在单一芯片上实现多路Sigma-Delta A /D转换也很容易。

Delta-Sigma有时称其为Sigma-Delta,或∑-△。

1 Delta-Sigma A/D转换器原理

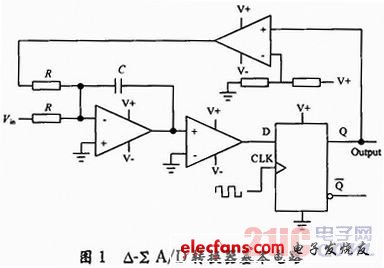

在△-∑A/D转换器中,模拟输入电压信号被连接到一个积分器的输入端。在输出端对应输入大小产生一个电压变化率,或者斜坡。然后用比较器将该斜坡电压与地电位(0V)进行比较。比较器的行为就像1位A/D转换器,根据积分器的输出是正或负产生1位的输出(“高”或“低”)。比较器的输出通过一个以很高频率时钟驱动的D触发器被锁存,并且反馈到积分器的另一个输入通道,向0V方向趋势驱动积分器。基本电路如图1所示。

在图1中,最左边的运放是积分器。积分器馈入的下一个运放是比较器,或1位A/D转换器。接下来是D触发器,在每个时钟脉冲锁存比较器的输出,发送“高”或“低”信号到电路顶部的下一个比较器。最后这个比较器用于转换信号极性,将触发器的0 V/5 V逻辑电平输出转换到V+/V-电压信号再反馈到积分器。

如果积分器输出是正,第一次比较器将输出一个“高”信号给触发器的D输入。在下一个时钟脉冲,“高”信号将从Q线输出到最后一个比较器的放大器输入。最上面的那个比较器将看见一个输入电压大于+1/2 V的阈值电压,它向正方向饱和,发送一个满V+信号到积分器的另一个输入端。这个V+反馈信号向负方向驱动积分器输出。如果输出电压一直为负,反馈环将发送一个矫正信号(V-)回到积分器的顶部输入,向正方向驱动它。这就是△-∑行为的概念:第一个比较器感知在积分器输出和0 V电压之间的差(△),积分器求模拟输入信号与最上面比较器输出的和(∑)。

2 PSpice仿真

通过PSpice仿真模拟实验,可以更容易和更清楚地理解△-∑A/D转换器的工作原理。下面采用PSpiee仿真△-∑A/D转换器。本文使用CaptLire CIS Lite Edition 9.2绘制电路图,用PSpice Lite Version 9.2进行仿真。

2.1 绘制电路图

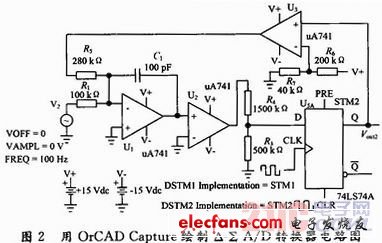

先用OrCAD Capture绘制△-∑A/D转换器电路图,如图2所示。信号源采用FREQ=100 kHz的正弦信号。偏移VOFF=0,幅度先设置为0 V,AMPL=0。

为方便起见图中所有的运算放大器都使用uA741模型,因为这个模型很容易找到,实际项目中根据需要选用合适的运放。D触发器使用74LS74。在CaptureCIS Lite Edition 9.2和PSpice Lite Version 9.2中没有74LS系列的元件符号库74ls.olb也没有仿真库74ls.lib,可以从下面的网站下载:

http://power.teipat. gr/download/OrCAD/OrCAD%20Libraries/Library%20for%20Capture/PSPICE/

74LS系列是低功耗肖特基型TTL器件,输入高电平最小为2.0 V,输入低电平最大为0.8 V;输出高电平最小位2.7 V,输出低电平最大为0.5 V。采用R3和R4分压将U2的输出电压转换为0~3.75 V电压,以适应TTL输入电平。74LS模型只接受正电压作为电平信号,所以可以不理会比较器U2的负电压输出。R6和R7分压15 V为2.5 V作为参考电压,将74LS74的TTL输出电平通过U3转换为V+/V-的电压信号。D触发器的时钟由DSTM1提供。从74LS74的产品手册可知,当LCR和PRE端都为高电平时,在时钟的上升沿,D触发器将输入端D的数据送到输出端Q,并锁存到下一个时钟的上升沿。这个高电平由DSTM2提供。图3是在Stimulus Editor中显示的STM1和STM2的波形,双击波形可以对它进行编辑。

2.2 输入信号电压幅度为0 V的情况

从功能上说,△-∑A/D转换器的转换结果是一个由触发器输出的串行比特流。如果模拟输入是0 V,积分器将不会有趋向正或负的斜坡,积分器只响应反馈电压。在这种情况下,触发器输出将持续在“高”和“低”之间震荡输出,反馈系统前后搜索,试图维持积分器输出在0 V。图4是∑-△转换器以0 V模拟输入运行的示意图,图中方波是D触发器输出,三角波是积分器输出的。

图5是∑-△转换器以0 V模拟输入运行的仿真图。

图5中,方波是D触发器输出的串行比特流,幅度较大的三角波是积分器的输出波形。仿真配置文件设置如图6所示。

2.3 输入信号电压幅度不为0 V的情况

如果施加一个小的负模拟输入电压,积分器将有一个向负方向倾斜它的输出的趋势。反馈只能以一个固定的电压(电源电压)在一定的时间内校正积分器的倾斜,这样触发器的比特流输出将和前面不完全相同。图7是∑-△转换器以小负模拟输入运行的示意图。

施加一个较大的负模拟输入信号到积分器,它的输出向正方向倾斜的更陡。这样,反馈系统将输出比以前更多的1,以带领积分器输出回到0 V。图8为∑-△转换器以较大负模拟输入运行的示意图。

用平均串行比特流的方法可以从该电路获得并行二进制数输出。例如,用一个计数电路搜集在一个给定时钟脉冲中触发器输出1的总数(正输入电压数输出0的总数),该计数器的值可以用来表示模拟输入电压。图9是∑-△转换器以5 V模拟输入运行的仿真图。

图中,正弦波是输入信号,方波是D触发器输出的串行比特流,三角波是积分器的输出波形。图10只显示输入信号和D触发器输出。

从图10中可以清楚地看到输入信号对输出脉冲宽度和频率的调制,输出是占空比随模拟输入电压大小变化的1,0位流。

3 PSpice仿真对不同电压幅度的输入信号积分器参数的调整

对不同幅度的输入信号,需要调制积分器的参数,以提高A/D转换的精度。图11是理想积分器及其输入/输出公式,其中RC是积分器的积分常数。

对应本文的电路R1、R5和C1决定积分器的时间常数,R1C1是输入信号的积分常数,R5C1是反馈信号的积分常数。改变电阻或电容值会改变转换精度。改变C1会同时改变输入信号和反馈信号的时间常数,当输入信号的幅值范围变化时通过改变R1来提高转换精度要好一些。通过对R1的参数扫描可以看出积分器时间常数对转换精度的影响。

通过参数扫描分析可知,电阻增加,减小了输入信号的强度,脉冲直接的间距减小,脉冲之中包含更少的“0”或“1”,说明转换精度降低。但是R1也不能太小,如果R1太小在对应输入信号幅值较高处会丢失一些脉冲,也就是丢失了数据。时间常数的选取要根据实际需求中输入信号波形的幅值范围进行反复仿真以获取最佳参数,并用实际电路测试来确定。

4 小信号输入的仿真例子

前面在说明∑-△转换器原理时输入信号电压幅值为5 V,实际应用中很多情况下输入信号是毫伏量级的,下面对幅值为0.05 V(50 mV)的正弦信号进行仿真。用参数仿真的方法确定R1=1.1kΩ。仿真结果如图12所示。

5 结语

∑-△A/D转换器具有非常高的分辨率,而且噪声很低,因为它采用了过采样的技术,因此对于前端的抗混叠滤波器的要求也大大降低,一般一个简单的RC低通滤波器就足够了。这类ADC的线性度也非常好,目前已成为实现高精度A/D转换的主要方式,但是它付出的代价是采样速率的降低。另外,由于内部滤波器对于模拟信号的突变和通道的切换需要相对长的建立时间,而且输出的数据与模拟输入之间有较长的延时,所以这类A/D转换器适用于那些模拟信号近似于直流或变化很慢的应用,如温度测量、压力测量等,近年来在音频领域也有应用。

- 相关推荐

- 热点推荐

- A/D转换器

- PSPICE

- Delta-Sigma

-

RZ MPU Delta-sigma的工作原理 Delta-Sigma的应用简介2024-03-22 5163

-

基于0.35μm工艺的Delta-Sigma ADC实现2010-04-24 2209

-

请问delta-sigma调制的FPGA实现原理是什么?2019-04-18 2635

-

LTC2420的典型应用,SO-8中的20位微功率无延迟Delta-Sigma ADC2019-08-21 2428

-

什么是Delta-Sigma转换器?ADS1232特点及应用是什么?2021-04-23 2690

-

Understanding Delta-Sigma Data Converters, 2nd Edition 中文翻译出版2021-07-30 3790

-

delta-sigma调制过后的高频噪声是怎么去掉的?2023-05-06 2490

-

基于0.35μm工艺的Delta-Sigma ADC实现2010-02-11 718

-

Delta-Sigma模数转换器的优点2010-07-01 4302

-

Delta-Sigma转换器的原理和应用2011-02-03 9525

-

高精度Delta-Sigma A/D转换器原理及其应用2012-01-13 1131

-

Delta-Sigma AD转换器的详细资料介绍2020-03-21 1691

-

Delta-Sigma转换器和ADS1232芯片的工作原理和应用分析2020-08-14 7841

-

AN-406:使用AD771X系列24位Sigma-Delta A/D转换器2021-05-07 1004

-

AN-365:AD7712 24位Sigma-Delta A/D转换器评估板2021-05-10 956

全部0条评论

快来发表一下你的评论吧 !