以太网自协商机制-双绞线自协商案例设计(二)

描述

FLP Burst内容编码—BasePage

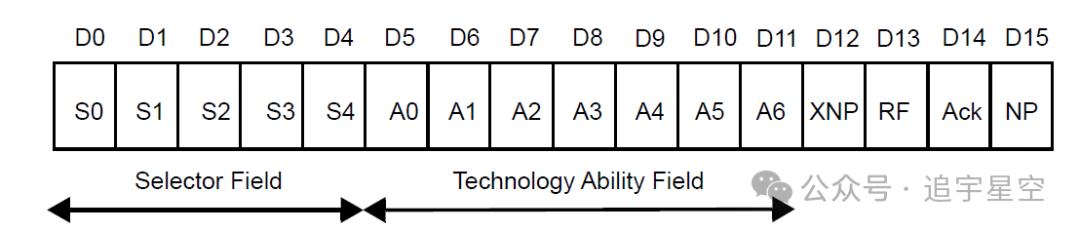

BasePage的编码格式如下图:

在FLP突发中,D0应是传输的第一个比特。编码释义如下: Selector Field

[S4:S0]=2b00001(表示基于IEEE802.3以太网的自协商);

Technology Ability Field

[A0] 10BASE-T半双工;

[A1] 10BASE-T全双工;

[A2] 100BASE-TX半双工;

[A3] 100BASE-TX全双工;

[A4] 100BASE-T4半双工;

[A5:A6] =2b00(表示无流控),

=2b01(表示指向对端的非对称流控),

=2b10(表示对称流控),

=2b11(表示对称流控和指向本端的非对称流控);

Extended Next Page

[XNP] =2b0 紧接BasePage的下一页为NextPage,

=2b1 紧接BasePage的下一页为ExtendedNextPage;

Remote Fault

[RF] =2b0 自协商无错误,

=2b1 自协商有错误;

Acknowledge

[Ack] =2b0尚未收到来自远端的BasePage,

=2b1 已收到来自远端的BasePage;

Next Page

[NP] =2b0当前BasePage页已是最后页,

=2b1 当前BasePage页不是最后页;

BasePage的应用实践

FLP Burst-BasePage交互应用于IEEE Clause 28双绞线自协商的所有类型(10M/100M)、(10M/100M/1000M)和(10M/100M/1000M/2.5G/5G/ 10G/25G/40G)。而其中10M/100M自协商仅使用BasePage交互即可,10M/ 100M/1000M和10M/100M/1000M/2.G/5G/10G/25G/40G需要其他类型Page (NextPage和ExtendedNextPage)[在后续章节会陆续进行详细介绍]。

笔者以曾经实践过的Marvell公司的88e6097F Switch芯片中集成的百兆PHY举例[与自协商相关的寄存器属于IEEE802.3标准寄存器,故不同厂家不同型号的PHY该部分实现大同小异],与10M/100M自协商相关的3个寄存器内容分别如下:

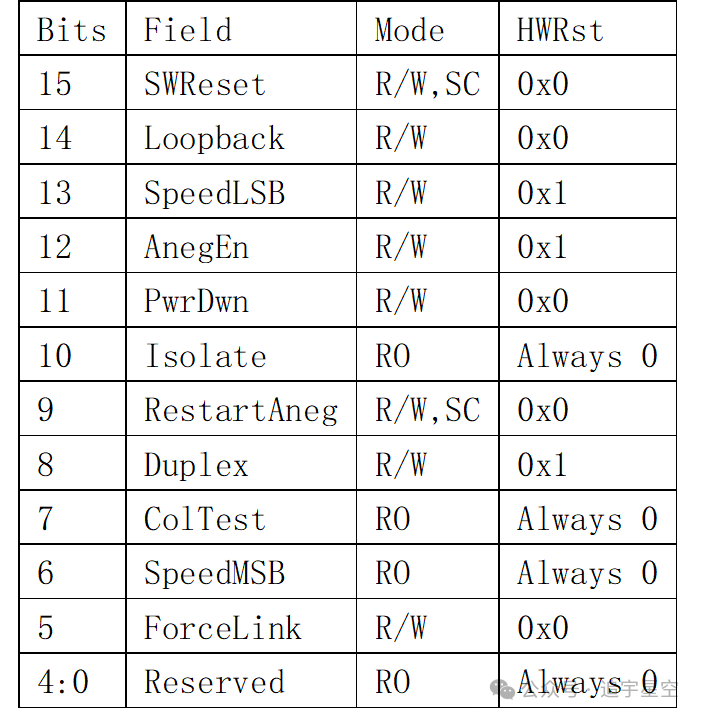

PHY Control Register Register 0

在该寄存器中与自协商相关bit分别为:

bit12 AnegEn 该bit为自协商使能位(配置工程师需要保证双绞线两端的自协商使能位保持一致。如果一端自协商使能另一端自协商关闭,自协商使能这端会触发并行检测状态机,可能会造成链路双方的双工状态的不一致);

bit9 RestartAneg 该bit为重新自协商使能位,当本端自协商的广告能力位有变化或者未能协商选择链路双方彼此最高阶的广告能力(如EMC等强电磁辐射造成的FLP Busrt信号畸变)时,需要软件操作此bit设置1以重启自协商进程;

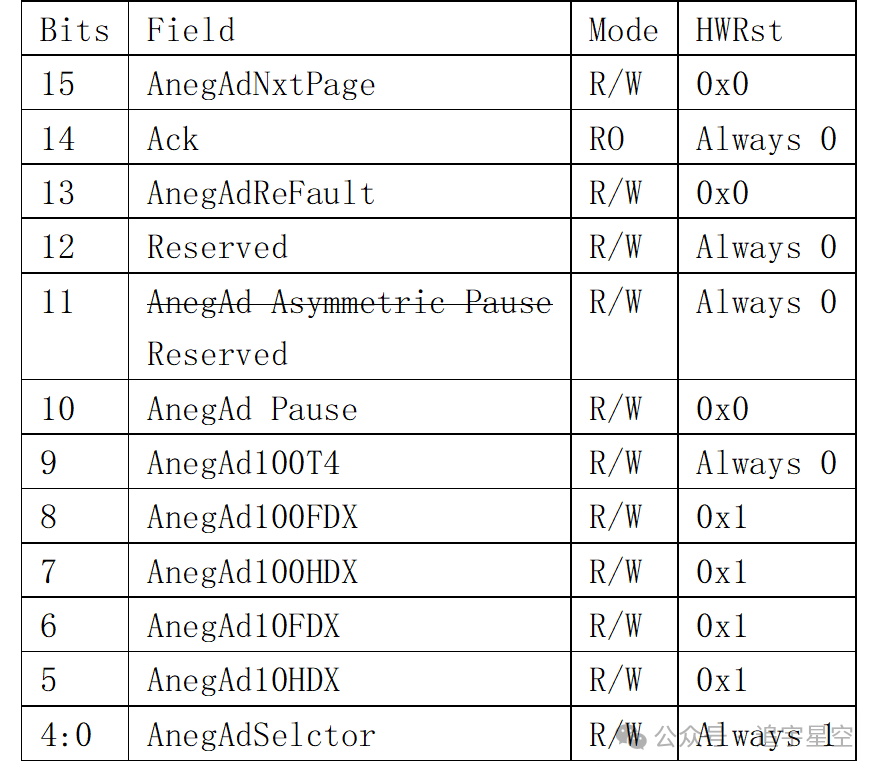

Auto-Negotiation Advertisement Register Register4

该本地广告能力寄存器是10M/100M自协商的核心寄存器,现逐bit解释:

bit15 AnegAdNxtPage 该bit为FLPBurst-BasePage的D15.NP,因为10M/100M自协商只使用BasePage,故此bit永远为0;

bit14 Ack 该bit为FLPBurst-BasePage的D14.Ack,该bit由PHY芯片自协商状态机自动维护,软件无需设置此bit;

bit13 AnegAdReFault 该bit为FLPBurst-BasePage的D13.RF,软件周期需要读PHYStatus RegisterRegister 1的bit4 RemoteFault的状态值,然后同步设置到此bit;

bit12 Reserved 该bit为FLPBurst-BasePage的D12.XNP,因为10M/100M自协商只使用BasePage,故此bit永远为0;

bit11 AnegAd Asymmetric Pause 该bit为FLPBurst-BasePage的D11.A6,但10M/100MPHY通常不支持非对称流控,故此bit为Reserved,永远为0;

bit10 AnegAd Pause 该bit为FLPBurst-BasePage的D10.A5,该bit根据网络管理员的实际应用需求灵活设置(置1有此能力,置0无此能力);

bit9 AnegAd 100T4 该bit为FLPBurst-BasePage的D9.A4,因为100Base-T4该物理层标准已经被淘汰,故该bit永远为0;

bit8 AnegAd100FDX 该bit为FLPBurst-BasePage的D8.A3,该bit为100Base-TX全双工能力,根据网络管理员的实际应用需求灵活设置(置1有此能力,置0无此能力);

bit7 AnegAd100HDX 该bit为FLPBurst-BasePage的D7.A2,该bit为100Base-TX半双工能力,根据网络管理员的实际应用需求灵活设置(置1有此能力,置0无此能力);

bit6 AnegAd10FDX 该bit为FLPBurst-BasePage的D6.A1,该bit为10Base-T全双工能力,根据网络管理员的实际应用需求灵活设置(置1有此能力,置0无此能力);

bit5 AnegAd10HDX 该bit为FLPBurst-BasePage的D5.A0,该bit为10Base-T半双工能力,根据网络管理员的实际应用需求灵活设置(置1有此能力,置0无此能力);

bit[4:0] Selector Field 该bits为FLPBurst-BasePage的D4:D0.[S4:S0],该bits永远为1,表示该自协商为基于IEEE802.3以太网的自协商(比如该bits为0x4表示基于IEEE1394的自协商,该bits为0x5表示为基于INCITS的T10 SCSI、T11FC、T13 SATA的自协商);

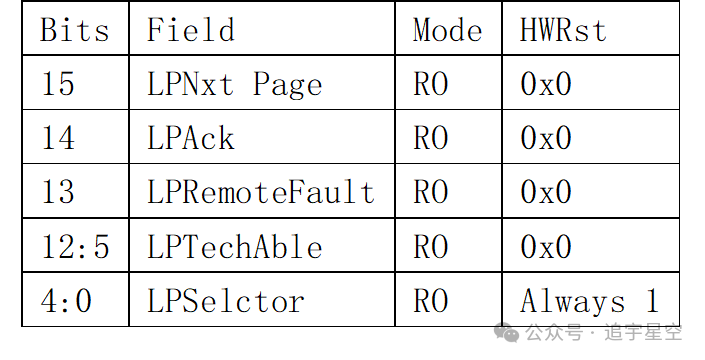

Link Partner Ability Register (Base Page)Register 5

该邻居广告能力状态寄存器是将远端发送的FLPBurst-BasePage的信息存储在本寄存器。如果自协商协商失败从而链路双方不能正常建立链接,相关驱动工程师可以利用本寄存器进行故障定位和分析。本寄存器bit定义与“Auto-Negotiation AdvertisementRegister Register 4”完全相同,故这里就不再赘述了。

10M/100M自协商基理

10M/100M自协商,主要协商的内容为“速度双工”和“流控”两大类,下面就这两大类内容进行阐述。

速度双工协商

速度双工主要靠设置“本地广告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5实现的。本端和远端选择彼此都有的能力(bit9:5中的置1的相关bit)中优先级高的那种能力作为本端PHY和远端PHY的实际工作的速度双工状态。

PHY能力优先级由高到低排序如下:

100BASE-T2full duplex[需使用NextPage,实际是没有芯片支持此能力]

100BASE-TX full duplex

100BASE-T2[需使用NextPage,实际是没有芯片支持此能力]

100BASE-T4[实际是没有芯片支持此能力]

100BASE-TX half duplex

10BASE-T full duplex

10BASE-T half duplex

例子1:本端PHY的“本地广告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b01111;双绞线另一侧的远端PHY的“本地广告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b00101。此时他俩的彼此能力的交集为bit9:5=2b00101,即双绞线链路双方都支持的PHY能力为bit5=1(10BASE-T half duplex)和bit7=1(100BASE-T half duplex),并且因为优先级顺序为100BASE-T half duplex>10BASE-T half duplex,故此时本端和远端速度双工自协商的结果为“100BASE-T half duplex”;

例子2:本端PHY的“本地广告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b01110;双绞线另一侧的远端PHY的“本地广告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b00110。此时他俩的彼此能力的交集为bit9:5=2b00110,即双绞线链路双方都支持PHY能力为bit6=1(10BASE-T full duplex)和bit7=1(100BASE-T half duplex),并且因为优先级顺序为100BASE-T half duplex>10BASE-T full duplex,故此时本端和远端速度双工自协商的结果为“100BASE-T half duplex”;

例子3:本端PHY的“本地广告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b01010;双绞线另一侧的远端PHY的“本地广告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit9:5=2b00101。此时他俩的彼此能力的交集为bit9:5=2b00000,即双绞线链路双方没有PHY能力交集,故此时本端和远端永远无法建立正确链接。

写到这里,可能有小伙伴感觉到疑惑,既然88e6097F PHY默认支持bit9:5=2b01111,为什么还有将部分PHY能力主动设置为0的需求。讲到这里我们必须有一个基本的认知就是:10Base-T全双工的可靠性和链路冗余度是远远强于100Base-TX全双工的(通常cat5e的网线在100Base-TX时支持160米左右的无损传输,而cat5e的网线在10Base-T时支持210米左右的无损传输;同样的辐射抗扰度RS的干扰下10Base-T的丢包率也远小于100Base-TX)。如果应用层的实际单宽需求小于10Mbps,此时远端第三方设备bit9:5=2b01111(可能无用户侧配置接口)的场景下,本端可以主动设置bit9:5=2b00011,以保证本端远端最终协商于10Base-T全双工模式。

流控协商

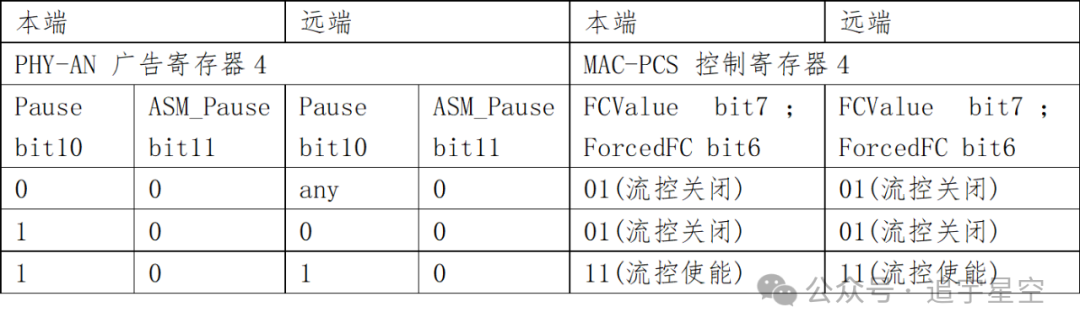

流控主要靠设置“本地广告能力寄存器Auto-Negotiation Advertisement Register Register 4”的bit11:10实现的。软件通过本端和远端的bit11:10的各种组合进行对本端MAC的tx和rx方向的802.3流控进行设置,因为10/100M PHY不支持非对称流控,故bit11永远为0,具体规则如下表:

MAC-PCS控制寄存器需要软件根据“PHY-AN广告寄存器”和“PHY-AN LP广告状态寄存器”的内容进行动态更新配置,交换芯片硬件并不会自动联动。

流控设置之所以有上表的规则要求,是需要保证双绞线链路双方的流控状态一致。如果出现一端流控使能,一端流控关闭,在链路拥塞时不但不能享受流控的优点,反而会引起链路中出现大量Pause流控帧使已经拥塞的链路更加拥塞。

审核编辑:刘清

-

以太网自协商机制—双绞线自协商案例(四)2024-03-20 6090

-

以太网自协商机制-双绞线自协商案例设计(三)2024-03-18 3123

-

基于IEEE Clause 28双绞线的以太网自协商机制2024-03-15 1579

-

一文解析以太网自动协商技术2024-02-22 7404

-

基于DP83822I工业以太网PHY自协商功能与其Strap电阻配置2022-11-11 722

-

以太网网口自协商功能现象2021-12-29 12602

-

10G/25G以太网IP自协商调试方案2020-11-03 7193

-

如何调试10G/25G以太网IP自协商/Link Training2020-09-03 11243

-

为什么以太网+柔性板与电脑无法协商为100M?2019-09-11 2320

-

DP83822I工业以太网PHY自协商功能与其Strap电阻配置2019-03-14 3216

-

基于语义网技术的SLA协商机制2018-01-02 918

-

FPGA光纤以太网自协商的设计2011-03-26 915

全部0条评论

快来发表一下你的评论吧 !