什么是BCD工艺?BCD工艺与CMOS工艺对比

制造/封装

描述

原文作者:Tom

本文简单介绍了BCD工艺的概念,并比较BCD工艺与CMOS工艺。

在功率芯片中,常会用到BCD工艺。BCD工艺是CMOS工艺的变种,是基于CMOS工艺的一种特色工艺。 什么是BCD工艺?

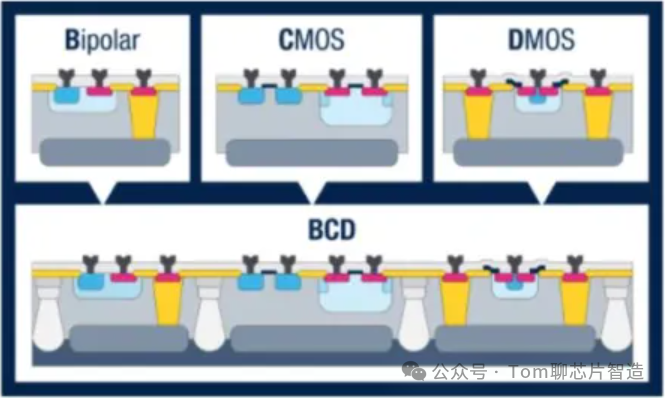

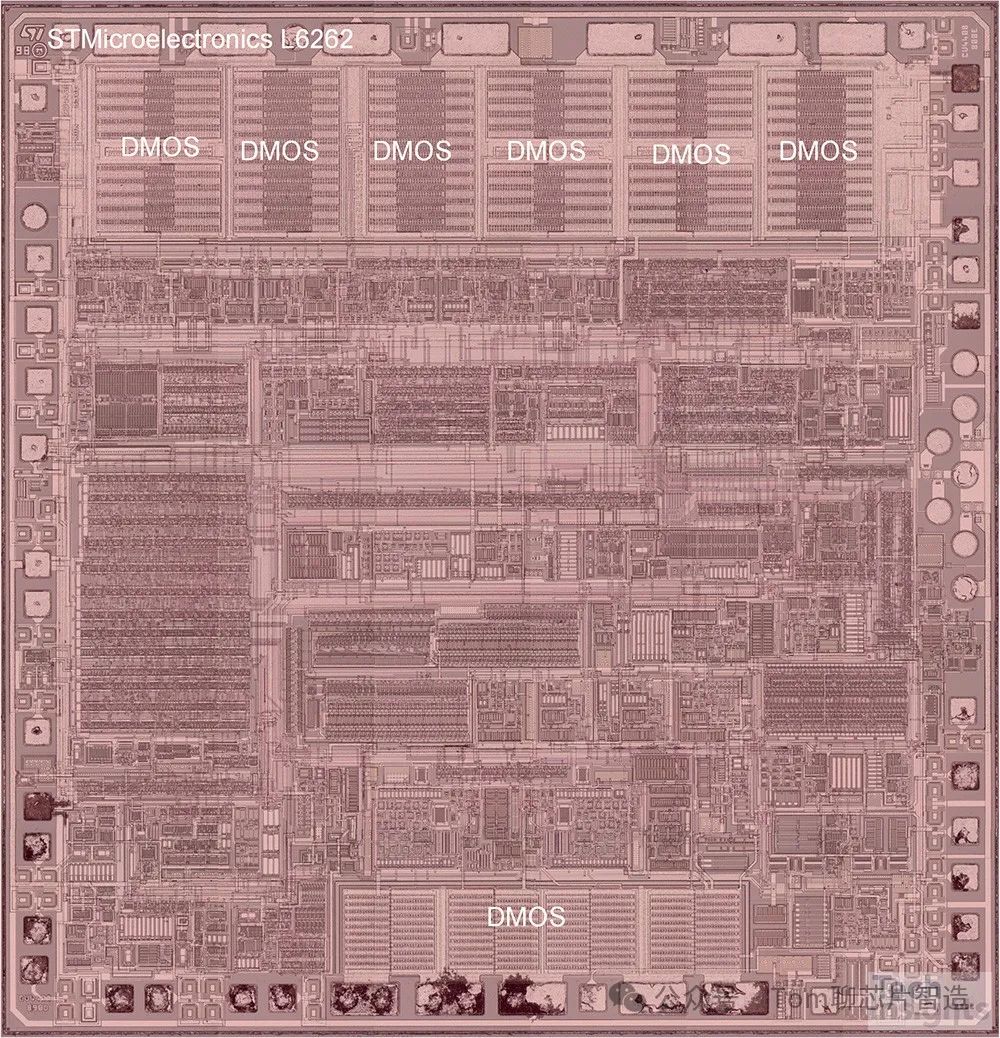

BCD(Bipolar-CMOS-DMOS)工艺技术是将双极型晶体管、CMOS(互补金属氧化物半导体)和DMOS(双扩散金属氧化物半导体)晶体管技术组合在单个芯片上的高级制造工艺。双极型晶体管主要用于模拟信号控制,而CMOS 和 DMOS则用于数字信号控制和高功率的处理。

什么是双极型工艺?

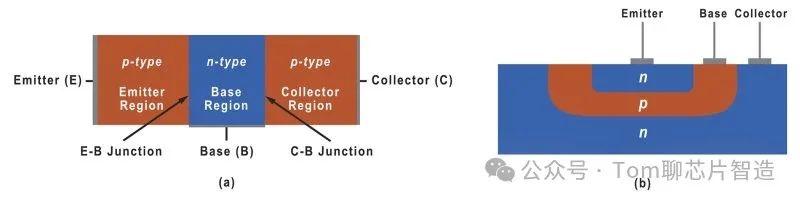

双极型工艺是最早出现的IC工艺制程技术,它的基本结构按照P型和N型半导体的不同排列顺序,可以分为两种类型:NPN和PNP。以NPN为例,由一个P型半导体夹在两个N型半导体之间构成,电流从集电极(Collector)流向发射极(Emitter),当基极(Base)和发射极之间施加正向偏置电压时,可以控制集电极和发射极之间的电流大小。

什么是DMOS工艺制程?

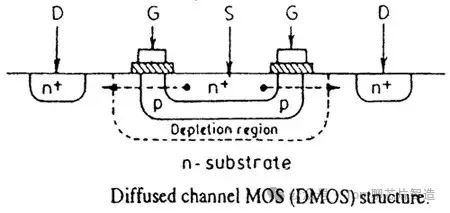

DMOS全称为Double-Diffused MOS,即双扩散金属氧化物半导体。DMOS之所以被称为“双扩散”,是因为其制造过程中有到两次掺杂扩散步骤,这两次扩散分别用于形成晶体管的不同区域:第一次扩散在硅基底上形成沟道区,第二次扩散在沟道区形成源极和漏极。DMOS又包含Vertical DMOS(垂直DMOS),Lateral DMOS(水平DMOS)等。 以N型Lateral DMOS为例,见下图:

漏极(Drain, D):位于晶体管一端的N+区域,用于收集从源极流出的电子。 源极(Source, S):位于另一端的N+区域,电子从该处进入晶体管。 栅极(Gate, G):位于源极和漏极之间的P区域上方,通过氧化物层与沟道隔离。栅极控制在P区域下方N型沟道区域中电子的流动。 沟道:栅极下方,当栅极施加足够的正向电压时,会在P区和N型衬底之间形成N型沟道,允许电子流动。 N型衬底(n-substrate):选用的是n型硅片基材。 耗尽区(Depletion region):当栅极未施加电压时,源极和漏极之间N+区与P区交界处形成耗尽区。耗尽区宽度随栅极电压的增加而减小,从而允许电子从源极通过沟道流向漏极。

BCD工艺相对于CMOS工艺的优点?

1,提高了芯片可靠性:将三种工艺集成在单个芯片上减少了组件数量,从而降低了连接失败的故障率。而且有助于更有效地散热,减少因温度过高而导致的可靠性问题。

2,减少电磁干扰:内部互连长度减小,降低了寄生电感,从而减少了高频开关时产生的电磁干扰。

3,更小的芯片面积。

审核编辑:黄飞

-

电动汽车时代,BCD工艺成为关键2025-07-05 10026

-

HV-CMOS工艺制程技术简介2024-07-22 7653

-

BCD工艺制程技术简介2024-07-19 8327

-

BCD工艺凭什么成为主流?2023-10-31 3719

-

锐成芯微推出基于BCD工艺的三层光罩eFlash IP2023-03-03 1644

-

请教各位大佬BCD工艺和mixsignal工艺的区别在什么地方?2021-06-25 5968

-

请问哪位大侠有umc0.25um bcd工艺?2021-06-22 2694

-

华虹半导体12英寸90纳米BCD工艺实现规模量产2021-06-04 7795

-

什么是BCD工艺?2020-11-27 25324

-

COMS工艺制程技术与集成电路设计指南2019-03-15 6670

-

CMOS工艺制程技术的详细资料说明2019-01-08 2549

-

华润上华第三代超高压700V BCD系列工艺开发成功2013-05-16 3696

-

BCD工艺介绍2012-03-26 95143

-

基于0.5μm BCD工艺的欠压锁存电路设计2009-11-26 2844

全部0条评论

快来发表一下你的评论吧 !