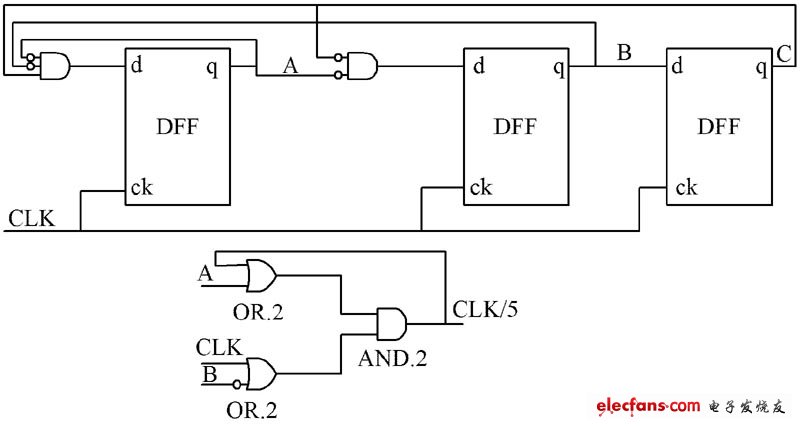

D触发器结构的五分频器逻辑电路

数字电路图

134人已加入

描述

D触发器结构的五分频器逻辑电路由3 个D 触发器和少量逻辑门构成, 采用了同步工作模式, 其原理是由吞脉冲计数原理产生2 个占空比不同的五分频信号A 和B, 然后对时钟信号CLK, A 和B 进行逻辑运算得到占空比为50% 的五分频信号CLK/ 5, 其计数过程如表1 所示, 从表1 的计数过程可知, 分频后的时钟CLK/ 5 的周期是输入时钟CLK 的5 倍, 由此实现了五分频并且其占空比为50% .

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

用CD4013双D触发器做的脉冲4分频器资料推荐2021-05-13 2084

-

D触发器怎么实现二分频电路?2020-03-02 6778

-

请问D触发器结构的五分频器逻辑电路怎么实现?2019-09-11 4149

-

基于65nm工艺的五分频器设计方案2018-04-18 10889

-

d触发器四分频电路2017-11-02 115722

-

如何用D触发器实现2分频 原理2016-07-03 9744

-

D触发器组成的_2N_1_2分频电路2012-05-23 3890

-

D触发器组成分频器和计数器电路图2010-09-20 13722

-

d触发器构成2分频电路2009-06-22 9077

-

D触发器实现二分频电路(D触发器构成的2分频电路)2009-06-12 81658

-

十分频器电路图2009-03-29 8355

-

供数字时钟使用的+5000分频器电路2009-01-13 2398

-

D触发器2008-10-20 3228

-

cd4013双d触发器电路图2008-01-09 5980

全部0条评论

快来发表一下你的评论吧 !