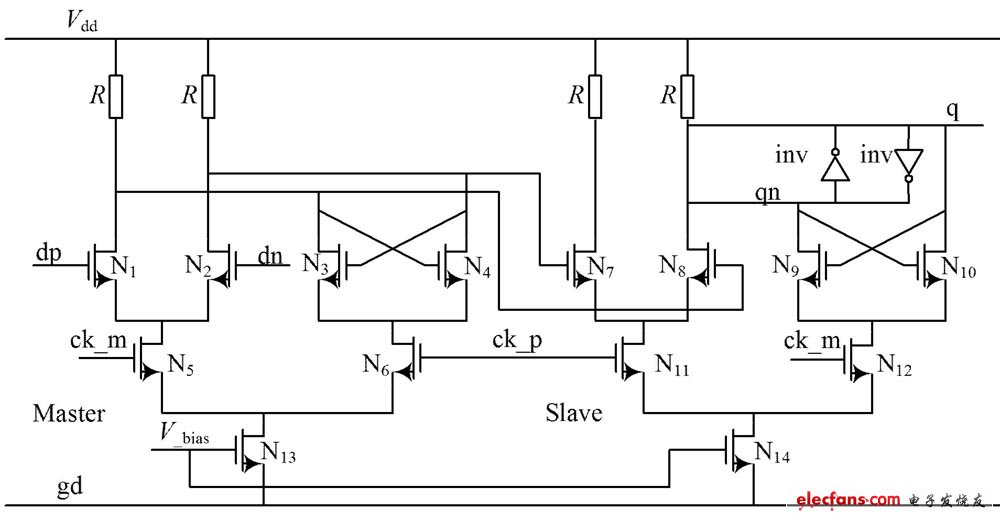

CML锁存器构成的主从式触发器电路

数字电路图

134人已加入

描述

该触发器由2 个CML 结构锁存器组成, 它们构成主从型结构, 每个锁存器都要经过2 个阶段: 跟踪阶段和保持阶段。当主锁存器跟踪输入信号时, 从锁存器处于锁存保持阶段, 然后交替。其中N13 , N14 为尾电流管, 偏置电压V_bias 使N13 , N14管工作在饱和状态, 充当恒流源的作用。dp 和dn 是由输入信号d 经传输门和反相器产生的一对互补差分信号, ck_m 和ck_p 是由输入时钟信号clk 经传输门和反相器产生的一对互补时钟差分信号。主锁存器工作状态为: 当ck_m 为高电平时, N5 管导通, N6 管关闭, 此时N1 , N2 管工作在差分状态, 将输入信号dp, dn 采入。当ck_p 为高电平时,N6 管导通, N5 管关闭, 此时N3 , N4 使电路维持在锁存状态, 从锁存器工作状态恰好与主锁存器工作状态相反。设计中在触发器输出端q, qn 之间加了2 个反相器从而在q, qn 之间形成正反馈, 增强了电路的输出驱动能力。工作时, 电路的尾电流应当足够大, 有利于提高电路工作频率和输出信号的摆幅。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

评论(0)

发评论

-

游客 2011-11-25

0 回复 举报技术交流、我要发言 收起回复

-

锁存器、触发器、寄存器和缓冲器的区别2011-10-09 9566

-

凔海笔记之FPGA(六):触发器和锁存器2016-05-21 4451

-

寄存器、锁存器和触发器的区别2018-07-03 4104

-

触发器、锁存器、寄存器三者的区别2018-09-11 6279

-

【转】数字电路三剑客:锁存器、触发器和寄存器2018-10-27 2838

-

锁存器与触发器的工作原理是什么2021-11-03 4848

-

锁存器和触发器2022-03-10 9576

-

锁存器和触发器原理2010-08-18 2075

-

主从触发器,主从触发器的原理和特点有哪些?2010-03-08 12427

-

触发器的分类, 触发器的电路2010-03-09 1915

-

锁存器与触发器的区别2020-11-29 26672

-

锁存器、触发器、寄存器的关联与区别及其相应的verilog描述2022-12-19 15162

-

触发器和锁存器的区别和联系2023-12-25 3047

-

锁存器电路通过什么触发的2024-07-23 1650

-

主从触发器是一种能防止什么现象的触发器2024-08-11 2108

全部0条评论

快来发表一下你的评论吧 !