OV426硬件设计方案-CCU(相机控制单元)

描述

使用OVM6946和OV426设计内窥镜吧!

决战1mm,OVM6946内窥FPGA方案开源

这篇来写硬件分析,这篇文章是个大的杂合体,如果有什么不对的地方请指教。

主要是我没有大哥FPGA的功力,我只能用现成的转换方案了。

但是所有的方案都是流式处理,对于图像处理来说,永远都是等着前一级的处理完才能干活。

所以都是:桥接处理器(同步输出),数字信号将被图像信号处理器(ISP)处理,最后输出图像数据。

其中中低端的内窥镜用图像传感器,主要是以OV的为主:

有OV6946+OV426、OV6948+OV426、OV9734、OH02A1S(带近红外增强)、OH0TA10+普通ADC(这颗料据说是业界最小,400×400相素,封装尺寸只有550μm*550μm)、DH01A10。

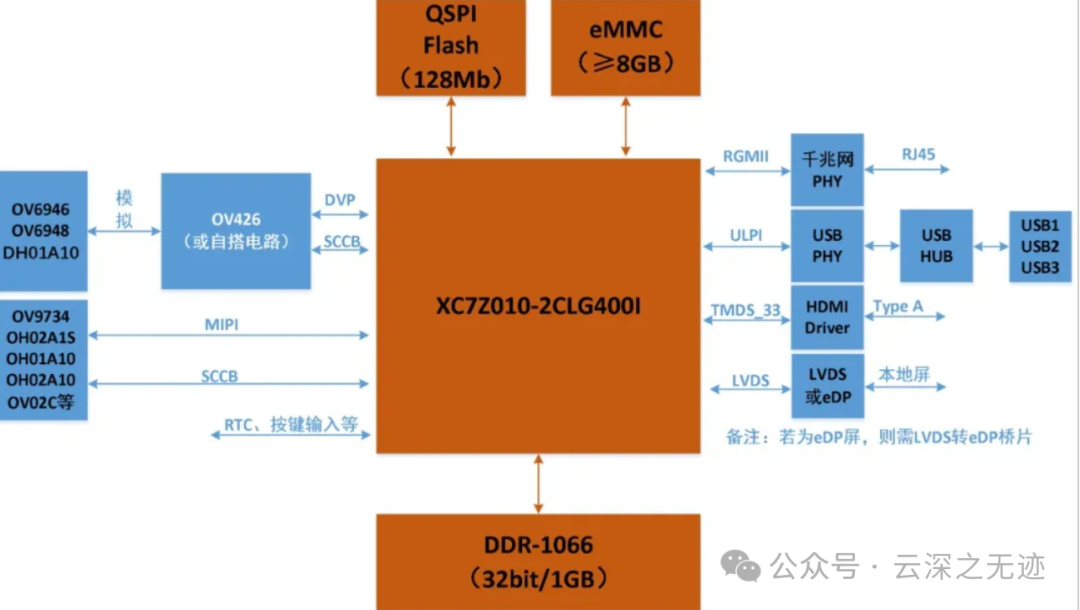

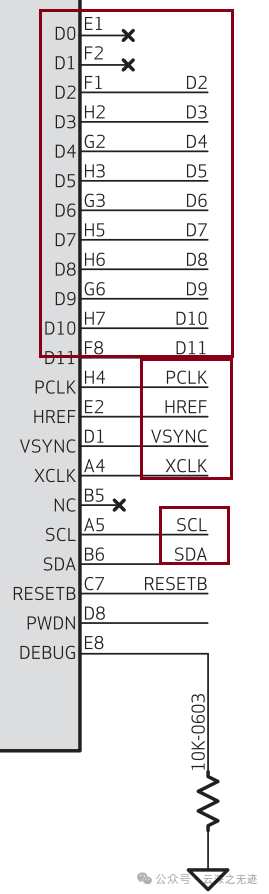

来自ZYNQ的一张图,这里就看DVP和SCCB的接口

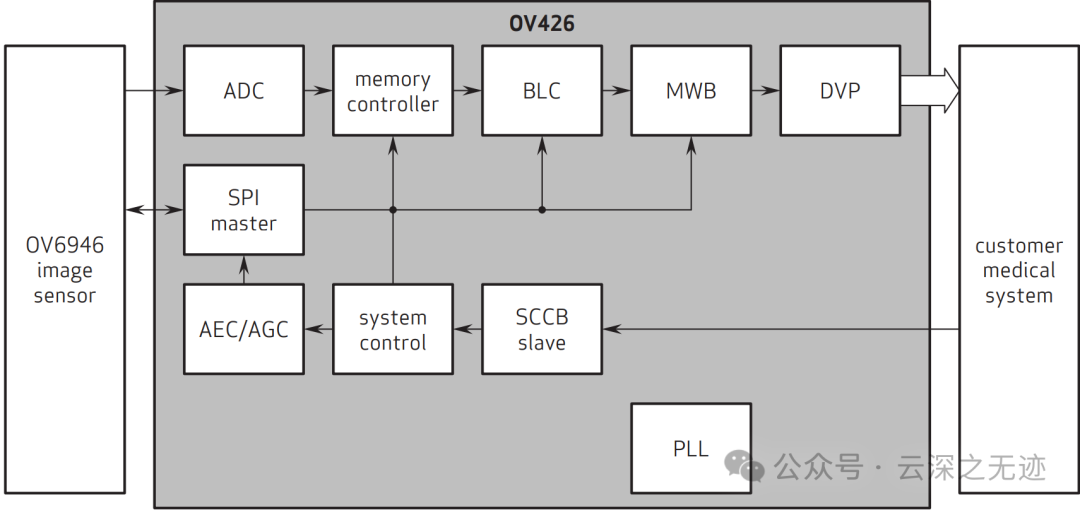

接口是4个,ADC+SPI是相机侧的,IIC+DVP并口是输出侧的

稳妥

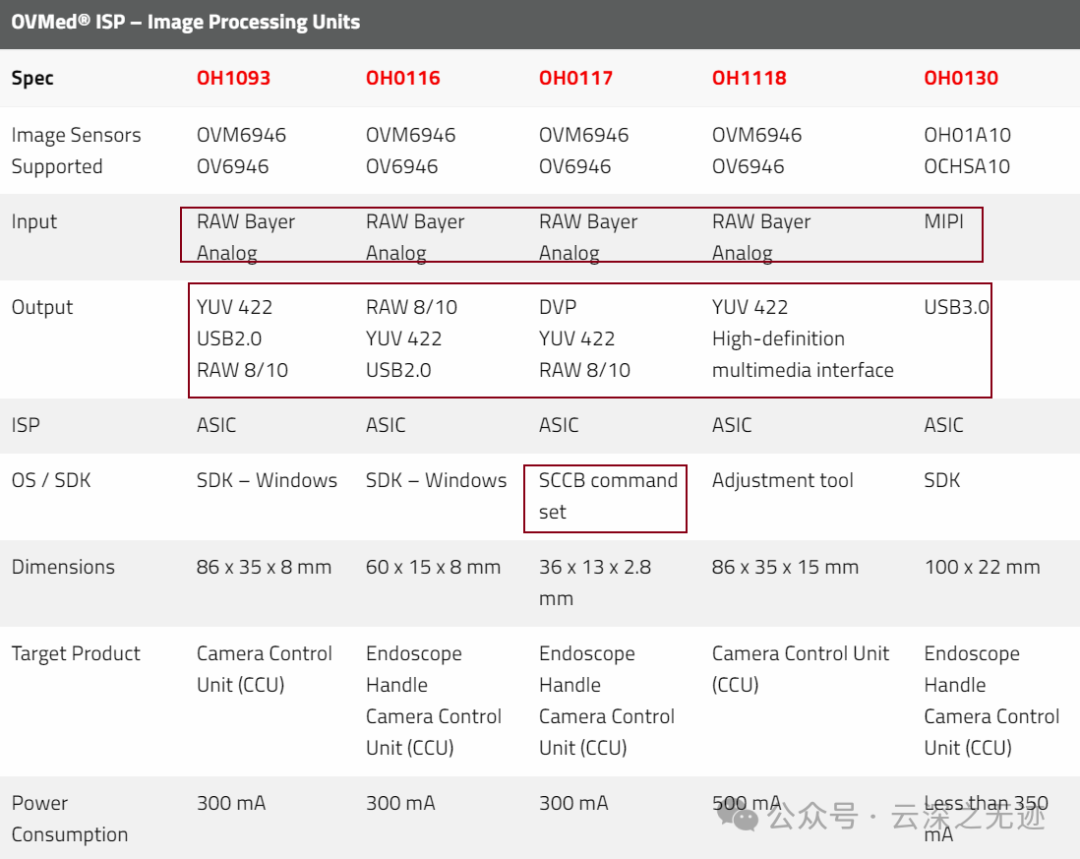

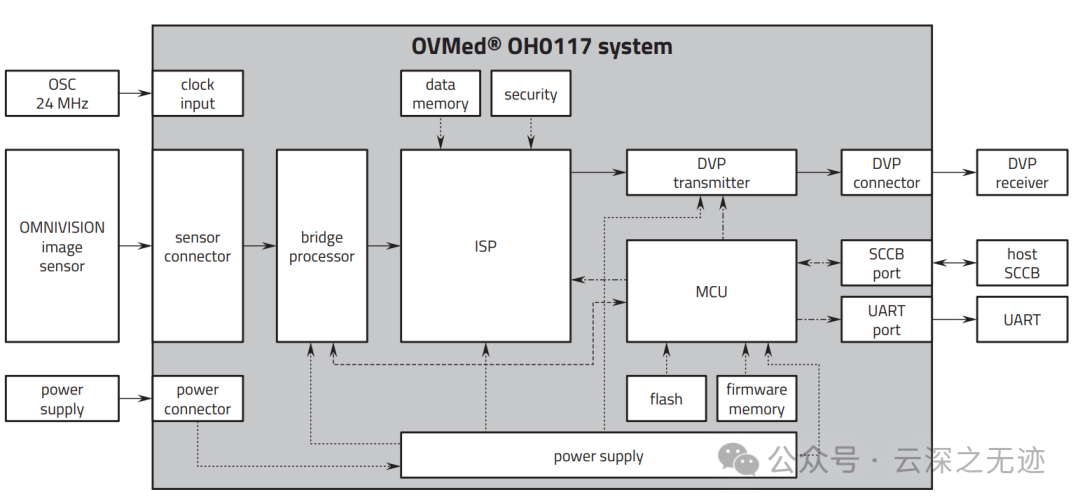

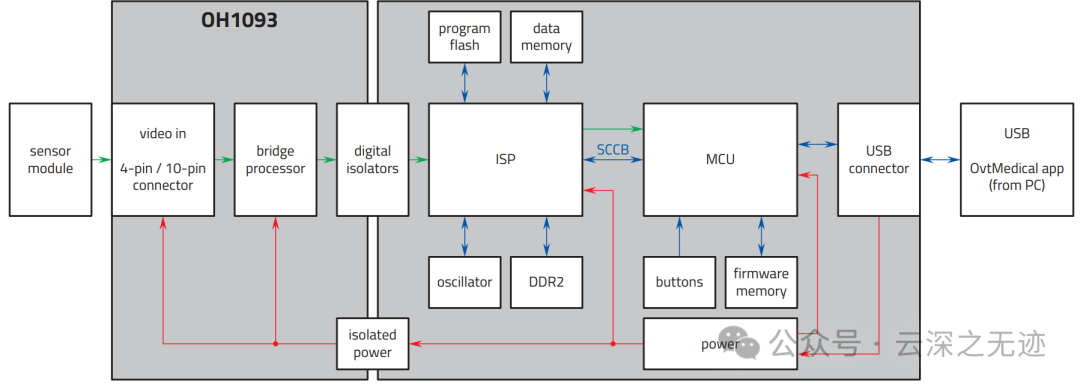

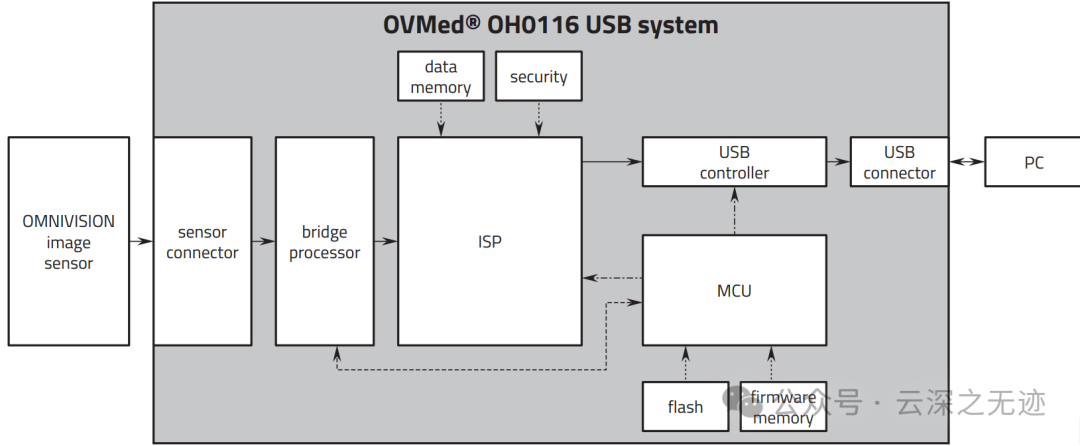

另外OV其实也是给了一系列的现成的解决方案:

五款

这个是处理完又是DVP输出去了,命令可以使用串口来控制

这个一看就很重型,直接USB输出

这个是追求实时性,没有过多的缓存

这个是注重外设控制

有时候是好几个摄像头仪器拍摄,各个系统之间进行同步曝光:

同步曝光:关于 FSIN 引脚用于同步曝光的功能,可以通过外部信号来同步多个摄像头的曝光时间,确保它们捕获图像的时刻是一致的。要实现这一点需要在设计中额外添加对 FSIN 信号的支持,以确保能够正确地控制和同步曝光。 内部时钟:由于每个图像传感器的时钟是自由运行的,同步曝光仅同步它们的曝光起点,而不会同步内部时钟或其他电路。这意味着即使曝光是同步的,传感器间的像素数据输出可能仍存在微小的时差,这通常可以通过后续的软件处理来校正。

以上系统延迟范围为100ms到160ms,我不知道真的假的。

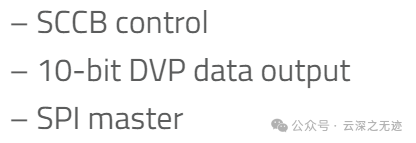

说回OV426,DVP是需要很多的引脚,DVP接口使用的是LVDS(Low Voltage Differential Signaling)电气接口标准,通常需要使用更多的电源和地线来支持高速数据传输。这使得dvp接口的设计更为复杂,并且需要更多的空间来布线。

DVP接口一个PCLK周期可以传输1byte数据,1byte各位并行输出,一行Pixel输出完后,Sensor输出一个HSYNC行同步信号,一帧所有行输出完成后,输出一个VSYNC帧同步型号。

PCLK、D0、D1都是高频信号线(低位变化更加频繁),Layout时注意屏蔽干扰、不可与其它高频线并排或重叠走线,最好用GND线或者低频线(如D7、D6)隔开。

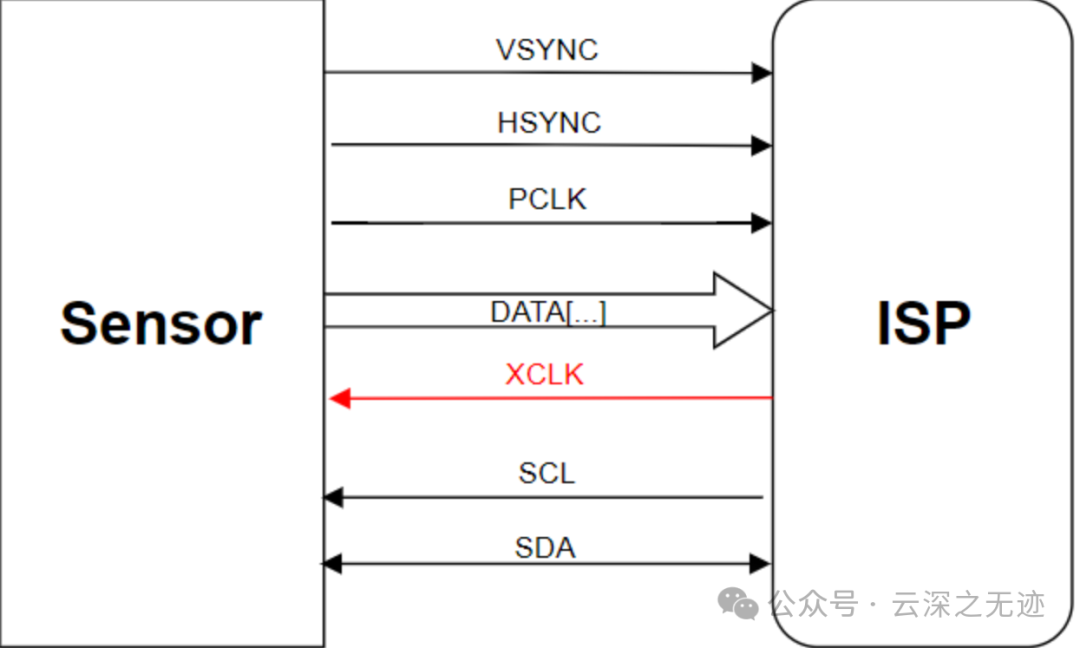

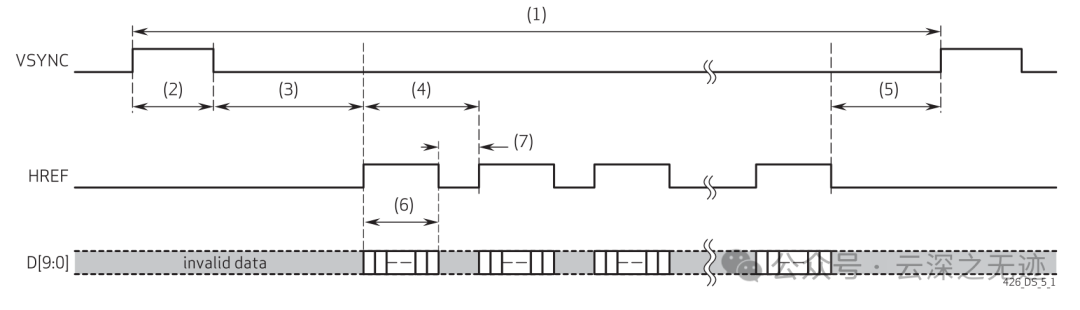

这图最经典了

VSYNC:vertical synchronization,帧同步信号, 一帧一个信号,频率为几十Hz

HSYNC:horizonal synchronization,行同步信号,一般为几十KHz

PCLK:pixel clock ,像素时钟,每个时钟对应一个像素数据

DATA: 像素数据,视频数据,常见的有8位和10位

XCLK:也叫 MCLK,ISP芯片输出给驱动 sensor 的时钟,可由 ISP 主控或晶振提供,

一般是24MHz/27MHz

SCL: IIC 时钟引脚,用来读写sensor的寄存器

SDA:IIC 数据引脚,用来读写 sensor 的寄存器

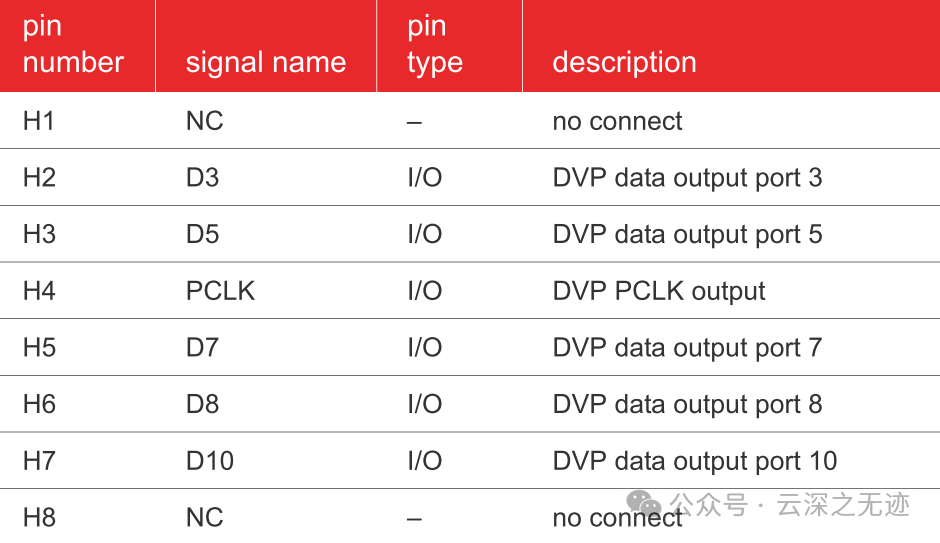

这里引脚放一部分

信号线虽然是说没有mipi那么严格

但是也是要保证等长,看电源

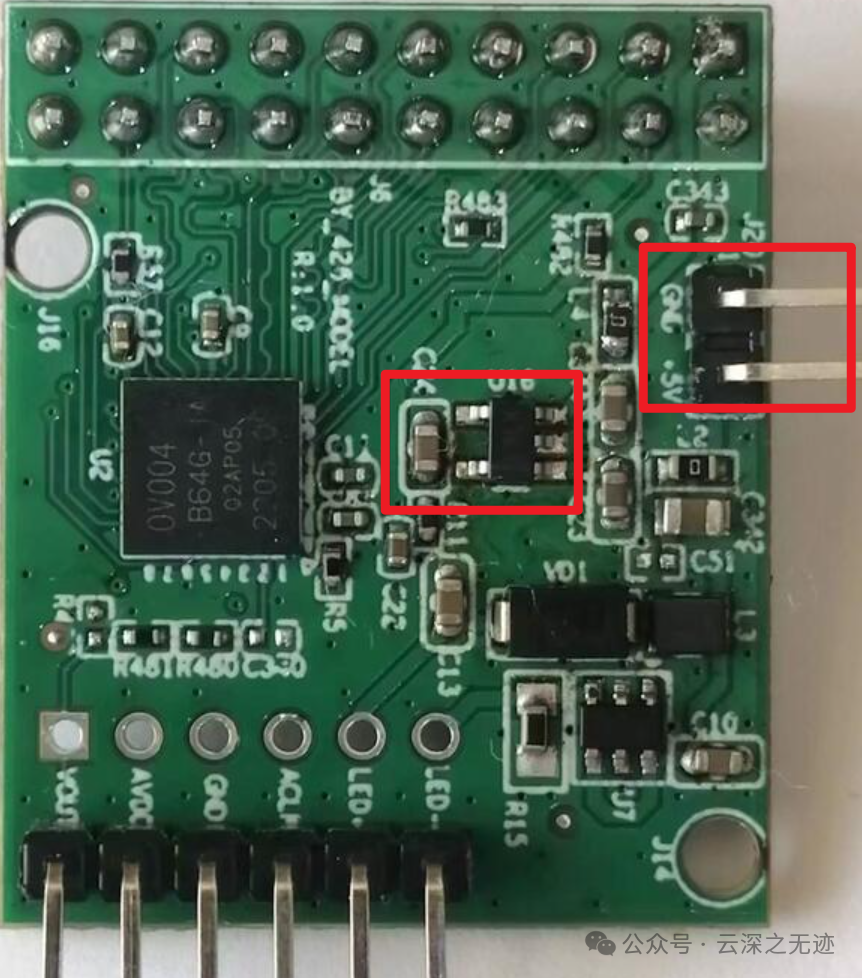

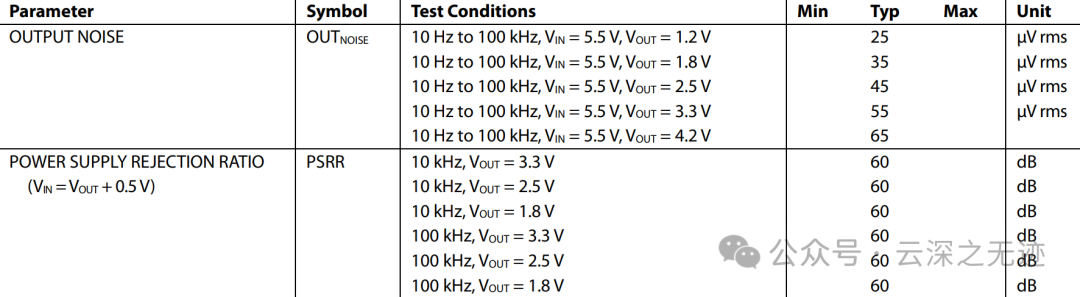

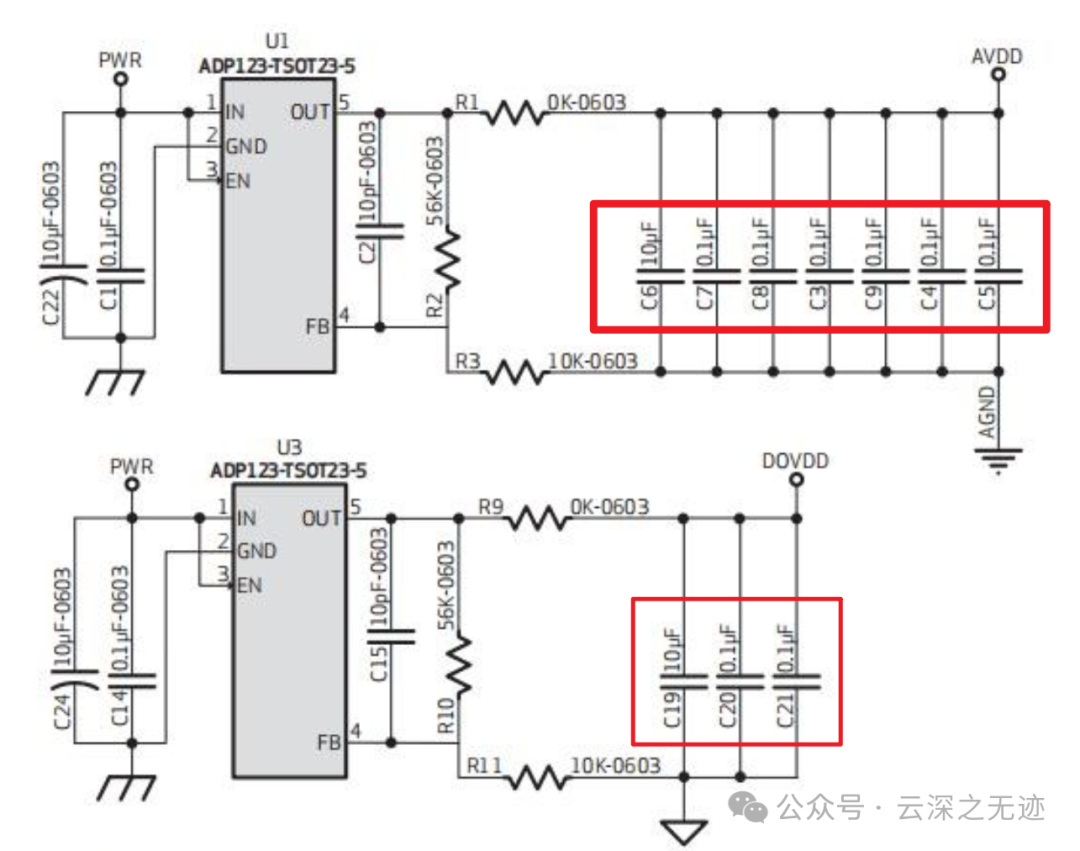

电源推荐ADP123,狠狠的加电容

模拟的比数字的电容更多

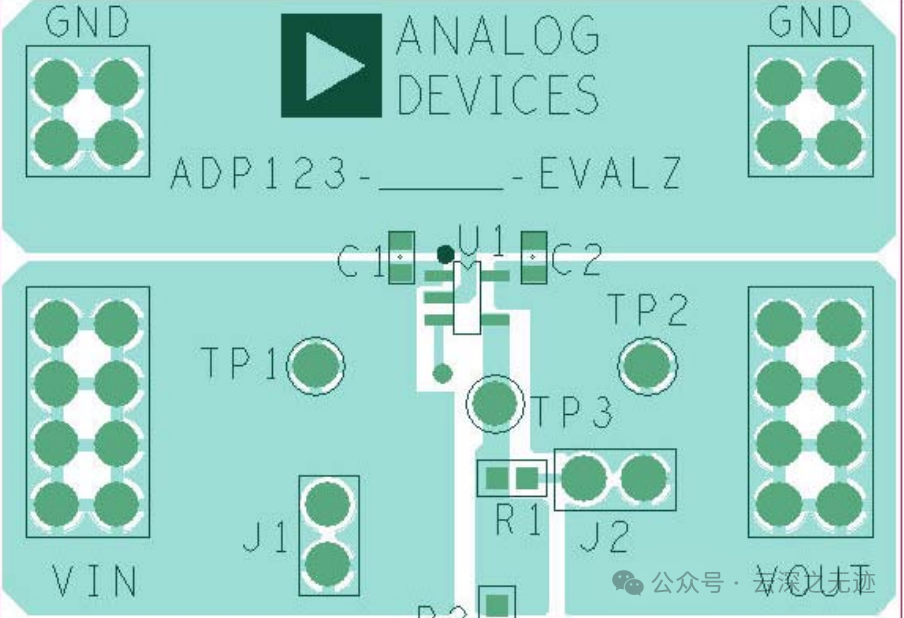

layout

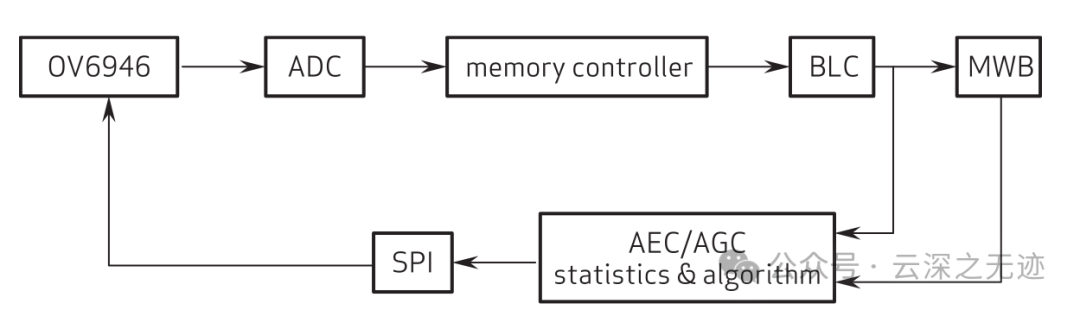

这个是内部的工作

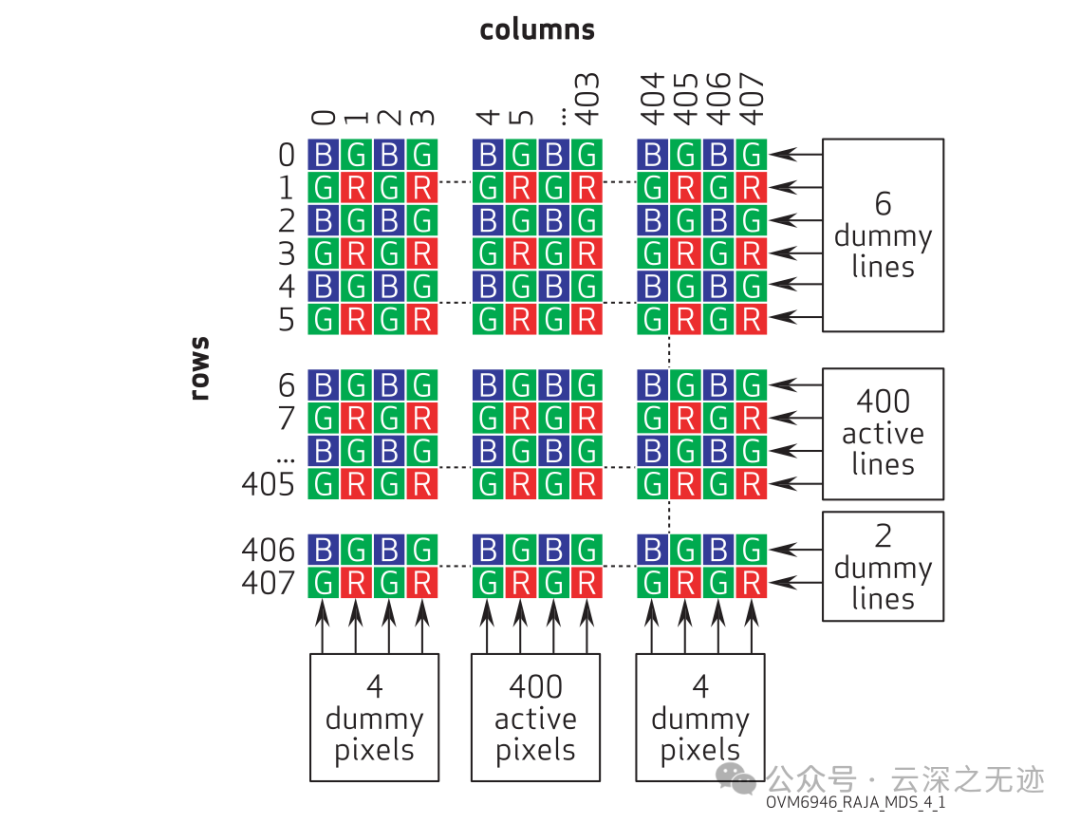

输出图像时,一帧帧地输出,在帧内的数据一般从左到右,从上到下, 一个像素一个像素地输出。

数据线会在1个像素同步时钟PCLK的驱动下发送1字节的数据信号,所以2个PCLK时钟可发送1个RGB565格式(我没有找到具体是什么)的像素数据。像素数据依次传输,每传输完一行数据时,行同步信号HREF会输出一个电平跳变信号,每传输完一帧图像时,VSYNC会输出一个电平跳变信号。

可以看这个

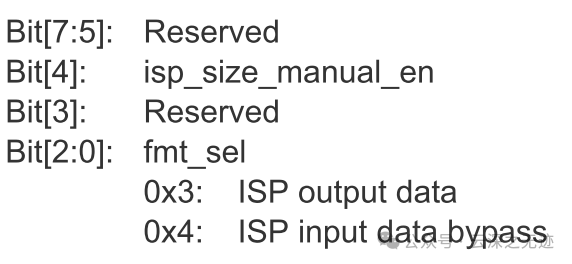

OV426的ISP很弱,所以需要外部ISP来补齐。

AEC 功能通过自动调整图像传感器的曝光时间来控制进入传感器的光量,确保图像既不过曝也不欠曝。

AGC 功能通过调整图像传感器的增益来控制图像的亮度。增益可以被视为图像信号的放大系数。

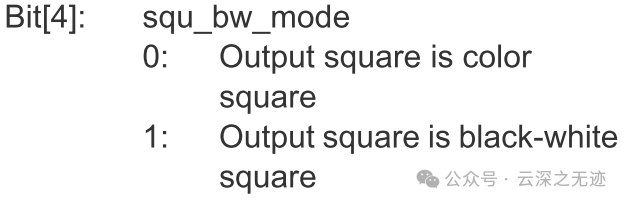

这个是一个有趣的寄存器,颜色

这个也是,可以输出拜耳图像,直接就不处理了

DVP的协议吧,一般都认为是和VGA的协议差不多:只是VSYNC信号高低电平相反了。DVP协议的HREF信号是在HERF为高电平是直接输出像素数据,而VGA接口的HSYNC信号在HSYNC为高时先后输出显示后沿、有效图像数据、显示前沿。

这里给出一个时序图分析

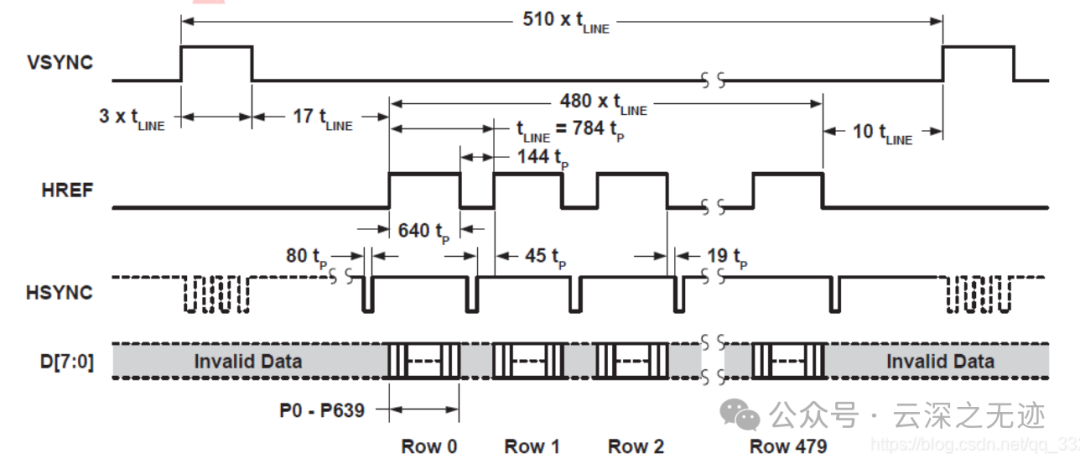

这个是OV7670的

数字的区域是时间,t=1/8Mhz

VSYNC(垂直同步): 指示一帧图像的开始和结束。在图中,一个 VSYNC 脉冲代表一帧图像的时间跨度。 HREF(水平参考): 用于标示一行像素的开始和结束。

在一帧图像内部,每当 HREF 信号为高电平时,对应的行像素数据被视为有效。 D[9:0](数据线): 传输图像数据的线。数据通常是在 HREF 高电平期间有效,并且在 VSYNC 低电平期间不断传输以构成一帧图像。

时序图中的各个部分代表:

(1): 整帧的周期,从一个 VSYNC 的下降沿到下一个下降沿。(看着是上升沿)

(2): VSYNC 信号内部,代表帧开始前的时间间隔,通常称为垂直前沿。

(3): 有效的帧传输时间,这时候 HREF 和 D[9:0] 会传输有效的图像数据。

(4): 垂直后沿,帧结束后到下一个帧开始前的时间间隔。

(5): 垂直同步信号持续的时间。

(6): HREF 信号内部,代表一行像素开始前的时间间隔,通常称为水平前沿。

(7): 有效的行传输时间,在此期间,D[9:0] 上会传输有效的像素数据。 图中的 "invalid data" 注释指出在 VSYNC 信号为高时,HREF 可能仍为高电平,但此时的数据不应被视为有效图像内容。

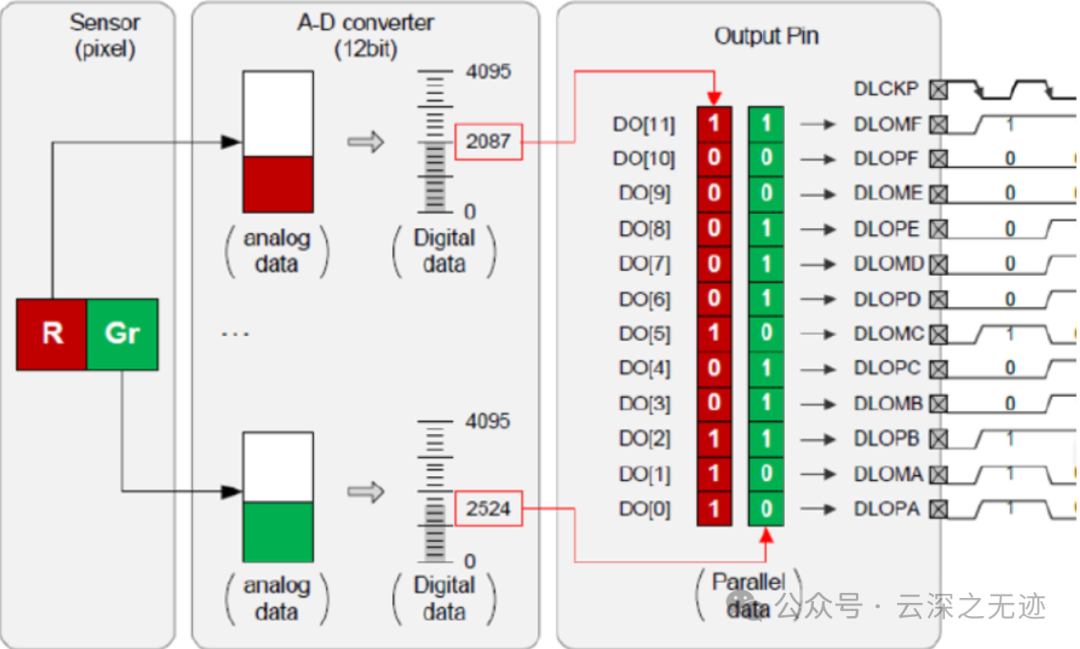

至于这个并口输出,这个好像是最形象的一个

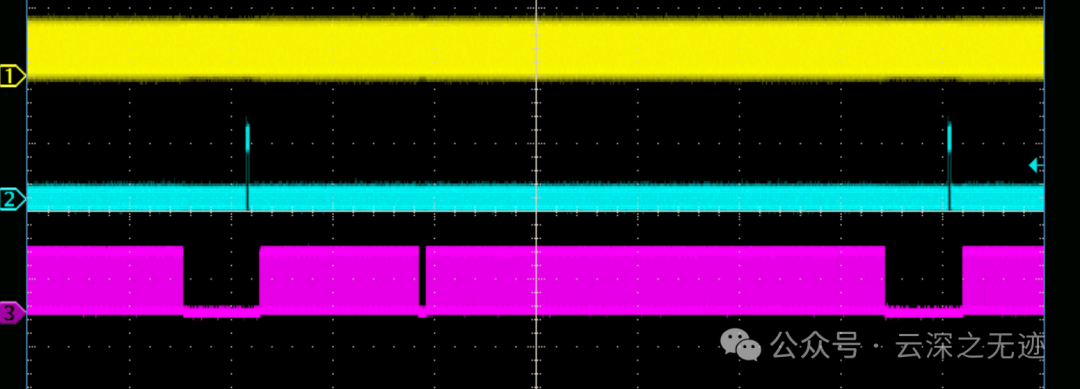

抓取的实测的 DVP 波形,黄色是输入时钟 ,蓝色是帧同步信号 ,红色是 PCLK(像素时钟)

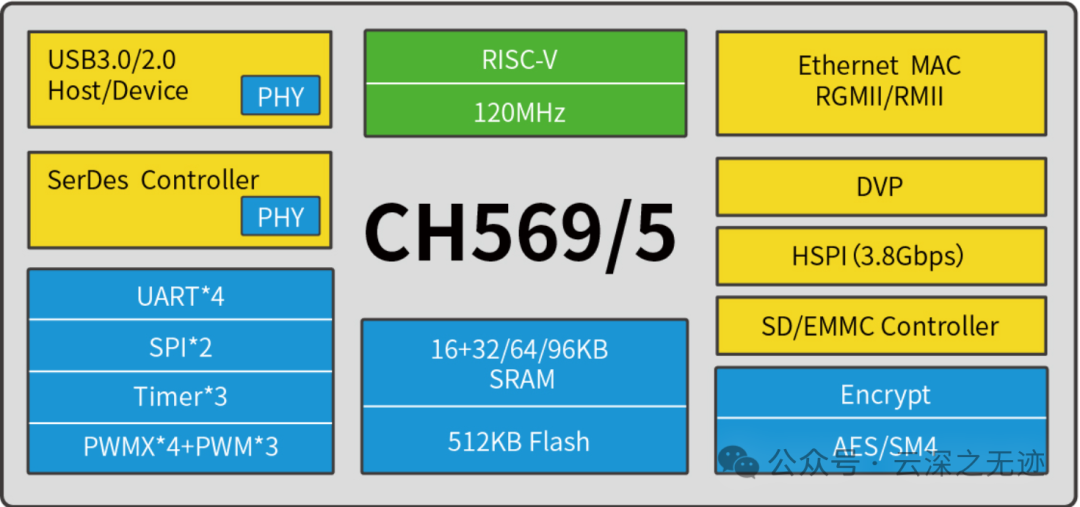

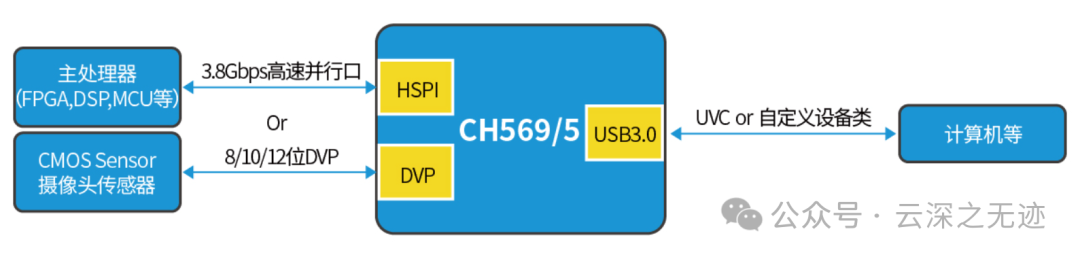

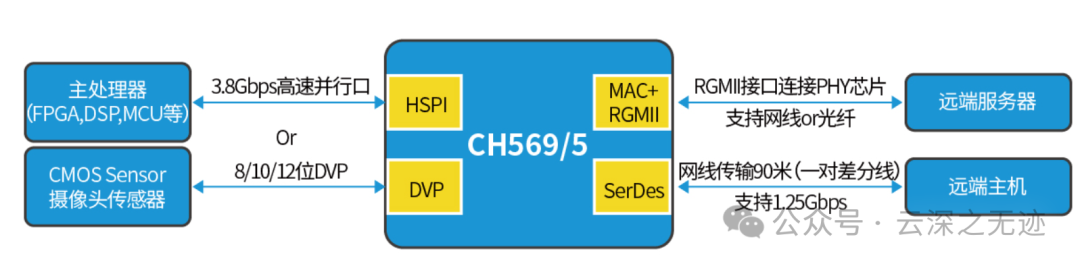

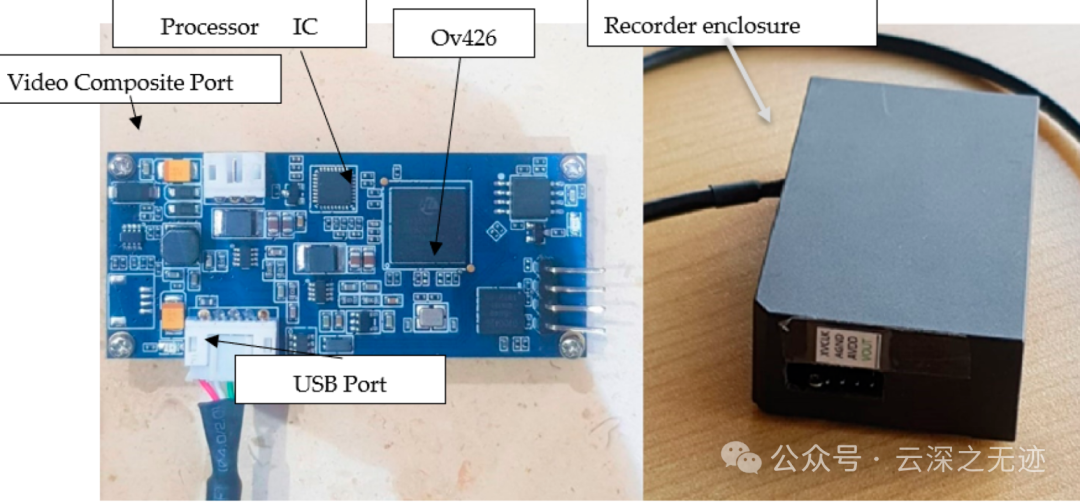

另外,我找到了一个芯片,这个可以直接当成USB输出,可以探索一下

一个拓扑图

也可以远程传输

审核编辑:刘清

-

汽车电子控制单元ECU的设计2009-10-06 290978

-

基于IXP425和DM642的会议电视多点控制单元硬件设计原理和实现方法介绍2019-06-28 2330

-

FPGA在赛车引擎控制单元有什么用处?2019-10-17 1520

-

Motronic发动机控制单元电路图2009-01-22 5045

-

ABS ECU控制单元是什么意思2010-03-11 16158

-

TCN线路冗余控制单元的研究2011-02-24 1073

-

上位控制单元在运动控制系统中的应用2011-07-22 847

-

充电控制单元原理图2012-05-21 3337

-

HCU控制单元硬件手册2017-09-27 3129

-

配网物理模拟系统控制单元设计2018-03-09 1029

-

ov426简介2018-07-22 3997

-

ov426最新规格书2022-07-31 1873

-

OV426最新规格书2023-12-11 1266

-

OV426相机桥接处理器规格书2024-10-09 1384

-

RDMA设计10:指令控制单元设计?2025-12-23 487

全部0条评论

快来发表一下你的评论吧 !