3D NAND的主要制作流程

存储技术

625人已加入

描述

3D NAND绝对是芯片制程的天花板,三星,海力士,英特尔,长江存储等都有3D NAND的产线,代表了一个国家的芯片制造水平。今天,我们就来剖析一下3D NAND的主要制作流程。

1,基底准备:选择12寸特定晶向的硅片。

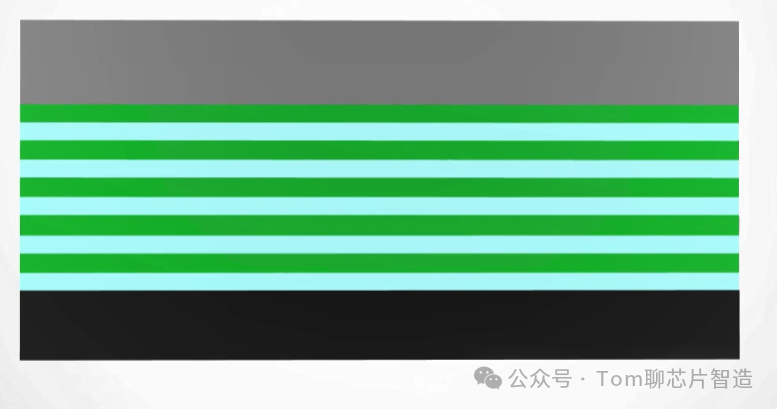

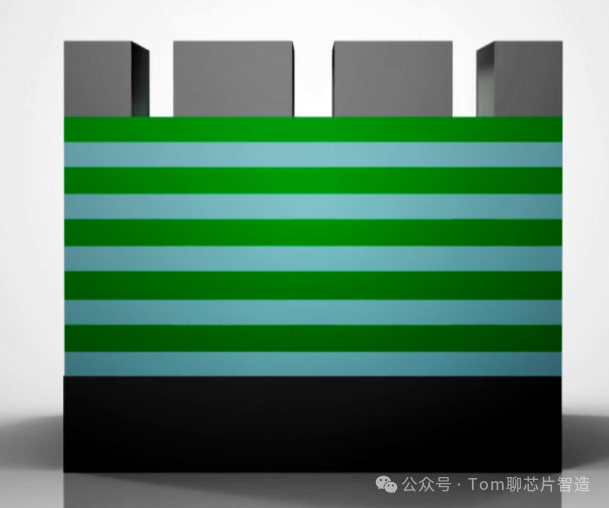

2,SiO2与SiNx交替镀膜,每层膜层在几十纳米左右。根据产品的不同,膜层的层数也不同。图中只是示意图,只有几层。但实际有64,128,400层等层数。

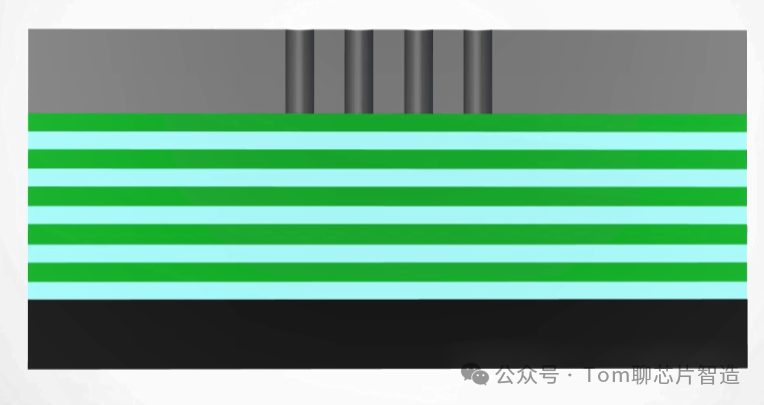

3,沉积无定形硅碳膜,这个是用来做沟道刻蚀的硬掩模。

4,硬掩模刻蚀,将硬掩模开口,以便于刻蚀堆叠的SiO2与SiNx材料

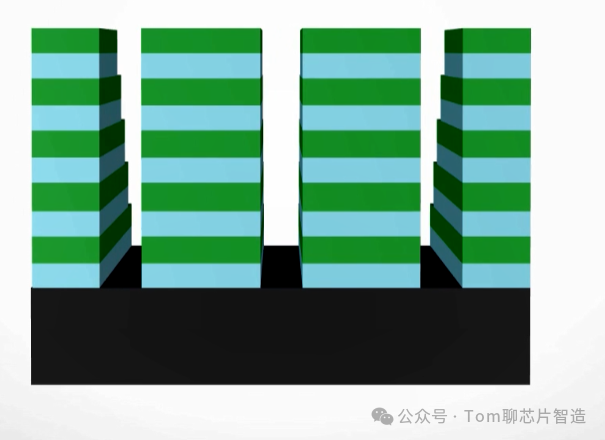

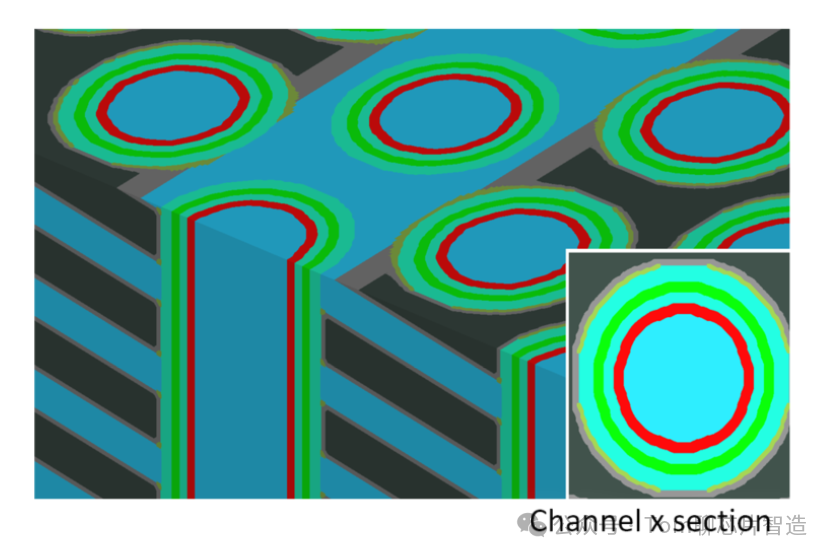

5,沟道通孔刻蚀,见文章:

《 3D NAND的沟道通孔是怎么做出来的?》

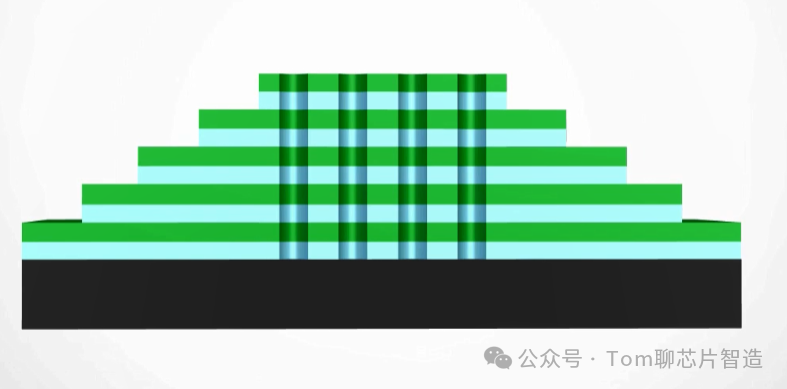

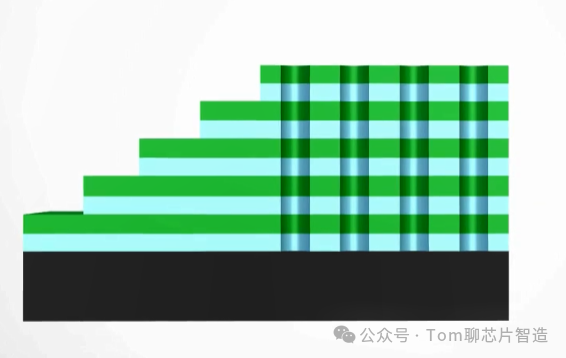

6,台阶刻蚀,见文章:

《3D NAND的台阶蚀刻(刻蚀)》

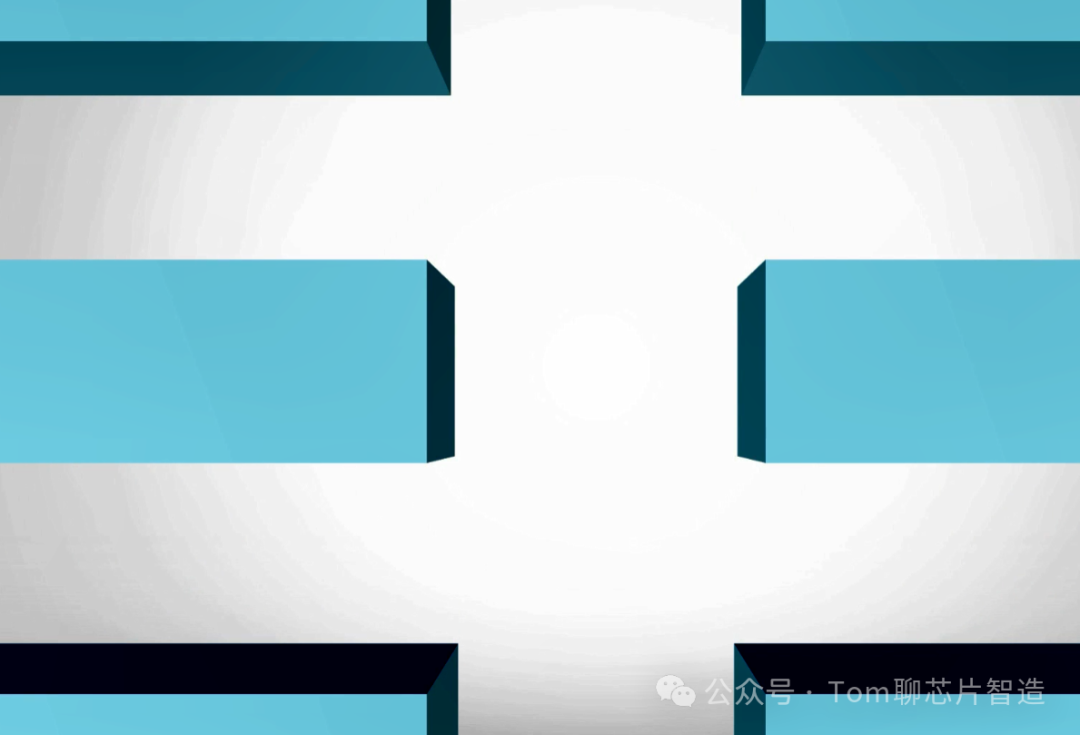

7,沉积无定形硅硬掩模,图片为侧视图

8,将硬掩模开孔

9,slit etch:将SiO2与SiNx的堆叠层刻蚀为一个个沟槽,

10,将堆叠层中的SiNx刻蚀掉,填充TiN,钨(W)等,即word line fill工艺。

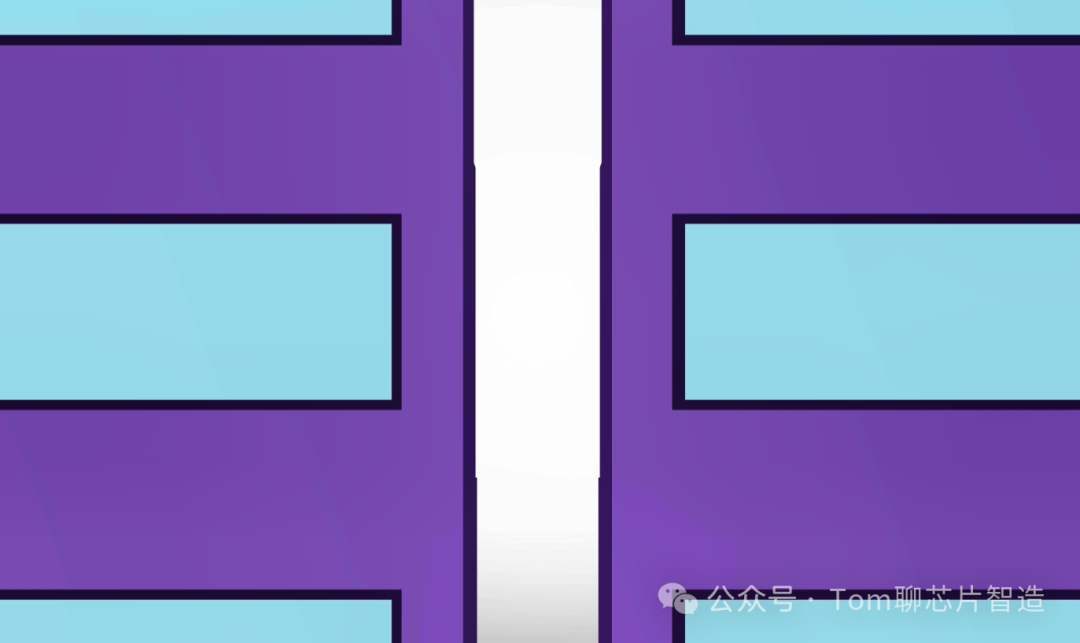

11,刻蚀掉多余的钨,之后需要对沟道通孔进行填充,因此需依次沉积阻挡氧化层,Charge Trap SiN (电荷陷阱氮化硅),Tunnel Oxide (隧道氧化物),Poly Si (多晶硅),Core SiO2 (硅基体)。功能区主体结构完成。

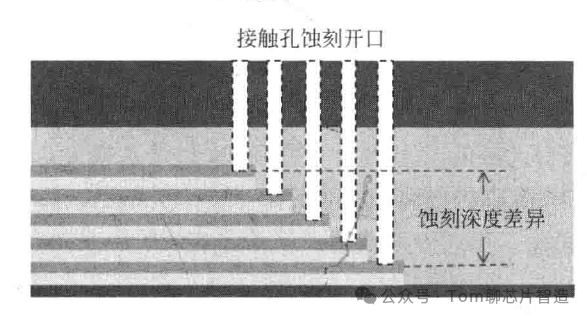

12,沉积介质层,并用CCP-RIE进行接触孔蚀刻。

13,用金属填充接触孔,并制作出连接接触孔的金属导线-Bit line,3D NAND的整个制程结束。

文中精简了比较多的重复步骤,实际工艺在数百步以上。

审核编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

什么是3D NAND闪存?2023-03-30 4683

-

3D NAND与4D NAND之间的差别在哪儿?2021-06-18 3167

-

不要过于关注3D NAND闪存层数2020-12-09 3901

-

未来的3D NAND将如何发展?2020-11-20 3491

-

美光发布176层3D NAND闪存2020-11-12 4023

-

3D NAND技术资料分享2019-09-12 2939

-

3d打印上色流程2019-05-19 11024

-

半导体行业3D NAND Flash2018-10-08 871

-

英特尔采用3D NAND技术的数据中心级固态盘发布,以便扩大3D NAND供应2018-08-01 1335

-

3D XPoint的原理解析 NAND和DRAM为什么拼不过它2018-04-19 52508

-

3D NAND良率是NAND Flash市场最大变数2017-02-27 1862

-

干货!一文看懂3D NAND Flash2016-08-11 44969

-

制作3D 对象,然后显示。 导入3D对象 ,然后显示。2015-12-23 17377

-

基于AD09的3d设计流程2015-05-15 4156

全部0条评论

快来发表一下你的评论吧 !