高速ADC用差分驱动器概述

模拟技术

描述

差分驱动器基础知识

目前许多高性能ADC设计均采用差分输入。全差分ADC设计具有共模抑制性能出色、二阶失真产物较少、直流调整算法简单的优点。尽管可以单端驱动,但全差分驱动器通常可以优化整体性能。

差分设计固有的低二阶失真产物如下所示。失真产物可以通过将电路传递函数表达为幂级数来建立模型。

进行输出一般扩展并假设放大器匹配,我们得到:

采用差分输出:

其中k1、k2和k3为常数。

二次项引起二阶谐波失真,三次项引起三阶谐波失真,如此等等。在一个全差分放大器中,奇数阶项保留极性,而偶数阶项则始终为正。当采取差分时,偶数阶项如等式3所示消除。三阶项不受影响。

差分输入ADC的一种最常用驱动方法是使用变压器。不过,因为频率响应必须延伸至直流,许多应用无法使用变压器来驱动。这类情况就需要使用差分驱动器。在ADC前面需要明显信号增益的情况下,差分放大器提供一种不错的解决方案。尽管提供"无噪声"电压增益,但匝数比大于2的变压器一般为带宽和失真问题所困扰,在中频时尤为明显。

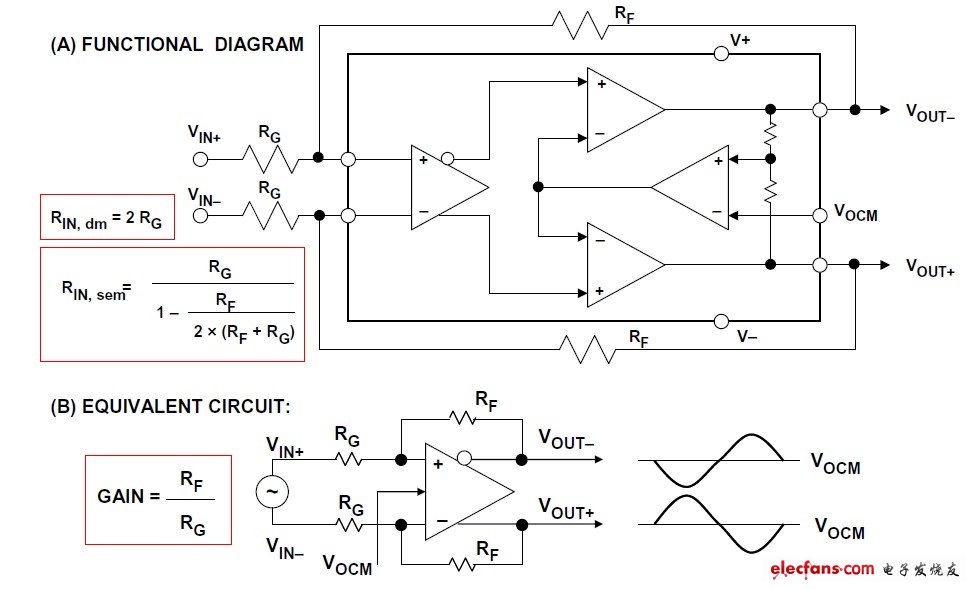

图1所示为驱动ADC而优化的AD813x和ADA493x系列全差分放大器框图。图1A显示内部电路细节,而图1B显示等效电路。增益由外部电阻RF和RG设定,共模电压由VOCM引脚上的电压设定。内部共模反馈强制VOUT+和VOUT–输出保持平衡,即在两个输出端的信号根据等式幅值始终相等,但相位相差180°。

图1:AD813x、AD493x差分ADC驱动器功能框图及等效电路。

AD813x和ADA493x用两个反馈环路,来分开控制差分输出电压和共模输出电压。外部电阻设定的差分反馈只控制差分输出电压。共模反馈控制共模输出电压。这种架构方便在电平转换应用中任意设定输出共模电平。内部共模反馈强制其等于VOCM输入上施加的电压,而不影响差分输出电压。其结果是近乎完美的平衡差分输出,在宽广的频率范围内其幅度完全相同,相位相差180°。该电路可配合差分或单端输入使用,且电压增益等于RF与RG之比。

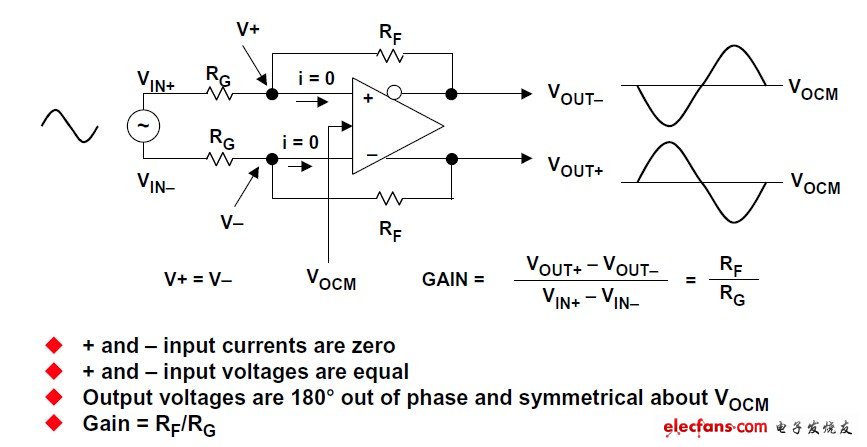

该电路可使用图2中所归纳的假设和程序来分析。如同运算放大器电路直流分析的情况,我们可以先假设流入反相和同相输入的电流为零(即输入阻抗相对反馈电阻值较高)。第二个假设为反馈强制同相和反相输入电压相等。第三个假设为输出电压相位相差180°并在VOCM两侧对称。

图2:差分放大器电平分析

即使外部反馈网络(RF/RG)不匹配,内部共模反馈环路仍将强制输出保持平衡。每个输出端的信号幅度保持相等,相位相差180°。输入到输出的差模增益变化与反馈的不匹配成比例,但输出平衡不受影响。外部电阻的比例匹配误差会导致电路抑制输入共模信号的能力降低,非常类似于使用常规运算放大器制成的四电阻差动放大器。

而且,如果输入和输出共模电压的直流电平不同,匹配误差会导致一个细小的差模输出失调电压。对于G = 1,具有一个地基准输入信号且针对2.5 V设定输出共模电平的情况,如果使用1%容差电阻,则可产生高达25 mV的输出失调(1%共模电平差)。由于2.5 V电平转换,1%容差的电阻将导致一个约40 dB的输入CMR(最差情况)、25 mV的差模输出失调(最差情况),不会对输出平衡误差造成明显恶化。

如图2所示电路的有效输入阻抗(在V IN+和V IN–端)取决于放大器是由单端信号源驱动,还是由差分信号源驱动。对于平衡差分输入信号,两个输入端(V IN+和V IN– )之间的输入阻抗(R IN,dm )为:

若为单端输入信号(例如,若V IN–接地,输入信号接入V IN+ ),输入阻抗则为:

该电路的单端输入阻抗高于作为反相放大器连接的常规运算放大器,因为一小部分差分输出电压在输入端表现为共模信号,从而部分增加了输入电阻RG两端的电压。

图3所示为AD813x差分放大器的一些可能配置。图3A为标准配置,其中利用两个反馈网络,分别表现为反馈系数 1和 2.另需注意,各反馈系数可能为0与1之间的任意数。

图3:差分放大器的一些配置

图3B显示在 V OUT–至V+之间无任何反馈的配置,即 1 = 0.在这种情况下, 2决定反馈至V–的V OUT+量值,且除了有额外的互补输出外,电路类似于同相运算放大器。因此,整体增益是同相运算放大器的两倍,或2 × (1 + RF2/RG2)或2 × (1/ 2)。

图3C显示 1 = 0且 2 = 1的电路。该电路特别提供无电阻增益2.

图3D显示 2 = 1的电路,而 1则由RF1和RG1决定。此电路的增益始终小于2.

最后,图3E的电路 2 = 0,除V OUT+端的额外互补型输出外,极其类似于常规反相运算放大器。

差分驱动器/接收器应用

AD813x/ADA493x系列也非常适用于平衡差分线路驱动,如图4所示,其中AD8132驱动一根100 双绞线。AD8132配置成一个增益为2的驱动器,说明来源和负载端接电缆所引起的2倍损耗。在此配置下,AD8132的带宽约为160 MHz.

图4:高速差分线路驱动器、线路接收器应用

该线路接收器为一个AD8130差分接收器,具有一种称为"有源反馈"的独创架构,可在10MHz时实现约70 dB的共模抑制。对于增益1,AD8130的3dB带宽约为270 MHz.

AD8130利用两个相同的跨导(gm)级,其输出电流在高阻抗节点处加总,然后缓冲至输出端。两个gm级的输出电流必须相等,符号相反,因此各自输入电压也必须相等,符号相反。

差分输入信号接入其中一级(GM1),而负反馈则如同常规运算放大器接入至另一级(GM2)。

增益等于1 + R2/R1.GM1级因此为端接双绞线提供一个真正平衡的输入,以获得最佳的共模抑制。

一系列三路驱动器用于在5类电缆上驱动RGB,例如AD8133、AD8134、AD8146、AD8147、 AD8148.

也可提供相应的三路接收器,包括AD8143和AD8145.AD8123(三路)和AD8128(单路)接收器也包括可调节线路均衡。

应用示例:ADA4937-1差分放大器驱动AD6645 14位80/105MSPS ADC

AD813x和ADA493x系列差分驱动器适用于直流或交流耦合应用,其中电压增益1至4(0 dB至12 dB),频率高达约100 MHz(取决于该系列的特定成员)。它们特别适合用作低失真直流耦合单端至差分转换器以驱动差分输入ADC.VOCM特性可用于电平转换双极性信号以匹配ADC的共模输入电压。直流驱动器的电路分析细节和电阻值挑选在MT-xxx中给出。还提供ADIsimDi Amp设计工具以方便这类设计。

ADA4937-1是最新系列差分放大器之一,针对+5 V单电源特殊优化。图5显示它用作一个电平转换器以驱动AD6645 14位80/105 MSPS ADC.(ADA4939-1是一个针对电压增益 2而优化的类似器件)。

图5:ADA4937-1在+5 V直流耦合应用中驱动AD6645

现在将在信号摆幅和共模电平方面对图5所示电路进行细致分析。为确保所有电压落入器件规定的允许范围内,这一步必不可少。

AD6645利用一个2.2 V p-p差分信号操作,共模电压为+2.4 V.这意味着ADA4937的每个输出必须在1.85 V和2.95 V之间摆动,即在+5 V单电源运行的ADA4937-1的输出驱动能力范围内。

输入信号因此必须在1.025 V和1.575 V之间摆动,落入在+5 V单电源运行的ADA4937-1的允许输入范围内。

电路输入由一个50 来源驱动。在单端配置中"自举式"输入阻抗约为267Ω 。61.5Ω 输入终端电阻与267Ω增益设定电阻并联使得整体阻抗约为50 Ω。注意,228 Ω电阻是与反相输入串联插入的。这是为了匹配同相输入的净阻抗(200 Ω + 61.5 Ω||50 Ω= 200 Ω+ 28 Ω= 228Ω)。

没有此额外28Ω匹配电阻与最初200Ω增益设定电阻串联,不平衡源阻抗会导致一个不必要的差分失调电压出现在输出端上。

底部增益设定电阻从200Ω增加至228Ω需要反馈电阻增加至207Ω以便保持增益1.实际上,最近标准1%电阻会代替计算值。ADIsimDi Amp设计工具用来方便这类设计并计算特定增益和源阻抗的所需电阻值。该工具还检查是否违反差分放大器的输入和输出共模范围限制。

ADA4937-1的输出噪声电压频谱密度只有5 nV/√Hz.该值包括反馈和增益电阻的贡献并适用于G = 1.这在AD6645的输入带宽(270 MHz)上积分,产生103 V rms的输出噪声。这对应于放大器所引起的77.6 dB SNR.注意,由于没有任何外部噪声滤波器,积分必须在ADC的完整输入带宽上。

AD6645的SNR为75 dB,对应于138μV rms的输入噪声。由于运算放大器(103μV)和ADC(138μV)所引起的组合噪声为172μV,产生73 dB的整体SNR.

如果不需要AD6645的完整带宽,可通过选择适当的C值来增加一个单极降噪滤波器。

适合中频应用的宽带交流耦合ADC驱动器

在图6所示的示例中,我们数字分析了AD9445 14位125MSPS ADC的宽带信号,希望尽量保留ADC输入带宽。因此没有任何中间级噪声滤波器。

图6:AD8352 2GHz 差分放大器驱动AD944514位 125MSPS ADC

在100 MHz时,AD9445输入带宽为615 MHz,SFDR为95 dBc.对于驱动器,我们挑选了AD8352 2 GHz带宽差分放大器,因为其电阻可编程增益范围为3 db至21 dB.该放大器还具有低噪声(对于10 dB增益设置,等效输入噪声为2.7 nV/ Hz)、低失真(100 MHz时82 dBc HD3 )。带宽要求的更低端约为10 MHz.

图6所示为在宽带应用中利用2 GHz AD8352驱动AD9445的最佳电路配置。巴伦将单端输入转换为差分以驱动AD8352.尽管可配置AD8352以接受一个单端输入(见AD8352数据手册),但如果按图所示以差分驱动,则获得最佳的失真性能。选择CD/RD网络是为了优化AD8352的三阶交调性能。这些值是基于所需增益而选择并在数据手册中给出。

该电路对于105 MSPS采样的98.9 MHz输入信号产生83 dBc的SFDR.

G = 10时AD8352的输出噪声频谱密度为8.5 nV/ Hz.由于没有任何输入滤波器,这必须在AD9445的整个615 MHz输入带宽上积分。组合放大器和ADC的SNR为67 dB.

-

ADI-高速差分ADC驱动器设计指南2023-11-27 562

-

高速差分ADC驱动器的设计指南2023-11-23 386

-

用于降低差分ADC驱动器谐波失真的PCB布局技术2023-01-27 2193

-

MT-074: 精密ADC用差分驱动器2021-03-21 1111

-

ADA4945-1:高速、±0.1 µV/˚C失调漂移、全差分ADC驱动器2021-03-20 739

-

高速PCB布局:高速差分ADC驱动器轨至轨和轨至地旁路电容器布置方案2021-03-01 4245

-

如何针对设计选择合适的差分ADC驱动器2019-06-20 4459

-

高速差分ADC驱动器设计指南(二)2018-11-01 5100

-

高速差分ADC驱动器设计指南(一)2018-10-17 6164

-

一文了解高速差分ADC驱动器设计考虑2018-04-08 1229

-

高速差分ADC驱动器设计考虑2011-11-28 886

-

全差分驱动器释放高速ADC性能潜力2010-09-15 388

全部0条评论

快来发表一下你的评论吧 !