芯片制造工艺:光学光刻-掩膜、光刻胶

制造/封装

描述

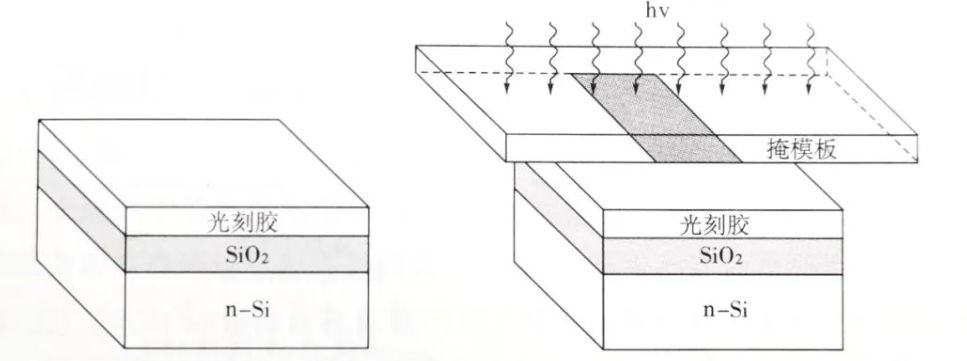

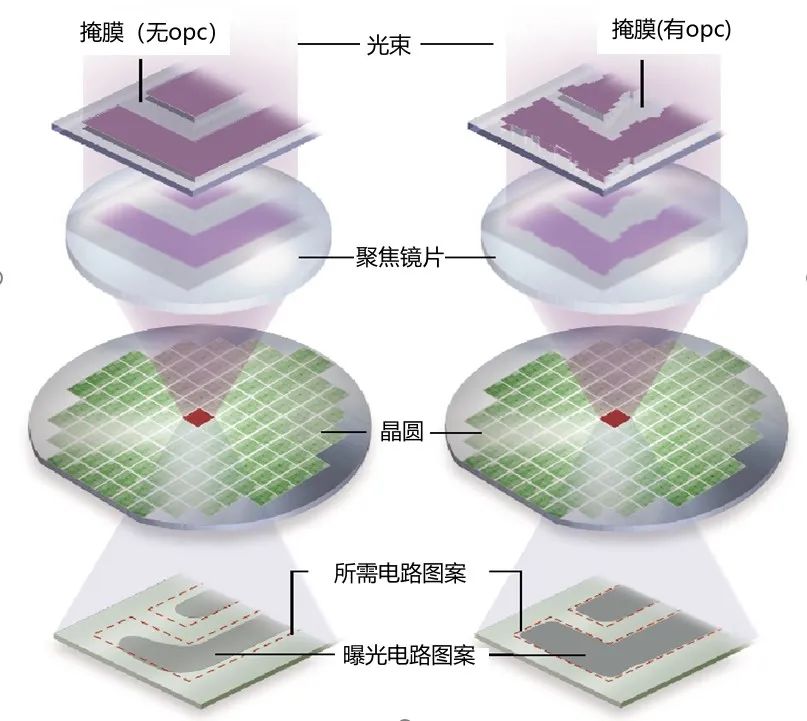

光刻就是将掩膜上的几何图形转移到涂在半导体晶圆表面的光敏薄层材料(光刻胶)上的工艺过程。为了产生电路图形,还需要再一次把光刻胶上的图形转移到光刻胶下面的组成集成电路器件的各层上去(刻蚀)。

1.光学光刻-掩膜、光刻胶

1.1 洁净室

由于空气中的尘埃粒子会落到半导体晶圆和光刻掩模上,致使器件中产生缺陷,导致集成电路失效,因此洁净室是必需的。 制造集成电路的大多数工艺区域要求100级(空气中每立方米内直径大于等于0.5μm的尘埃粒子总数不超过约3500)洁净室,在光刻区域,洁净室要求10级或更高。

1.2 光刻胶

光刻这个步骤中,首先是涂光刻胶:

涂光刻胶的过程:

将光刻胶涂在晶圆上,并让晶圆高速旋转,使光刻胶均匀分布

图源:Sanken Electric

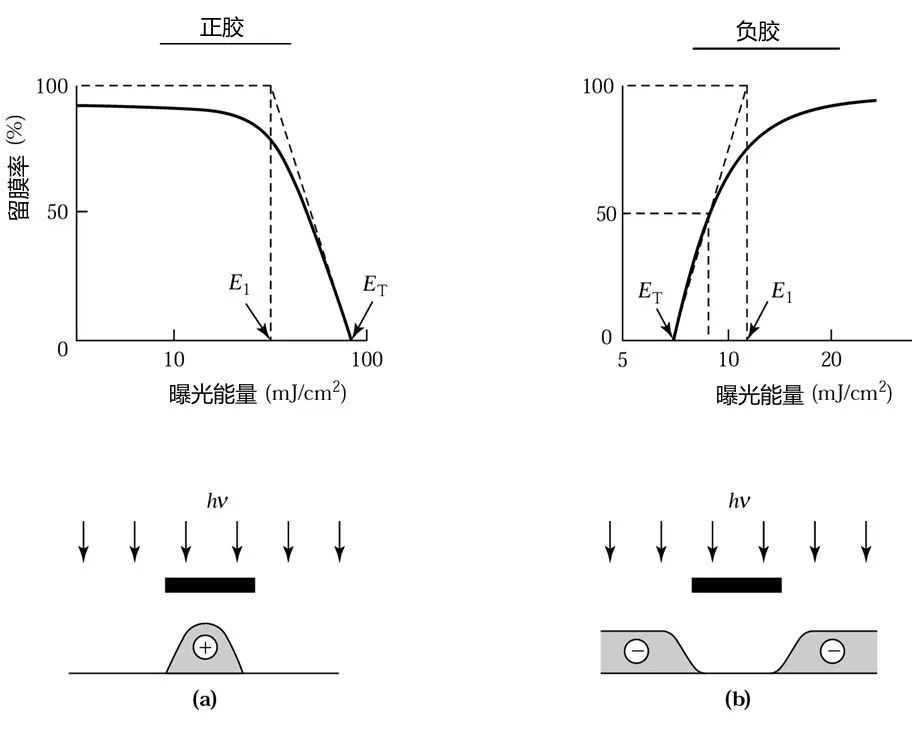

光刻胶是一种对辐射敏感的化合物,分为正胶和负胶。正胶的曝光部分在显影时更易溶于溶剂而被去掉,所得的图图像与掩模上的相同。负胶的曝光部分在显影时更不易被溶解,因此所得图形与掩模上的相反。

图(a)给出了典型的曝光反应曲线与正胶图像的截面图。光刻胶即使没有曝光,在显影液中也有一定的可溶性。随着曝光能量的增加,可溶性逐渐增加,达到阈值能量Er后,光刻胶完全可溶。图(b)负胶同理。

由于存在衍射,光刻胶图像边缘一般不在掩膜图像边缘的垂直投影位置上,而是在吸收的光能总量等于阈值能量Er的位置上。

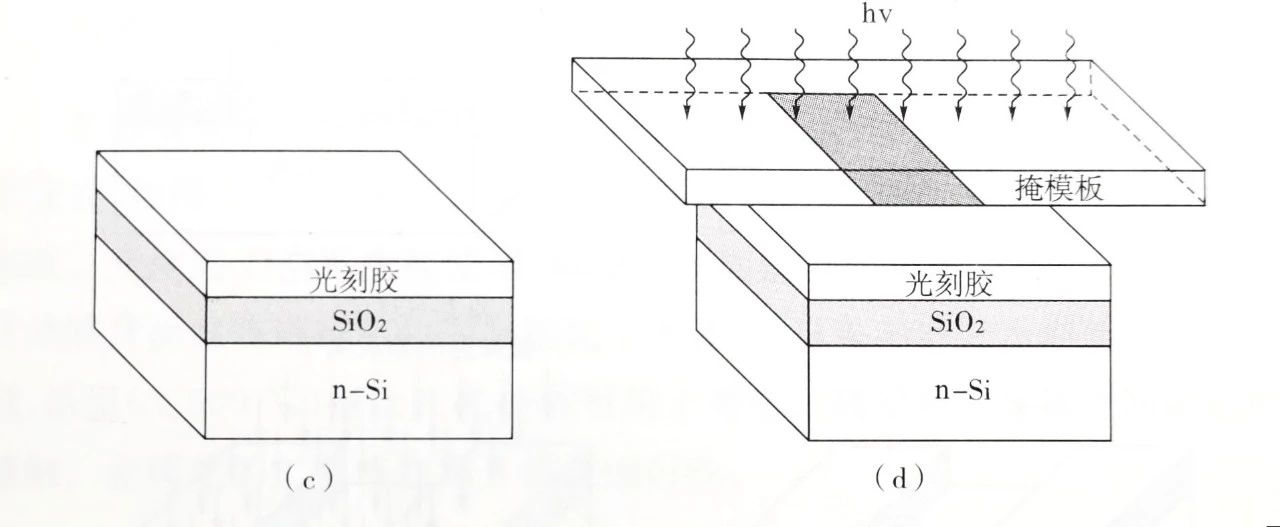

1.3 掩膜

集成电路制造所用的掩膜通常是缩小倍数的掩膜。制作掩膜是用电子束曝光系统将图形直接转移到对电子束敏感的掩膜上。掩模由镀铬玻璃板组成。电路图形首先被转移到对电子敏感的掩模上,再被转移到下面的镀铬层上,最终得到需要的掩模。

一块掩膜上的图形代表了集成电路设计中的一层。综合的布局布线图按照集成电路制造对应的工序分成若干块掩模层,例如隔离区是一层,栅极区是另一层等。一般一个完整的集成电路工艺流程需要15~20层不同的掩膜。

2.光学光刻-曝光(设备、原理)

2.1 遮蔽式曝光(接触式曝光、接近式曝光):

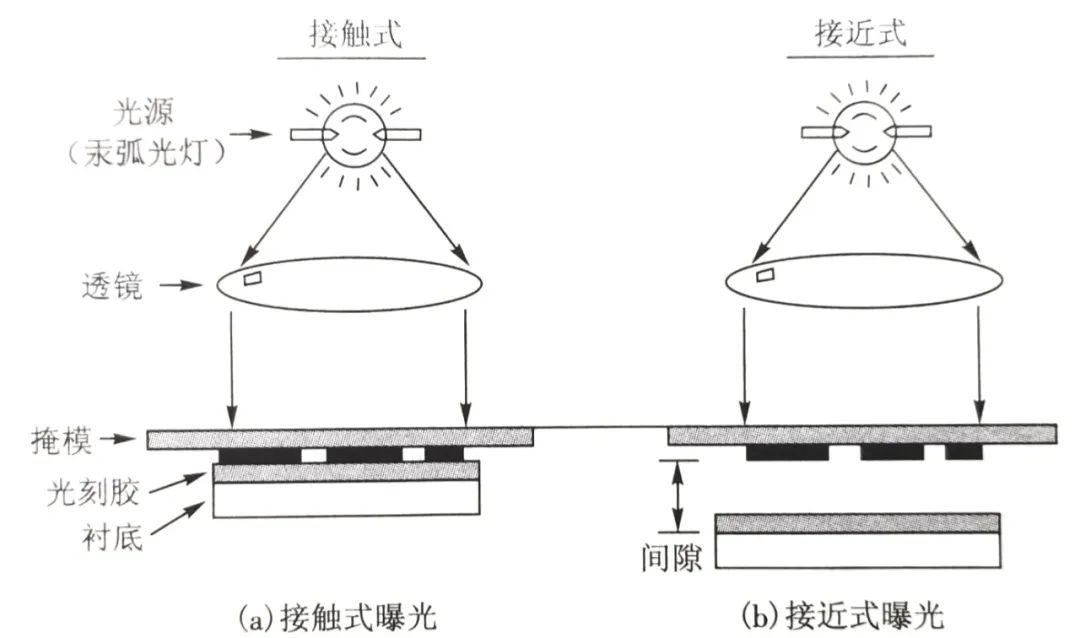

有两种基本的光学曝光方法:遮蔽式(shadow)曝光与投影式(projection)曝光。遮蔽式曝光可分为两种:掩模和晶圆直接接触,称为接触式曝光;掩模和晶圆非常靠近但不接触,称为接近式曝光。

图(a)为接触式曝光。涂了光刻胶的晶圆与掩模直接接触,分辨率可达1μm。但是,当掩模与晶圆接触时,晶圆上的尘埃粒子或硅渣会嵌入掩模,对掩模造成永久性损伤,使随后使用它曝光的每个晶圆上都留下缺陷。

要把掩模的受损程度减至最小,可采用接近式曝光,如图(b)所示:曝光时在掩模与晶圆之间有一个小的间隙(10~50μm)。这个小间隙使掩模图形边缘处形成光学衍射,即在光通过不透明掩模图形边缘时,形成一些干涉条纹,有一些光进入阴影区,使分辨率降到2~5μm范围.

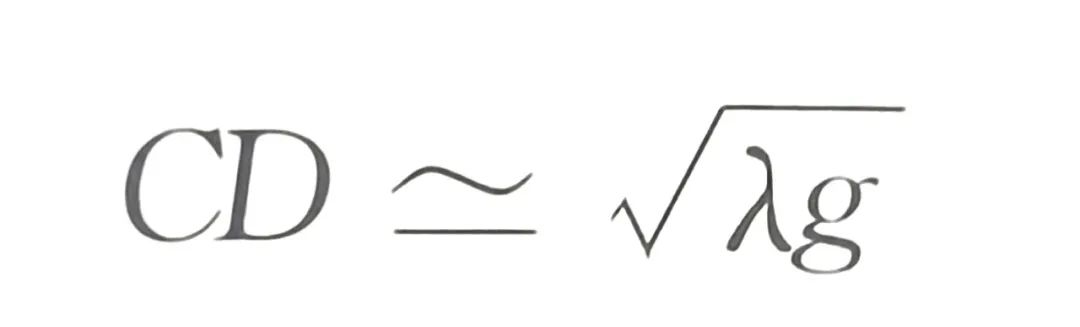

在遮蔽式曝光中,可以达到的最小线宽CD(critical dimension,也称临界尺寸)约为

因此,减小λ(曝光所用的光波波长)与g(掩模与晶圆之间的距离,包括光刻胶的厚度)都是有利的。 当λ=0.4 μm,g=50 μm时,临界尺寸CD为4.5 um。若λ降到0.25μm(波长为0.2~0.3μm的光属于紫外光谱区),g减小到15μm,则CD降为2μm。然而,在距离g给定后,直径大于g的尘埃粒子仍能造成掩模的损伤。

2.2 投影式曝光

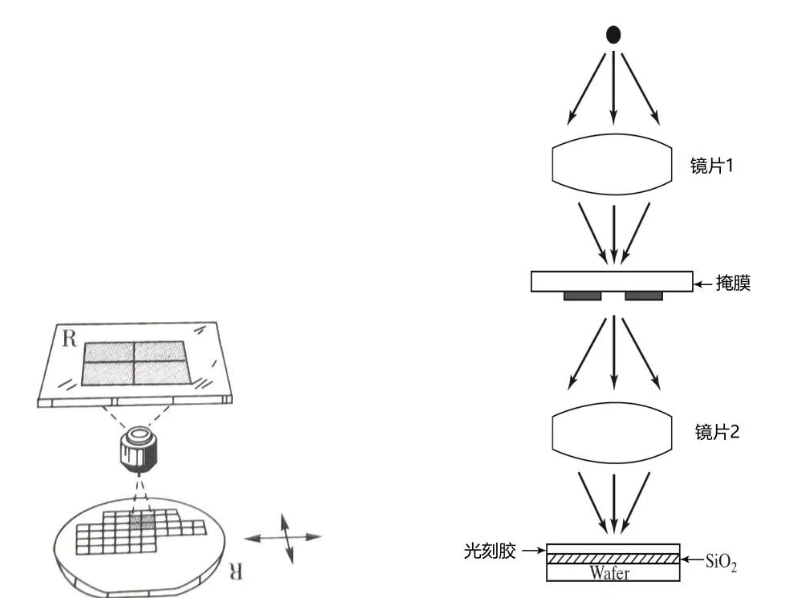

为了克服遮蔽式曝光的掩模损伤问题,出现了投影式曝光设备:

此类设备可将掩模上的图形投影到距离掩模几厘米远的涂有光刻胶的晶圆上。每次只曝光掩模的一小部分,然后移至下一个芯片位置曝光,用扫描或分步重复的方法使小面积图形布满整个晶圆。

图源:Sanken Electric

重点:分辨率的影响因素有哪些:

投影时,当掩膜上的尺寸比光的粒子性质大,效果就很好。但在较小的尺寸下,即掩模上的尺寸与光的波长相当,衍射效应占主导地位,即光的波动性。

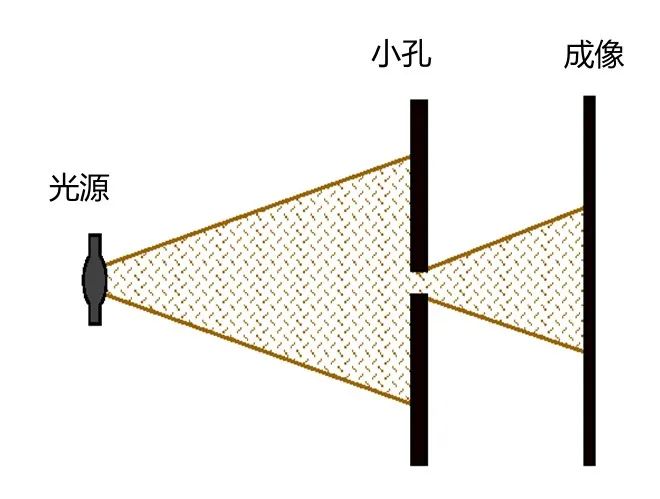

艾里斑(Airy disk)是点光源通过衍射受限成像时,由于衍射而在焦点处形成的光斑。

艾里斑(Airy disk)

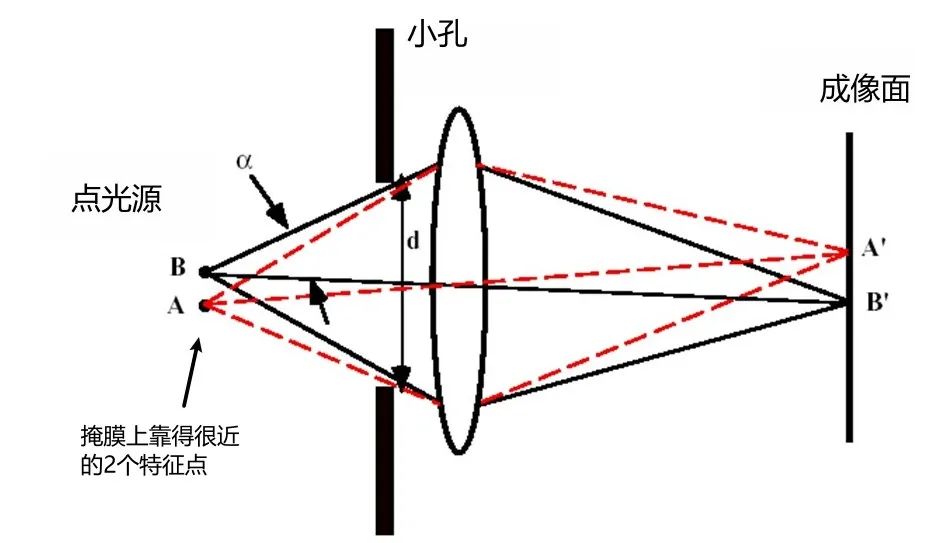

最中心的圆的直径为1.22λf/d。那么掩膜上2个很紧邻的特征会发生什么?

图源:https://slideplayer.com/slide/5732688/

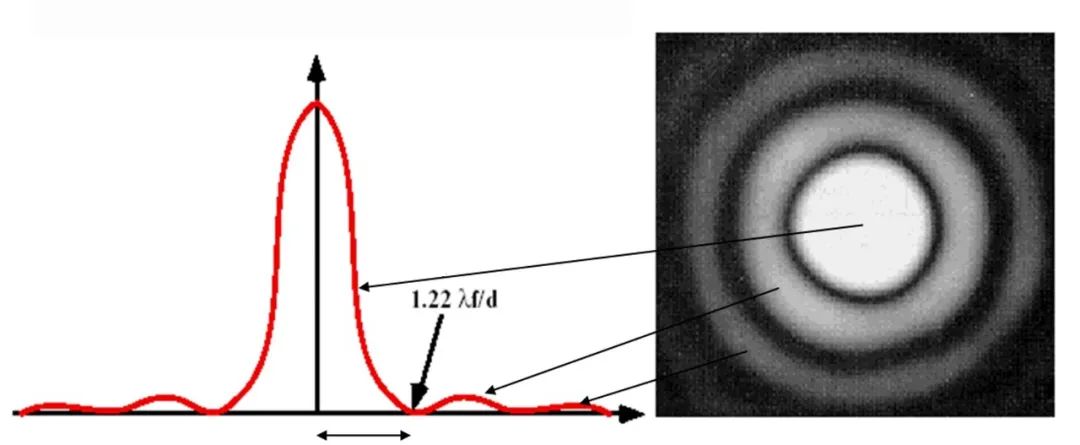

成像面上的A'和B'是否可分辨呢?这就引出了瑞利判据:

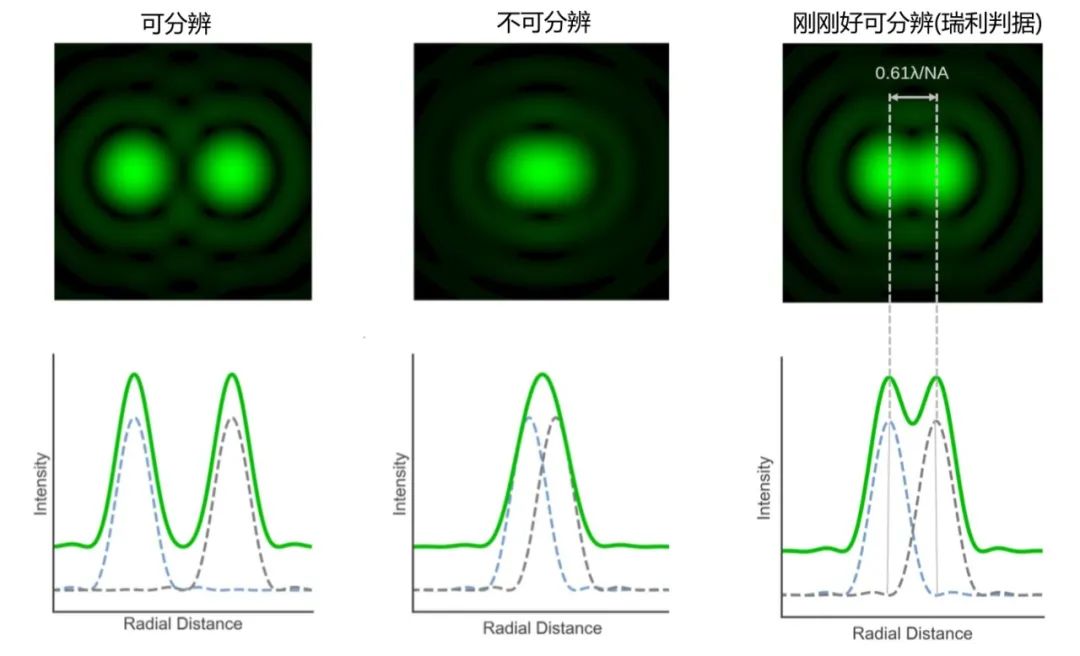

考虑衍射情况下的艾里斑,当2个物点过于靠近,则不可分辨;当一个物点正处在另一个物点的艾里斑的第一个暗环位置时,称为刚刚好可分辨的状态:

图源:www.edinst.com

依据瑞利判据,有了投影系统分辨率(线宽)的公式:

lm=k1 · λ / NA

λ为曝光波长。

k1为工艺参数,包含光学邻近效应、光刻胶的化学成分、光刻系统的温度等多个参数。

NA为数值孔径,由下式给出:

NA=nsinθ

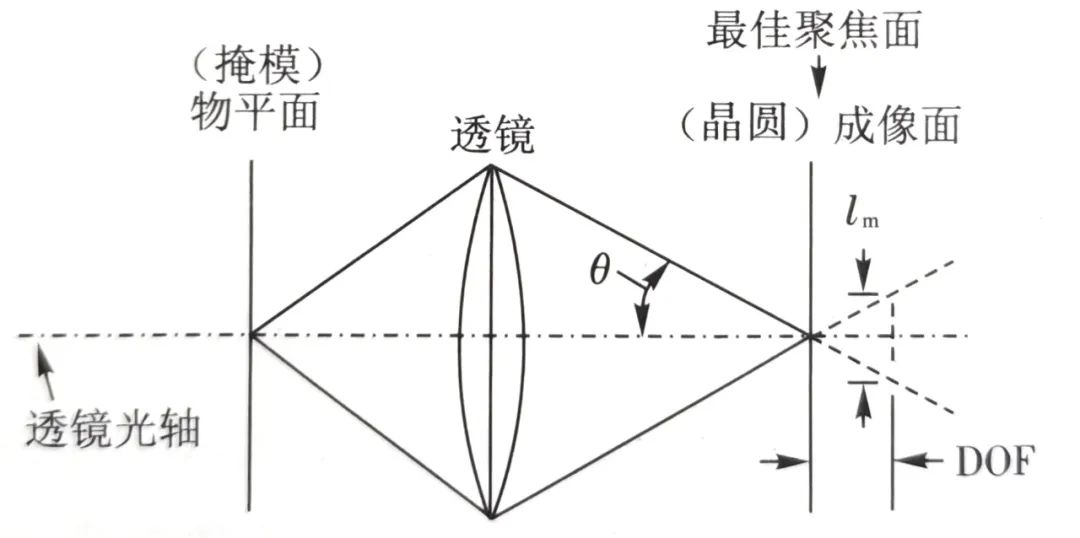

其中,n为成像介质的折射率,θ为光线在晶圆处汇聚成点像时的锥体顶角的一半

从分辨率公式 lm=k1 · λ / NA 可知,要提高分辨率,可以减小λ 、减小k1或增大NA。从上图也可以看到,θ的增大虽然会增大NA,但是也会让焦深DOF减小。

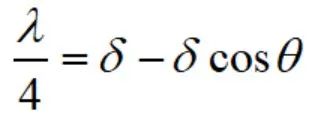

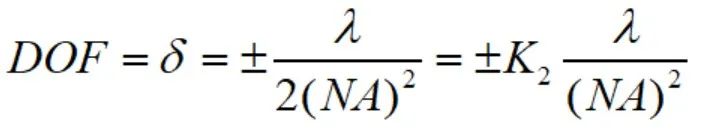

瑞利判据还有第二个限制条件是针对焦深DOF(δ)做出的,即:

所以,在优化过程中,需要综合考虑多方面因素。

3.光学光刻-提高分辨率:

3.1 减小λ:从436nm到13.5nm

图源:整理自《半导体制造工艺基础》、《极紫外光刻》

3.2 增大NA

根据公式 NA=nsinθ 可知,NA由透镜的接收角和透镜周围介质的折射率决定。所以,有两个方向可以增大NA:

(1)优化镜片(改变sinθ)

在曝光波长缩短的同时,镜头设计的改进也导致曝光系统镜头的数值孔径(NA)得到改善,见图 。在八十年代中期,NA 值约为 0.4 ,后来248nm 曝光系统的 NA 大于 0.8。使用空气作为透镜和晶圆之间介质的曝光系统的 NA 物理极限为 1,实际极限约为 0.9.

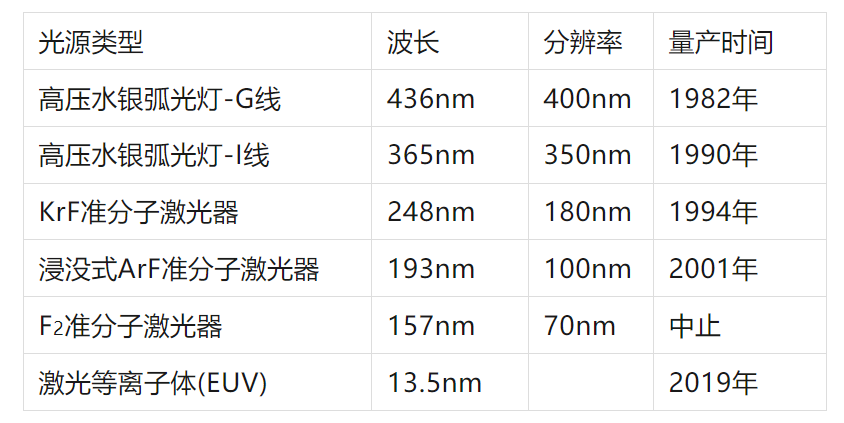

(2)改变介质(折射率)--浸没式光刻

NA 由透镜的接收角和透镜周围介质的折射率决定。基于空气的系统的物理限制是明确的,但如果用具有更高折射率的介质代替空气呢?多年来,显微镜一直在镜头和所观察的样品之间使用油来提高分辨率,令人惊讶的是,半导体行业花了很长时间才考虑用替代品替代空气。

图源:www.nikon.com

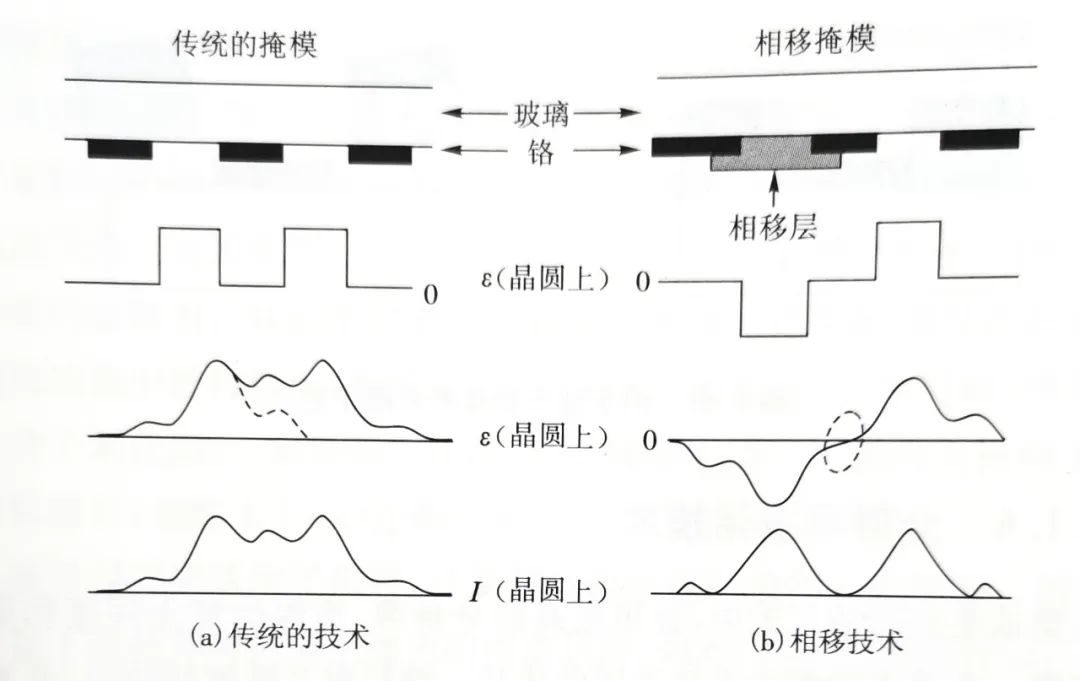

3.3 减小K1:相移掩膜、光学邻近效应矫正、离轴照明、双重曝光

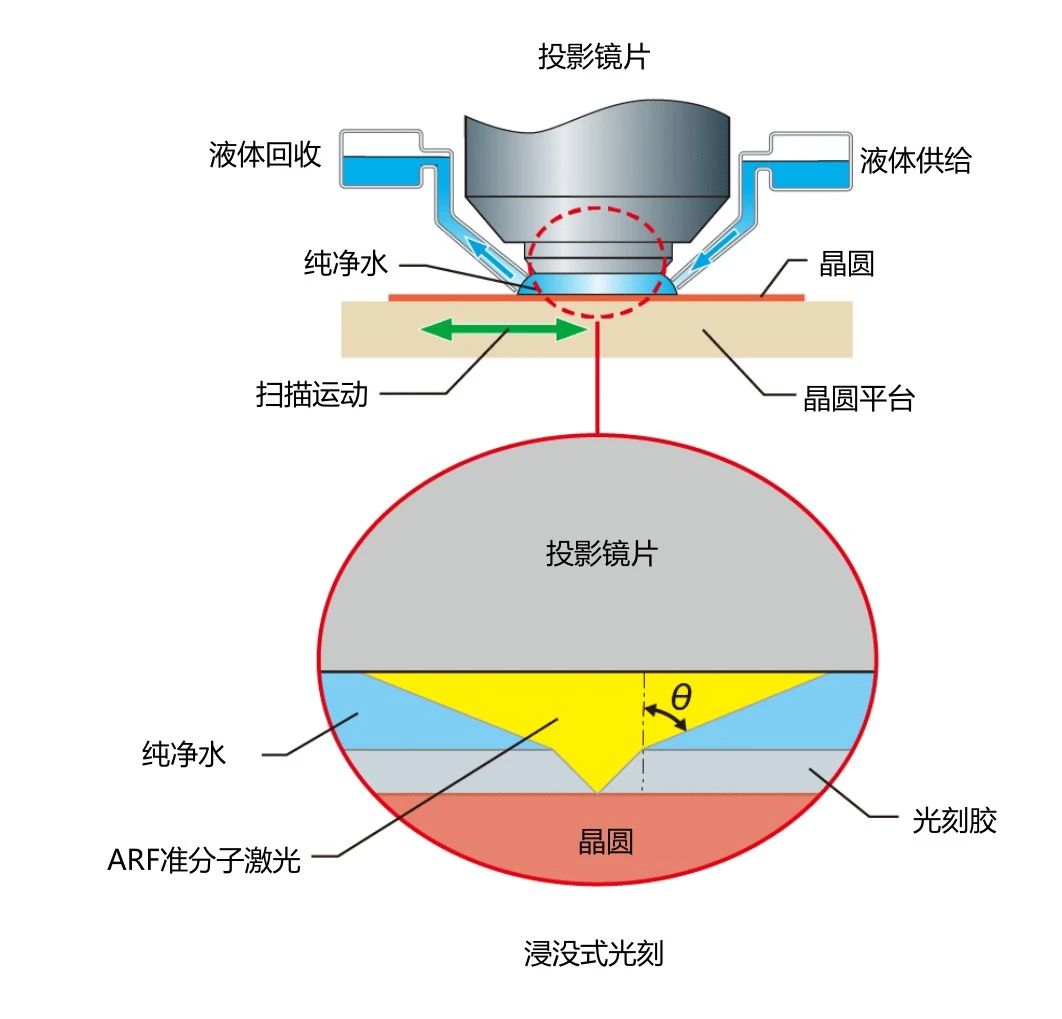

(1)相移掩膜 PSM

相移掩模(phase-shifting mask)原理如图:

传统的掩模,每个缝隙处电场的相位都相同,如图(a)所示。光学系统的衍射与分辨率的限制使得晶圆上的电场分布散开,如图中虚线所示。相邻缝隙处的衍射波相互干涉,增强了两者之间的电场。由于光强度I与电场的平方成正比,因此,若两个图形靠得很近,经过投影后就很难分辨了。将相移层覆盖在相邻缝隙处,则可以使其电场方向相反,如图(b)所示。因为掩模上的光强度未改变,晶圆上图形的电场可被抵消,所以两个靠得很近的图形也可以清晰地分辨。180°的相位变化可以通过在缝隙处添加一个厚度为d=λ/2(n-1)的透明层得到,其中n是折射系数,λ是波长。

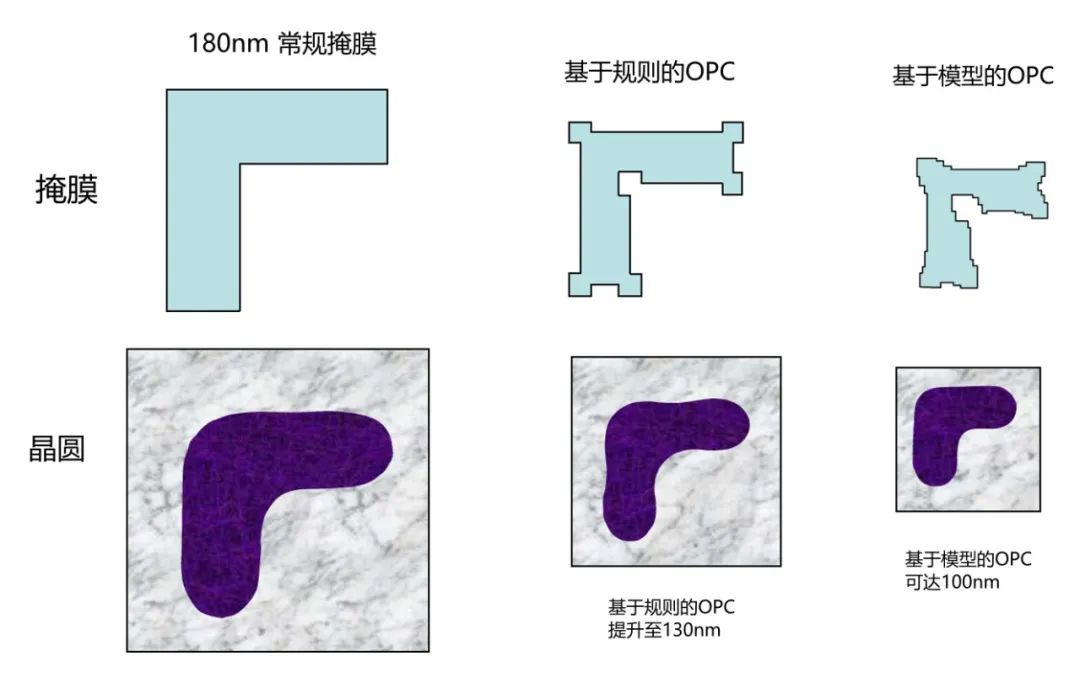

(2)光学邻近效应矫正 OPC

光学邻近效应校正(optical proximity correction)是通过采用对邻近区域修正过的图形来提高图像的质量,可用于在一定程度上补偿衍射效应。

例如,若接近分辨率极限的方形接触孔刻出来像一个圆孔,则可在掩模方形接触孔的拐角处对图形进行修正,使它刻出来成为一个准确的方孔。

OPC还分为基于规则和基于模型两种:

图源:https://slideplayer.com/slide/5732688/

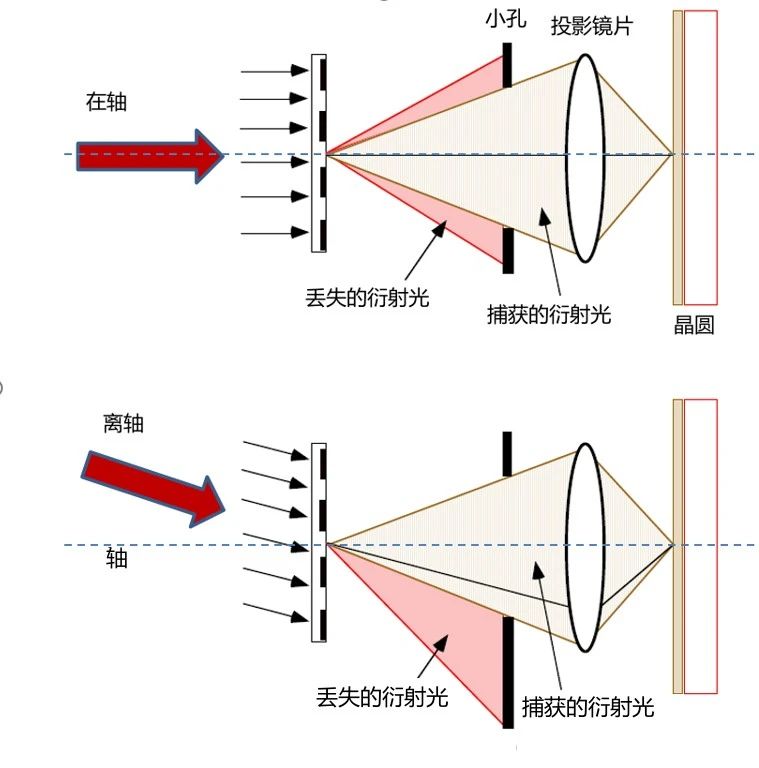

(3)离轴照明

离轴照明即光源不在轴上:

图源:https://slideplayer.com/slide/5732688/

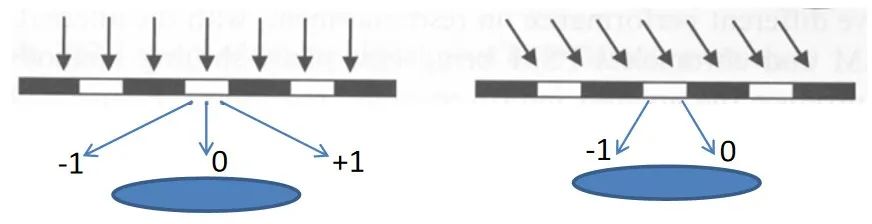

“离轴照明”允许捕获一些高阶衍射光,从信息光学的观点看,掩模图形经投影物镜成像时,由于投影物镜的数值孔径有限,高频部分不能进入光瞳对成像无贡献,使硅片面上的掩模像的对比度降低,影响成像质量。由于0级衍射光不包含掩模图形的任何空间调制信息,所以要对掩模图形成像至少要包含1级衍射光。在投影曝光系统中掩模图形的空间像的对比度依赖于投影物镜中参与成像的1级衍射光的比例。离轴照明技术通过降低成像光束中的低频成分来提高高频成分在总光强中的比例从而提高了空间像的对比度,同时还可以提高焦深。

图源:https://slideplayer.com/slide/5732688/

在IC工业中,仅收集m=0和+1(或-1)级衍射光。无需二阶。上图左边仅仅收集到了0阶衍射光,右边有了离轴照明后,可以收集到0阶和1阶衍射光。

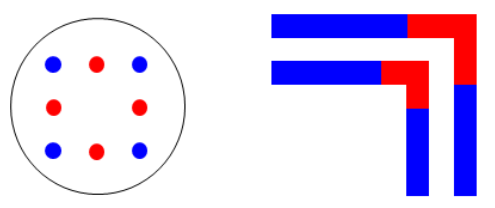

离轴照明的形式有多种,比如下图中的环形照明和四极照明:

图源:https://slideplayer.com/slide/5732688/

四极照明:对于线/空间图案最有效(取决于线方向,最适合垂直或水平线/空间图案),对于孤立特征效果较差。

环形照明:分辨率增强较少,但与方向无关。

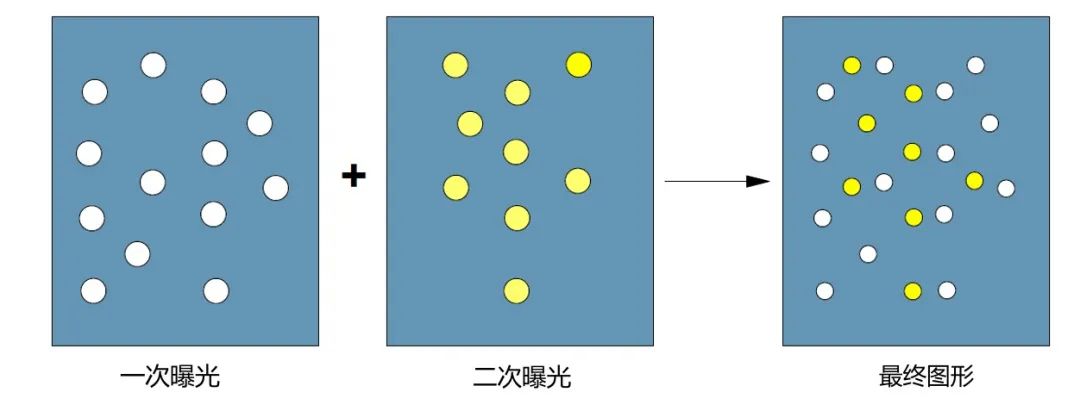

(4)双重曝光

双重曝光是将掩模上的图案分成两个掩模,从而使特征之间有更大的分离。使用两个掩模将光刻胶曝光两次。

图源:https://slideplayer.com/slide/5732688/

双重曝光的另一个优势是:同一布局中的不同特征(如不同颜色所示)可能需要不同的照明,因此需要不同的曝光。

图源:维基百科

虽然水平线和垂直线可以使用普通的四极照明(蓝色)来解决,但 45 度方向会受到影响,因为它们需要完全不同的四极照明(红色)。因此,要包括所有这些情况,需要单独曝光。

尽管上述的相移掩模、光学邻近效应校正、离轴照明等方法能弥补光学曝光的不足,但人们也在寻找新的曝光方法来完成纳米级的集成电路制造,比如电子束曝光、X射线曝光、离子束曝光、极紫外曝光等。此部分内容在下一篇中介绍。

滤波器 微信公众号

审核编辑:黄飞

-

光刻胶的类型及特性2025-04-29 10474

-

光刻掩膜设计与加工制造服务,请问可以加工二元光学器件吗?2024-04-22 548

-

【「芯片通识课:一本书读懂芯片技术」阅读体验】芯片怎样制造2025-04-02 4030

-

Futurrex高端光刻胶2010-04-21 3982

-

三种常见的光刻技术方法2012-01-12 11442

-

Microchem SU-8光刻胶 2000系列2018-07-04 4812

-

光刻胶2018-07-12 2984

-

光刻胶在集成电路制造中的应用2018-08-23 7421

-

光刻胶有什么分类?生产流程是什么?2019-11-07 4372

-

光刻机工艺的原理及设备2020-07-07 17525

-

掩膜版与光刻胶的功能和作用2024-09-06 2982

-

一文看懂光刻胶的坚膜工艺及物理特性和常见光刻胶2024-11-01 3453

-

光刻掩膜技术介绍2025-01-02 6466

-

芯片制造:光刻工艺原理与流程2025-01-28 4743

-

光刻胶剥离工艺2025-09-17 2395

全部0条评论

快来发表一下你的评论吧 !