如何实现基于FPGA的低成本安防雷达设计呢?

描述

系统架构

1.硬件设计简述

1.1 天线

1.1.1天线设计指标:

频率:5.4-5.6GHz

相邻阵元隔离度:不大于55dB

与校正通道耦合度:30dB

驻波:不大于1.2

阵元数:12

俯仰波束角:20°

水平波束角:10°

天线增益:21.8dB

1.1.2 天线仿真结果分析:

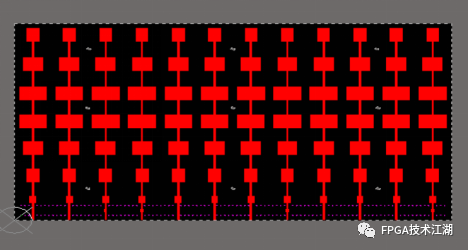

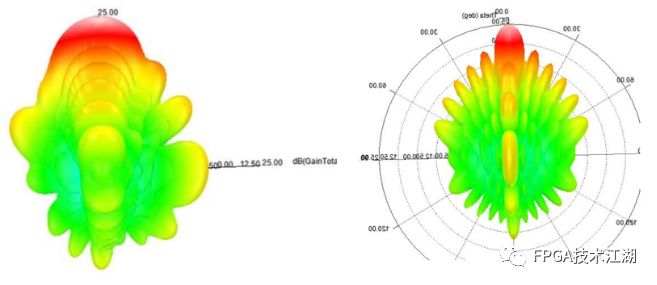

整个有源阵列天线尺寸为38×12cm,波束水平宽度约为10°,通过改变相移可实现波束扫描,即可覆盖前方±45°范围。

阵列天线的波束宽度理论上会随波束指向角的变化而变化。下图为12个阵元微带天线不同指向角对应的波束宽度变化曲线。

图3-1 12阵元理论波束宽度与角度关系

图中可以看出,法线方向时,对应的波束宽度最窄,为9.236°,±45°时对应的波束宽度最大,为13.6°。

图3-2 天线结构图

图3-3 天线3d俯仰面截图与水平面截图

1.2 雷达板卡

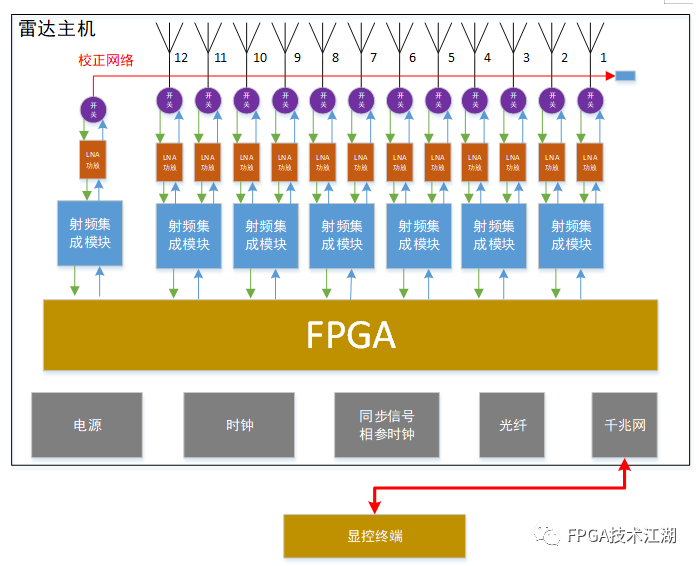

雷达板卡组成框图如图3.3所示。其中射频综合处理模块包括了12个射频收发通道和1个收发校正通道。

FPGA主要实现整机时序控制、波形产生、幅相校正、DBF、脉压等功能,最终的FPGA数据通过千兆以太网输出。

图3-4 C波段雷达板卡结构图

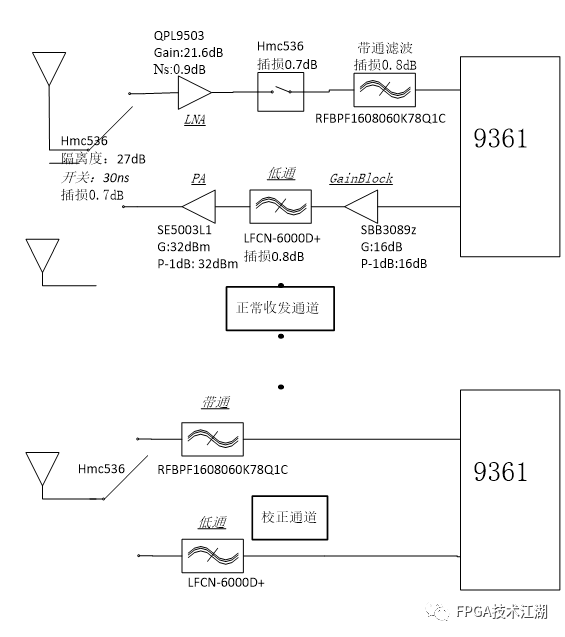

射频集成模块采用无线电标杆产品AD9361。而每个芯片都集成了两路12位的ADC和DAC用作收发,并且AD9361的每个通道均支持时分双工和频分双工两种模式。

千兆网用于上传最终的处理结果,而光纤用于调试阶段上传更多的原始数据或中间处理结果。

其中本雷达的射频前端主要指标如下表:

表3-1 射频前端指标表

| 技术参数 | ||

| 接收通道 | 发射通道 | |

| 频率要求 | 5500MHz | 5500MHz |

| 最大增益 | 20dB | 45dB |

| 输出功率 | -10dBm | 27dBm |

| 隔离度 | 54dB | |

根据框图中的指标设计链路如下:

图3-4 收发链路方案设计图

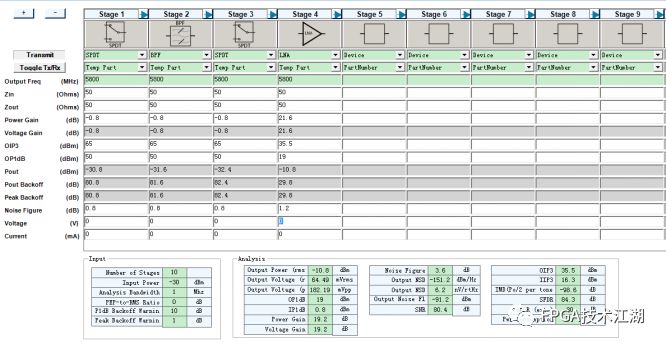

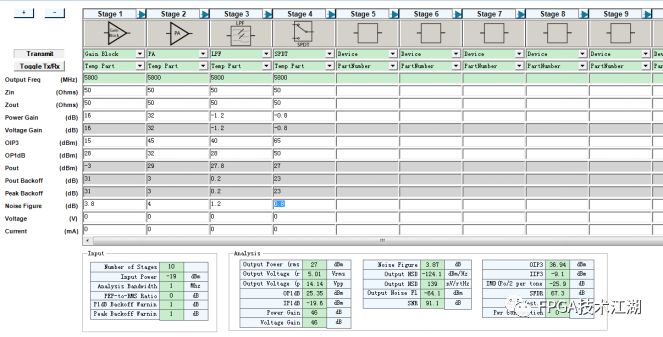

使用ADI的性能链路仿真软件计算如下:

图3-5 接收链路仿真图

图3-6 发射链路仿真图

由上图可以看出,接收通道噪声系数3.6dB,总体增益大约19.2dB。发射链路中,仿真建立AD9361的输出功率是-19dBm,链路增益增益45dB,最后输出功率27dBm,达到预期目标。

2 基于ZYNQ的信号处理

2.1 收发通道校准

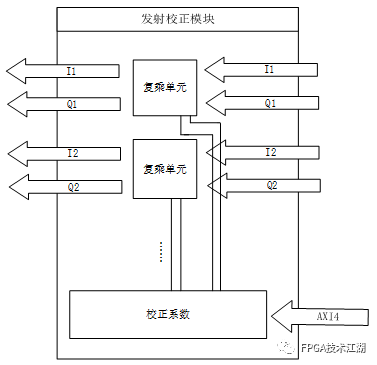

由于雷达收发信号为IQ信号,所以校准因子也就是一个复数的因子,也就是说校准过程也就是一个复数乘法的的过程。由于接收校准和发射校准只是数据流的方向相反,所以下面的介绍只以发射校准为例。

在校准模块内部,每一路发射通道的IQ数据被送入一个复数乘法器,与之前存储在模块内部的校准因子相乘,并将计算结果送出,结构如图。

图3-7 发射校准模块

2.2 数字波束形成

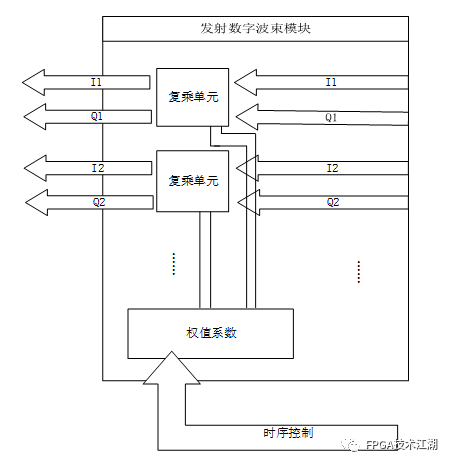

数字波束合成分为发射数字波束合成和接收数字波束合成两个部分。

发射数字波束合成是对发射校准模块输入的多路信号进行加权运算,运算方式是与权值系数进行复乘。权值系数总共9组,每一组对应一个波位,循环使用这9组权值系数,就可以完成波束的扫描,也就实现了相控阵的功能。其结构如下下图。

图3-8 发射数字波束合成

接收数字波束合成是对接收校准模块输入数据进行加权运算,对12路接收数据同时进行两组加权运算,得到2路的数据输出,每一路数据对应当下波位内的一个波束,通过同一个波位内的两个波束,可以完成比幅测角的运算。

接收数字波束合成模块的工作方式及流程与发射数字波束合成大体上相同,不同的是接收数字波束合成模块具有18组权值系统,每2组构成同时工作的一对,即总共有9对权值系数。其结构与发射数字波束合成相似。

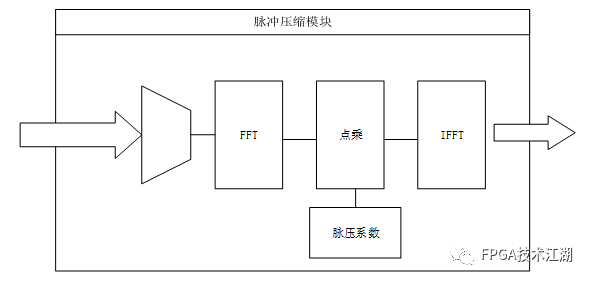

2.3 脉冲压缩

因为发射数据为线性调频信号,所以数据接收回来后,需要进行脉冲压缩处理。在脉冲重复周期100us,采样率10M的情况下,每一包数据具有1000个点,约10us的脉宽有100点的脉压系数。

因为点数较多,使用时域卷积的方式效率会比较低,因此选用频域点乘方式。

输入数据首先做一个1024点的FFT,将数据变到频域,然后与频域的脉压系数进行点乘(频域的脉压系数是事先将时域脉压系数做1024点FFT得到的),计算结果就是脉压后频域的数据,最后将计算结果输入到1024点逆FFT的核中,得到时域的数据。

结构如下图。

图3-9 脉冲压缩模块

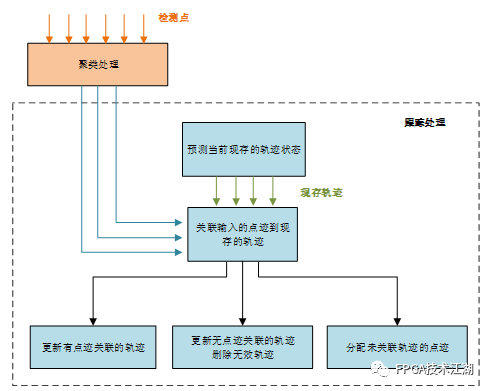

3 上位机数据处理(目标跟踪算法)

图3-10 目标聚类和跟踪算法的实现流程

跟踪算法输入为聚类处理结果,采用卡尔曼滤波器完成目标跟踪,跟踪目标的X/Y坐标及X/Y向速度。

本应用中使用的是经典的卡尔曼跟踪算法,采用的是恒速度模型,该算法较为成熟,在此不再赘述。

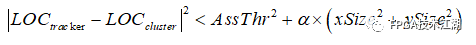

但匹配原则较为重要,简述于下: 对于每个聚类结果,都需要将其与现存的轨迹进行匹配,综合考虑目标尺寸变化问题,匹配规则如下: 式中

式中 分别为预测轨迹位置、聚类结果位置和关联半径,

分别为预测轨迹位置、聚类结果位置和关联半径, 分别为目标的X、Y向尺寸,

分别为目标的X、Y向尺寸, 为尺寸权系数。只要聚类结果落在以轨迹预测位置为中心的半径为关联半径的圆内,即认为该聚类结果关联至该轨迹。

为尺寸权系数。只要聚类结果落在以轨迹预测位置为中心的半径为关联半径的圆内,即认为该聚类结果关联至该轨迹。

若多个聚类结果被匹配至同一轨迹,这些聚类结果将被合并至一点,再更新轨迹,包括该轨迹的所有状态;若某条轨迹本帧内未被关联,则按照预测结果填补本帧结果,并开始失配计数,若直至达到失配阈值,也没有新的聚类结果被关联至该轨迹,这条轨迹将被删除;若某个聚类结果未被关联至任何轨迹,则本次将新建一条轨迹,并开始激活计数,直至激活计数值大于激活阈值,这条轨迹将被激活,算作有效轨迹。

有效轨迹将被显示至显示屏,以供决策人员决策。 经过上述一系列算法处理之后,我们已经能够成功检测出目标并建立航迹,只需按照特定的数据协议通过udp传送到显控终端,由终端对航迹进行相应地绘制。

设计演示

1.测试方法

测试时使用大疆精灵4无人机(截面积0.01m2)做为测试目标,以城市环境为背景,将雷达架设在露天阳台。无人机在飞手遥控下,从雷达架设点起飞,飞至遥控信号所能达到的最远距离,然后返航(由于城市中电磁环境复杂,飞行器最远飞行距离也不会超过1000m)。 无人机飞行时,通过上位机软件观察无人机飞行的点迹和航迹,同时将来自雷达前端的数据保存在电脑中,测试后再由MATLAB对保存数据进行分析、寻找问题,以此来提高雷达探测性能。

同时还要通过多次的重复实验,来寻找设计中存在的漏洞。且雷达前端设计时参数灵活多变,可以在线更改,所以需要通过实验找一组合适的雷达参数,作为今后无人机探测模式去使用。下图为测试环境的照片。

图4-1 雷达现场测试环境

2.测试结果

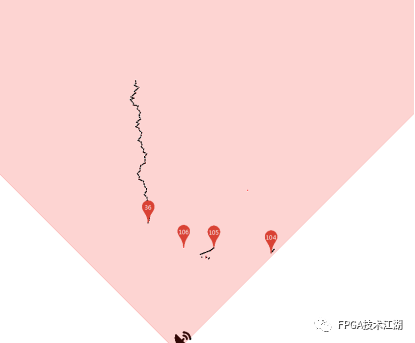

通过上位机软件,可以看到无人机连续的航迹,无人机从飞出盲区直到最远飞行距离都可以连续跟踪。如下图为无人机返航时的航迹,大约从960m无人机返航处开始建立航迹,直到飞入雷达盲区,航迹连续。

图4-2 建立航迹和连续追踪

图中除了无人机的航迹外,还有一些杂点存在,这是由于城市中电磁环境复杂,且有高楼这样的强反射体的存在,导致有很大的地杂波。地杂波虽然本身为静目标,但是由于相位噪声的影响,会使大幅度的回波信号有着更大的起伏,最终导致MTD后静目标从零通道扩散到其他多普勒通道。大部分杂点在此后通过优化上位机的算法,在建立航迹时可以去除掉。

3.结果分析

因为雷达的探测距离超过了无人机最远飞行距离,所以需要对现有测试条件的数据,进行分析和仿真,来计算出雷达对于小型无人机的最远探测距离。

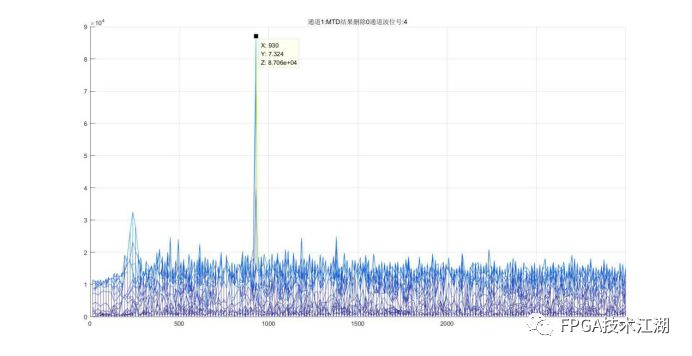

图4-3 雷达MTD结果显示

上图中为MTD的结果,最高的尖峰为无人机,X轴为距离,Y轴为无人机速度,Z轴为信号幅度。从图中可以看出,无人机与雷达的距离为930m,速度为7.324m/s。通过计算求得目标在此距离下的信噪比为21dB。

由雷达方程知,目标信噪比与目标距离的四次方成反比,如下式。

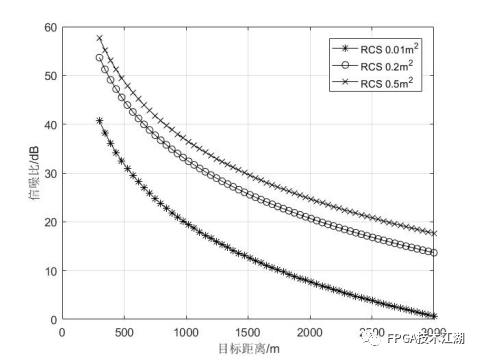

其中k为比例常数,包含如天线增益、目标RCS等多种因素,在完整的雷达方程会被拆解成多项。通过上图中的信噪比和目标距离,可以估算此环境下的k值,然后再代入上式,可得如下结果。

图4-4 信噪比与目标距离关系图

以13dB信噪比作为雷达检测门限,RCS为0.01的大疆精灵4探测距离可以达到1470m;RCS为0.2的小型无人机,探测距离可以达到3000;对于RCS为0.5的行人,探测距离可以达到3000m以上。

结论得出,是以一次较好的实验效果为基础,由此估计所得的雷达威力一定会偏高,在改变实验条件或实验环境更加恶劣时,不一定能达到所估算的威力。所以此次雷达威力的估计是一个较优的值,而不是稳定可以达到的值。 如果实验环境改为电磁环境干净,且较为空旷的野外,由于杂波干扰相对城市环境少很多,所以一定会得到更远的探测距离。

审核编辑:刘清

-

纳雷科技安防雷达可与Avigilon视频管理系统无缝集成2025-12-31 800

-

低成本毫米波雷达系统设计与研发2023-11-14 1603

-

怎么实现一种低成本微型测距雷达的设计?2021-05-12 1810

-

如何利用FPGA实现低成本汽车多总线桥接?2021-04-29 1461

-

怎么利用FPGA和嵌入式处理器实现低成本智能显示模块?2021-04-28 1601

-

安防雷达散热,选择什么材料好2021-04-23 877

-

英飞睿发布的T/R组件及天线主要针对相控阵安防雷达应用2021-02-20 8382

-

阿里达摩院实现低成本激光雷达,自动驾驶技术再升级2020-08-14 1393

-

国内毫米波安防雷达应用篇——木牛WAYV雷达助力智慧安防2020-05-06 3198

-

什么是Altera系列低成本Cyclone IV FPGA?2019-07-31 4480

-

高效、低成本的 FPGA 器件:Spartan-7 FPGA!2017-11-16 10473

-

采用低成本FPGA实现高效的低功耗PCIe接口2013-02-26 1251

-

在低成本FPGA中实现动态相位调整2010-03-25 3164

-

基于FPGA的低成本AES IP核的设计与实现2010-01-06 708

全部0条评论

快来发表一下你的评论吧 !