AMD FPGA的MicroBlaze固化过程详解

描述

一、简介

MicroBlaze是AMD FPGA推出的一款32/64位软核嵌入式处理器,其高度可配置,可满足通信、工业、医疗、汽车、以及消费类各场景需求。MicroBlaze是AMD FPGA嵌入式产品的重要组成部件,具有多功能互联系统,可支持各种嵌入式应用。

MicroBlaze的易用性使得其开发如AMD其它嵌入式SoCFPGA一样简单。客户在搭建含MicroBlaze IP的工程后,经常遇到的问题是,如何将.bit文件与应用程序.elf文件结合,固化到存储器件中(一般指串型/并行FLASH)。下面将结合原理与固化过程,详细描述此问题。

二、疑难理解

首先,要理解的一点是,AMD FPGA在配置了适当的启动模式后,上电即会按该模式去加载配置文件。以7系列FPGA为例,假设设置模式引脚M[2:0]=3’b001,上电后FPGA会以MasterSPI方式尝试从FLASH加载配置文件,其与工程是否含有MicroBlaze IP无关。其次,客户经常遇到的问题是,含MicroBlaze IP的工程中,需要考虑程序的运行地址空间(涉及DDR MIG IP);需要考虑应用程序的加载(涉及AXI Quad SPI IP),在固化时某些选项配置错误,导致系统无法启动。

三、固化过程详解

思考一个问题,在含有MicroBlaze的设计中,DDR MIG IP和AXI Quad SPI IP必须同时存在吗?带着这个疑问,下面详细讲解MicroBlaze两种应用场景下的固化过程。演示过程以7系列FPGA器件,以vitisv2022.2版本工具,以SPI FLASH存储器件为例,其它系列器件和工具版本类似。

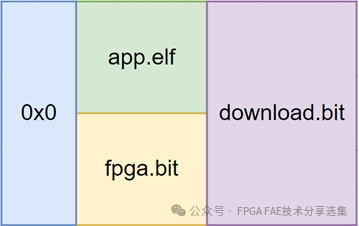

场景一,MicroBlaze运行简单的应用。如GPIO控制,IIC、UART等低速嵌入式总线应

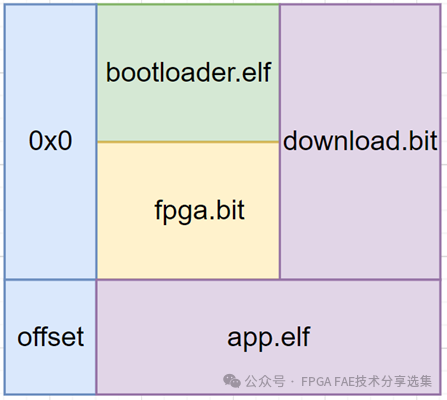

用,或者负责一些复杂IP和外围IC的初始化辅助性工作。此时,FPGA固化固件组成形式如下图所示。

在这个场景下,vivado生成的fpga.bit文件和vitis生成的应用程序app.elf文件,合并为download.bit文件,烧录到FLASH的起始地址0x0中。此设计中,不需要借助AXI Quad SPI IP的应用搬运能力,对是否含有DDR MIG IP也无要求。下面展示该固化流程:

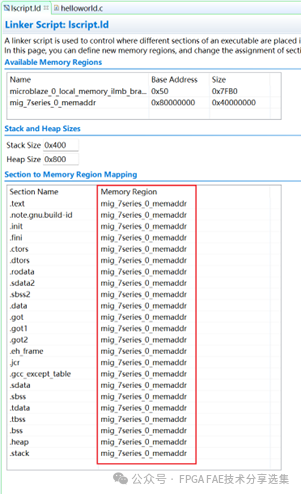

为增加迷惑性,设计中含有DDR MIG IP。vivado生成.bit文件后,导出.xsa文件,创建vitis软件工程。应用程序的ld脚本默认Memory Region Mapping指向外部DDR。

点击Program Device菜单生成download.bit文件将出现address mapped error错误,无法生成download.bit文件。

注意:

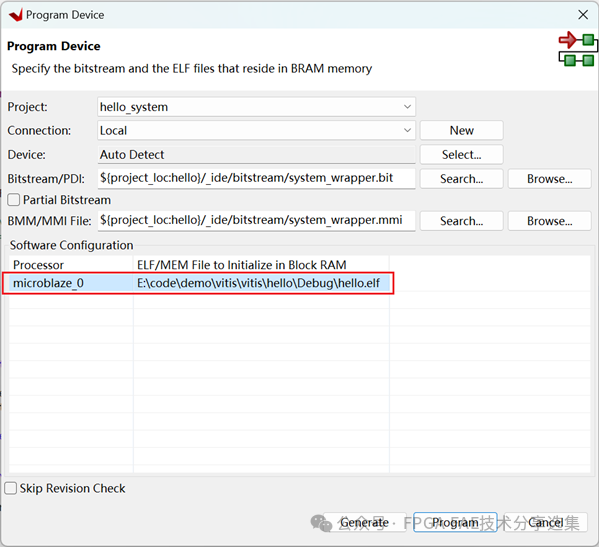

需要选择应用程序生成的.elf文件(如图示的hello.elf文件),而不是vitis默认的bootloader。

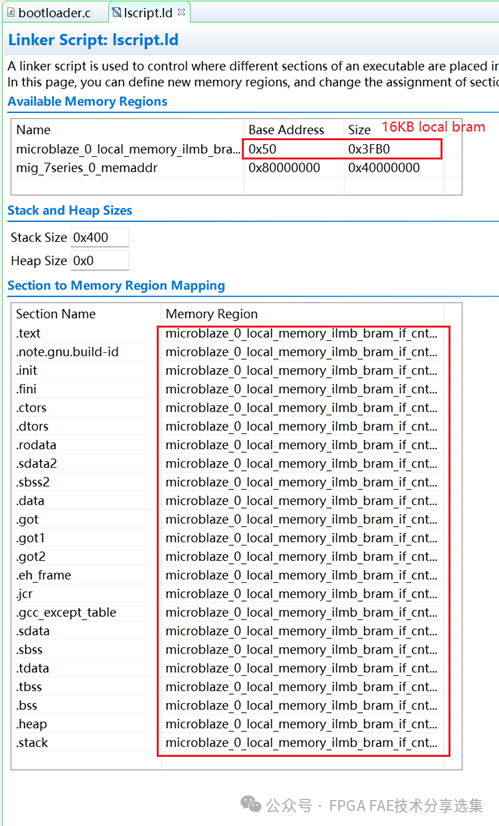

此时需要修改工程ld脚本文件,将MemoryRegion Mapping设置为local bram,如下图所示

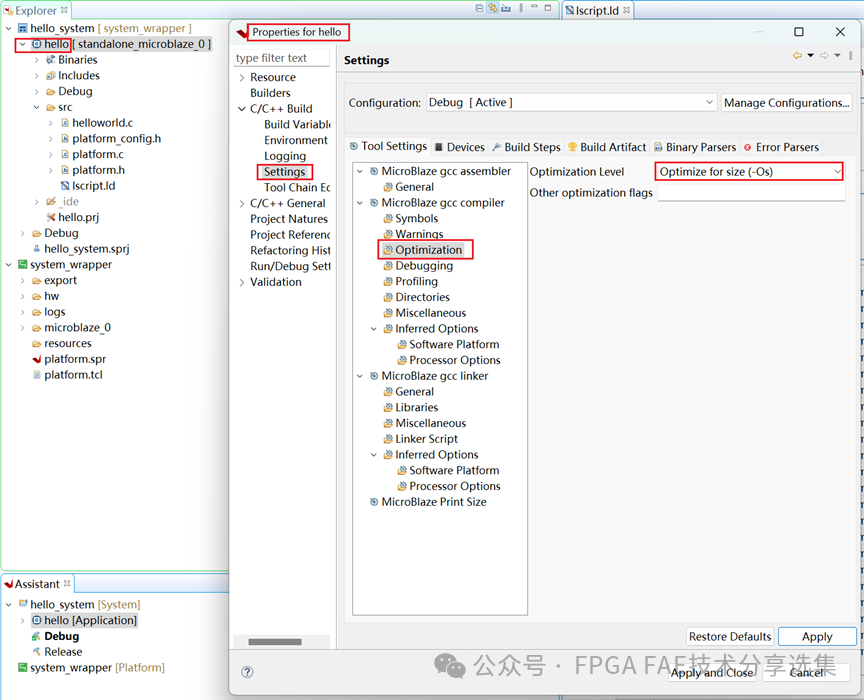

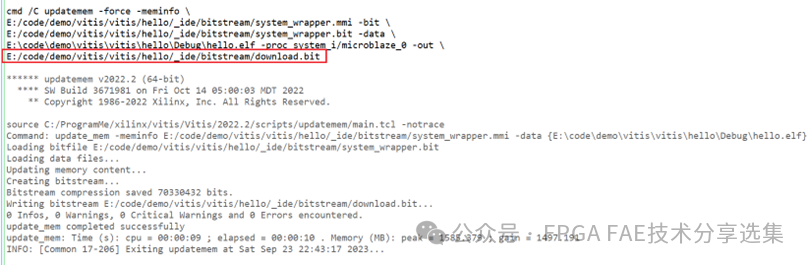

再次点击Program Device菜单生成download.bit文件即可。由于一般情况下,为节省FPGA block ram资源,用于MicroBlaze的local bram并不会设置很大,可使用下图所示优化选项,减小固件的大小。

生成download.bit文件后,JTAG模式下,烧录固件到FLASH中,注意Offset项为0x0。

烧录过程log记录:

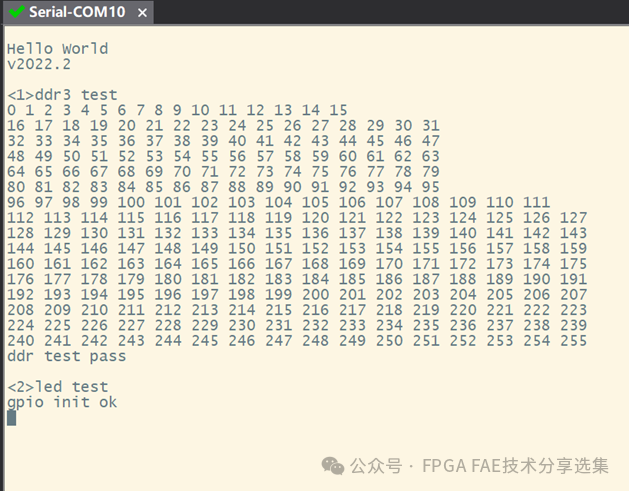

断电,将启动模式设置为Master SPI,系统启动log如下:

上述展示了一个简单的应用程序的固件固化过程。

场景二,MicroBlaze运行复杂的应用。如轻量级的网络协议栈LwIP,加载嵌入式文件

系统等。此场景一般生成的固件达到MB级别,对内存也有一定需求,需要借助DDR来运行应用程序。此时,FPGA固化固件组成形式如下图所示

在这个场景下,vivado生成的fpga.bit文件和vitis生成的应用引导程序bootloader.elf文件,合并为download.bit文件,烧录到FLASH的起始地址0x0中;复杂的应用程序app.elf文件,烧录到FLASH的指定offset地址中。

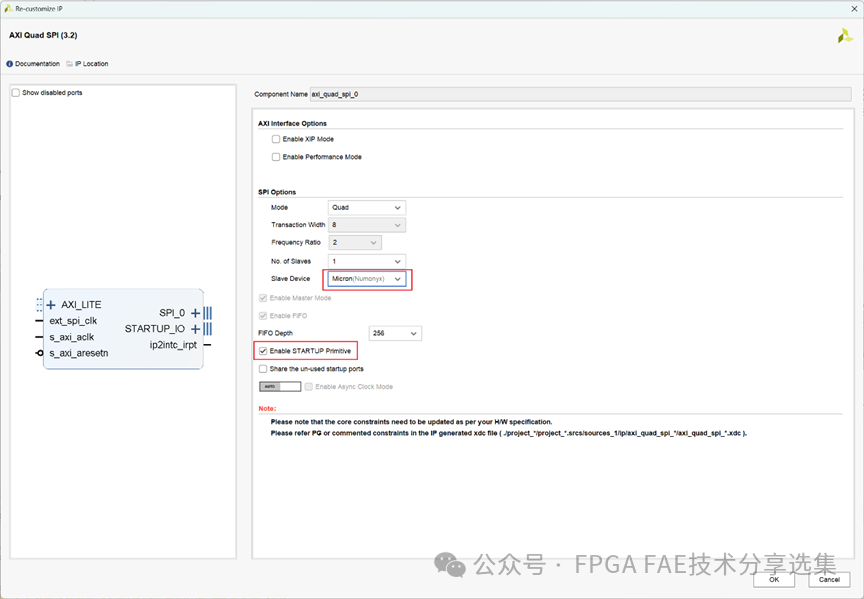

此设计中,必须借助AXI Quad SPI IP的应用搬运能力,复杂应用程序一般对DDR也有要求,也即设计需要DDR MIG IP。下面展示该固化流程:

首先在vivado中,需要对AXI Quad SPI IP做正确的设置,选择FLASH的型号,使能STARTUPPrimitive选项。

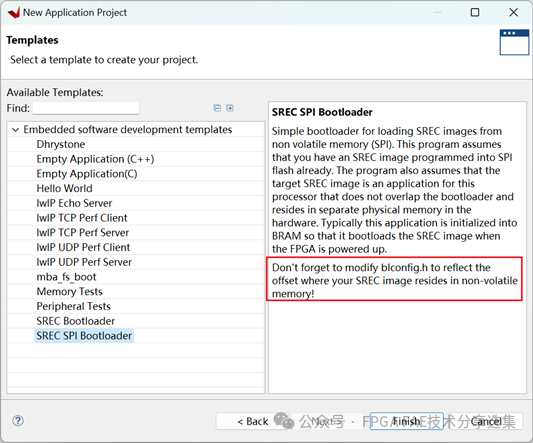

然后创建bootloader引导工程,如下

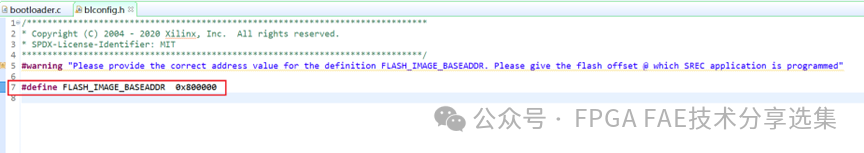

vitis工程引导界面提示修改合适的应用程序offset address。

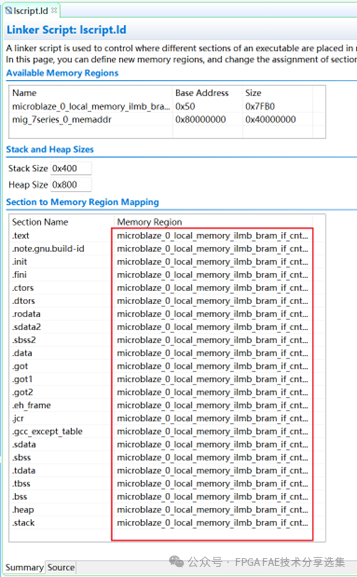

查看bootloader工程的ld脚本,确定bootloader工程的Memory Region Mapping指向为local bram。

同时需要修改应用程序在FLASH中的程序地址,根据FLASH的容量大小,选择合适的偏移地址。这里修改为0x800000(起始地址偏移8MB空间)。

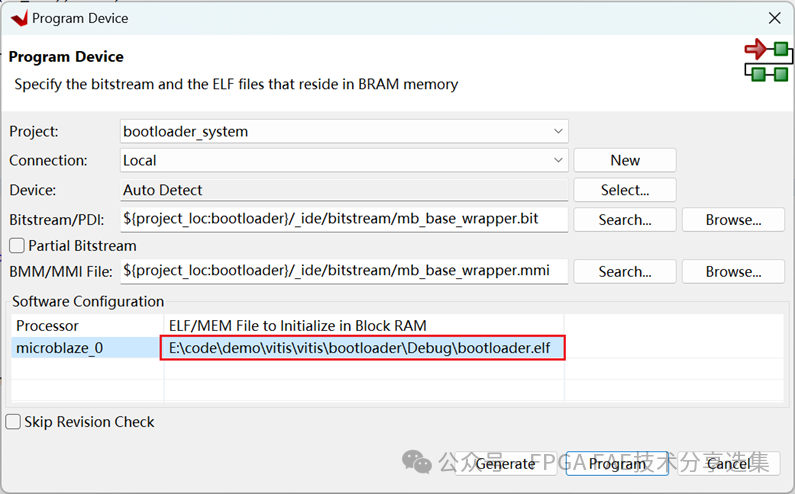

点击Program Device菜单生成download.bit文件,注意选择的是bootloader.elf文件。

备注:

vitis IDE中,此菜单项包含Generate和Program选项,一般JTAG未连接板卡时选择Generate选项;连接JTAG在线调试时,选择Program。但是无论是否连接JTAG,两个选项都能生成download.bit文件。

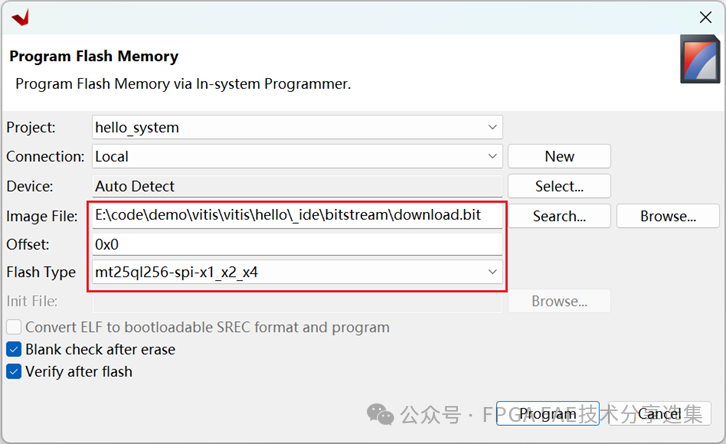

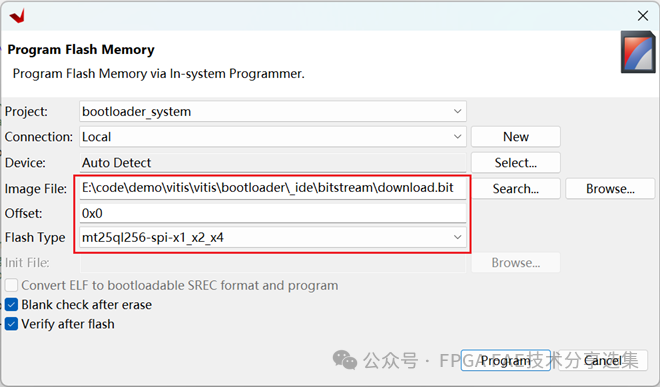

将生成的download.bit文件烧录到FLASH的0x0地址中。

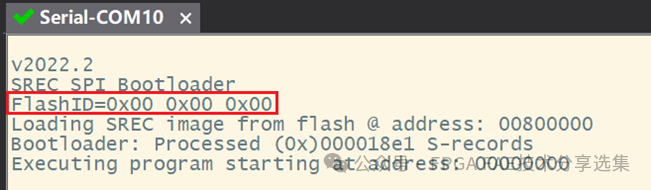

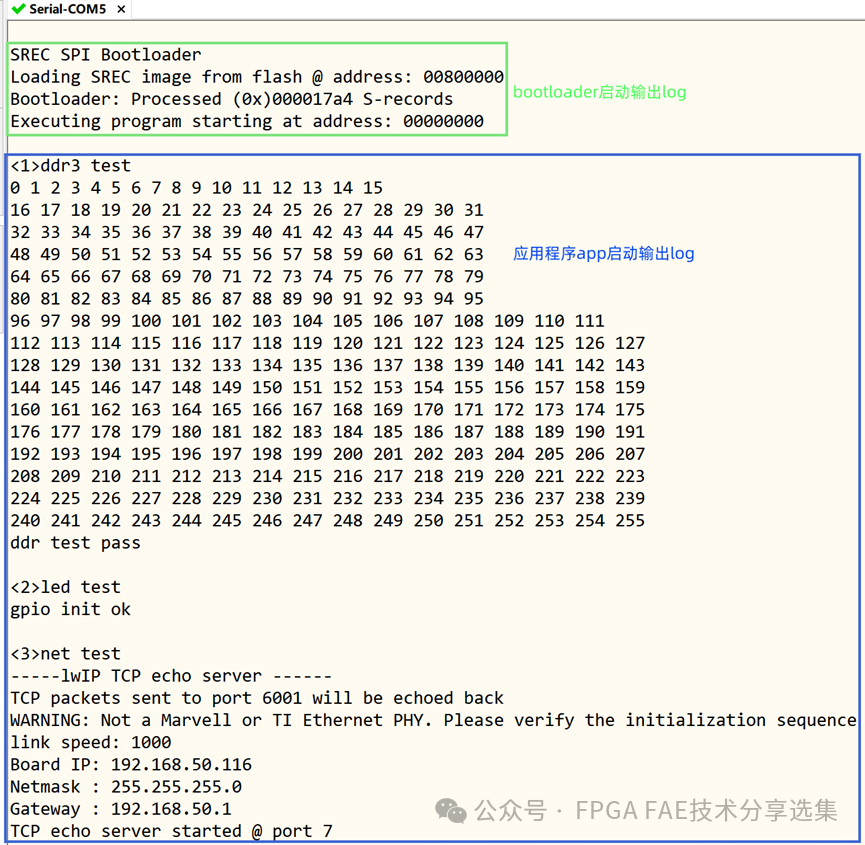

断电,将启动模式设置为Master SPI ,可验证bootloader是否烧录成功,其启动log如上。

log显示bootloader将从00800000地址中加载应用程序固件,证明bootloader烧录成功。

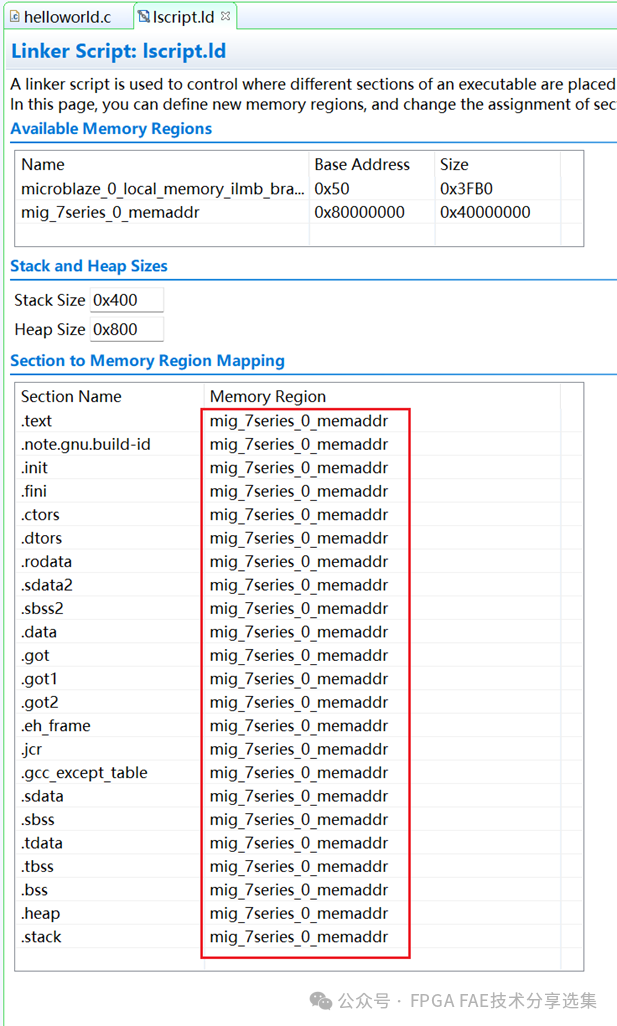

接下来创建应用工程,应用工程较复杂,所需运行内存较大,应用工程的ld脚本文件Memory Region Mapping指向外部DDR。

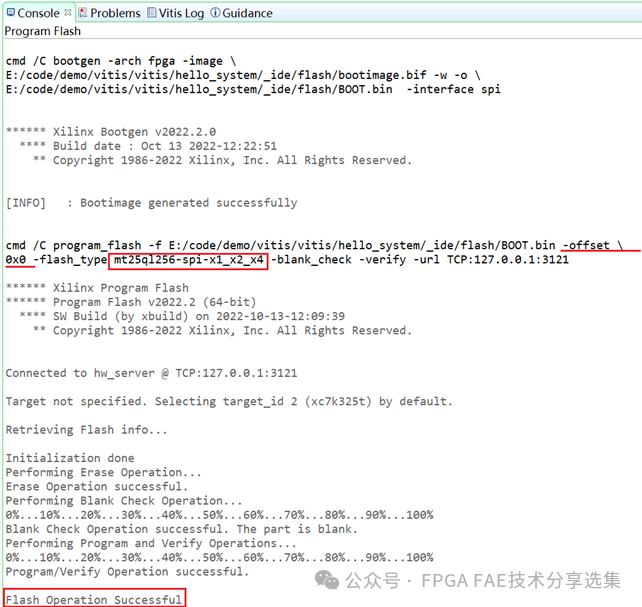

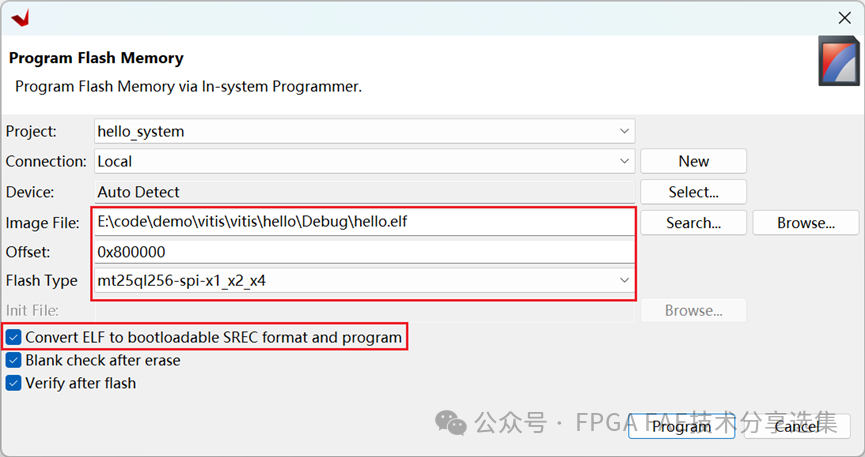

点击Program Flash Memory菜单,将应用程序hello.elf烧录到FLASH中,注意Offset项为之前bootloader工程设置的0x800000,且需要勾选SREC转换选项。

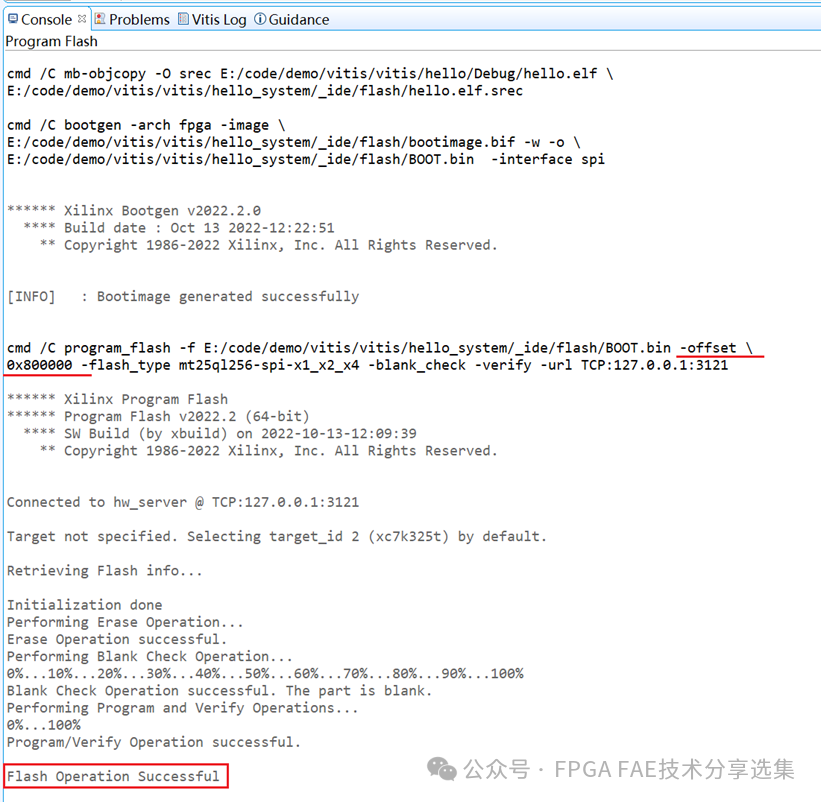

烧录过程输出log记录。

断电,将启动模式设置为Master SPI,系统启动log如下:

上述演示了一个稍复杂的应用程序的固件固化过程。

四、总结与拓展

1. 通过烧录过程可发现,场景二的bootloader引导应用程序即相当于场景一的用户程序;

2. 场景二的系统启动速度相对场景一较慢,AMD FPGA提供了一种加速方法,详细参考

https://support.xilinx.com/s/article/75646?language=en_US

3. 从2019.2版本工具开始,FLASH的驱动程序发生了变更,详细参考

https://support.xilinx.com/s/article/73329?language=en_US

4. 从SDK到Vitis,上述固化过程原理不变,但一些菜单选项细节稍有不同;

5. 从UltraScale系列开始支持的SPIx8模式,细节上有一些区别,详细参考官方手册UG570。

审核编辑:刘清

-

AMD FPGA中MicroBlaze的固化流程详解2024-04-25 1604

-

FPGA的PL端固化流程2024-03-07 621

-

MicroBlaze MCS和MicroBlaze的区别在哪?2023-08-23 2467

-

TI AM57X FPGA MicroBlaze裸机案例开发2022-05-23 1080

-

FPGA+MicroBlaze裸机程序加载与固化2021-12-29 1373

-

采用FPGA和MicroBlaze进行嵌入式系统设计2021-02-22 1790

-

如何使用PowerPC或Microblaze重新配置FPGA?2019-01-22 2215

-

Virtex-5中的Microblaze和Capture-Restore过程出现问题2019-01-10 2991

-

关于使用232下载固化FPGA程序,寻求外包2018-10-11 2701

-

MicroBlaze性能详解2017-11-25 9115

-

基于MicroBlaze处理器的BPIFlash操作2017-11-17 6031

-

【Artix-7 50T FPGA试用体验】Vivado程序固化2016-12-27 20009

-

基于MicroBlaze软核的FPGA片上系统设计2009-06-20 3690

-

基于MicroBlaze 软核的FPGA 片上系统设计2009-04-15 721

全部0条评论

快来发表一下你的评论吧 !