SOPC的嵌入式软硬件协同设计平台实现

嵌入式设计应用

描述

片上可编程系统(System On a Programmable Chip,SOPC)是Altera公司提出来的一种灵活、高效的SoC解决方案。SOPC是一种特殊的嵌入式系统:首先,它是系统芯片SoC,即由单个芯片完成整个系统的主要逻辑功能;其次,它是可编程系统,具有灵活的设计方式,可裁剪、可升级、可扩充,并具备软硬件在系统可编程的功能。它结合了SoC和FPGA的优点,具有以下基本特征:至少包含一个以上的嵌入式处理器IP(Intellectual Property,知识产权)核,具有小容量片内高速RAM资源,丰富的IP核资源可供灵活选择,有足够的片上可编程逻辑资源,处理器高速接口和FPGA编程接口共用或并存,可能包含部分可编程模拟电路,单芯片、低功耗。

本文主要研究的是应用嵌入式系统开发的软硬件协同设计方法来实现一个集软核处理器的嵌入式设计平台,在此基础上,如有必要还可集成嵌入式操作系统。

1 基于SOPC软硬件协同设计方法

SOPC设计技术实际上涵盖了嵌入式系统设计技术的全部内容,除了以处理器和实时多任务操作系统RTOS为中心的软件设计、以PCB和信号完整性分析为基础的高速电路设计技术以外,SOPC还涉及目前已经引起普遍关注的软硬件协同技术。

1.1 软硬件协同设计模型

目前的软硬件协同设计是指软硬件的设计同时进行,在系统的初期阶段两者就紧密相连。软硬件协同设计不仅是一种设计技术,同时也是一种新的设计方法和思想,它的核心问题是沟通软件设计和硬件设计,避免系统中关系密切的两部分设计过早独立。同传统设计方法相比,软硬件协同设计提高了设计抽象的层次,并拓展了设计的覆盖范围。采用软硬件协同设计技术可以使嵌入式系统设计更好和更快。

软硬件协同设计在其研究和生产实践过程中,提出了很多的设计模型。这些模型都是把系统功能转换成组织结构,将抽象的功能描述模型转换成组织结构模型。由于针对一个系统可以建立多种模型,因此应根据系统的仿真和先前的经验来选择模型。

软硬件协同设计流程从目标系统构思开始。对一个给定的目标系统,经过构思,完成该系统的规范描述,然后是模块的行为描述、对模块的有效性检查、软硬件划分、性能评估、硬件综合、软件编译、软硬件集成、软硬件协同仿真与验证等各个阶段。其中软硬件划分后产生硬件部分、软件部分和软硬件接口3个部分。硬件部分遵循软件描述、软件生成和参数化的步骤,生成软件模块,最后把生成的软硬件模块和软硬件接口集成,并进行软硬件协同仿真,以进行系统评估和设计验证。图1给出了一个软硬件协同设计流程。

图中对软硬件设计流程中每个子过程进行了简单的描述。确定说明文档之后,先建立高级算法模型,然后再考虑软硬件的划分,这样可以更好地分析算法的实现方法,比如是用硬件实现还是用软件实现等。

1.2 软硬件任务划分和软硬件接口

系统模型是对系统初步的粗粒度划分。依据这个粗粒度的划分,有助于第一次软硬件任务分配。在进行软硬件划分时,需要将系统需求根据设计目标和设计约束,分解出硬件的功能需求和非功能需求,以及软件的功能需求和非功能需求,并进一步细化硬件需求及软件需求。

进行软硬件划分是协同设计的重心,划分的合理与否,将直接影响到后续的设计与开发。设计者要从系统的角度,将软硬件完成的功能作均衡,以想要达到的目标为设计标准。在系统的复杂度一定时,使软硬件结合,达到更高的性能。软硬件划分好以后,软件和硬件的设计一直是保持并行的,在设计过程中两者交织在一起,互相支持,互相提供开发的平台。

软硬件的划分不是简单地将功能分解,在进行软硬件任务分配时已经在进行系统的架构设计。其中,非常重要的部分是软硬件的接口设计。嵌入式系统的软硬件接口,从基本的寄存器到高级的系统接口都非常重要。在软硬件任务分配时,主要考虑系统的软件与硬件之间的接口,以及那些影响最终软硬件集成、调试的软硬件接口。

2 系统硬件设计

整个系统的设计可以分为两个部分:第一部分是硬件平台的设计,即可用以运行整个系统的硬件部分,包含了主芯片、外设芯片以及它们之间的互联;第二部分是根据系统设计需求来定制硬件系统,即设计处理器软核和相关外设的控制逻辑,完成系统的定制。第一部分的工作是后面工作的基础。

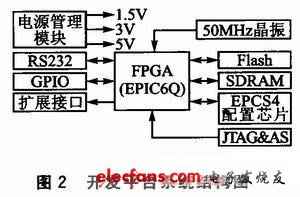

本设计中的SOPC开发平台系统结构如图2所示,开发板的PCB版图设计利用Altium Designer工具完成。软硬件接口设计的主要任务是基于基本指令集完成驱动程序的编写工作。驱动程序是硬件组件与软件组件之间的桥梁。软硬件接口的另一个重要工作是进行硬件初始化。初始化代码是处理器从复位状态进入操作系统能够运行的状态,也就是在把控制权交给操作系统或应用程序之前硬件和底层软件(驱动)必须做的一些工作。

下面详细说明平台中重要的电源电路、Flash接口电路、SDRAM接口电路设计,其他部分电路可参考相应资料。

2.1 FPGA EP1C6Q

目前大部分Altera公司的FPGA均支持NiosIICPU,而Cyclone系列器件是当前世界上成本最低的FPGA芯片之一,因此本设计中的核心芯片采用Cyclone EP1C6,具有9800个逻辑单元,92Kb的RAM资源,提供两个全功能的锁相环(PLL)。I/O接口185个,还支持LVDS、DDR等传输接口。它的配置使用最新型的AS配置方式,配置芯片是EPCS4(Flash结构,4Mb)。

2.2 电源电路设计

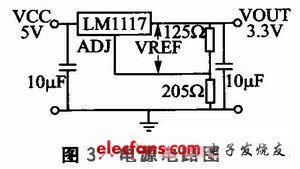

本设计采用了可调三端稳压器LM1117T-ADJ,可以将电压进行线性转换,电流为800 mA,3引脚的T0200封装。Cyclone系列FPGA上电的最大电流为300mA,该芯片可以满足要求。LM1117需要在输出与地之间接入电容以维持内部电路的稳定,输入与地之间也需要接入电容对输入信号进行滤波。具体的连接如图3所示。

2.3 Flash接口电路设计

Flash即闪速存储器,是一种在系统可电擦写的存储器。作为一种非易失性存储器,Flash主要有两个功能,一部分用来存储数据,另一部分存储专用程序。

由于不同厂家的Flash的擦写时序往往不同,Niosll只支持部分常用的Flash,对于不支持的Flash类型,需要NiosII系统设计人员自己完成相关Flash擦写子程序的编写。本平台采用的AM29LV065 Flash存储器。采用48脚TSOP封装,8位数据宽度,工作电压为2.7~3.6V,读写操作都较一般Flash省电,仅需要单3 V电压即可完成在系统编程与擦除操作。

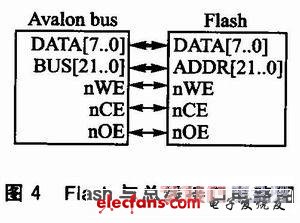

Flash选用的是22×8,即地址总线为22位,数据总线为8位,其连接关系如图4所示。

2.4 SDRAM接口电路设计

与Flash存储器不同,SDRAM不具有掉电保护数据的特性,但其操作都是由时钟作为同步。可以将其理解为一个电容,总是倾向于放电,为避免数据丢失,必须定时刷新(充电)。因此,要在系统中使用SDRAM,就要求微处理器具有刷新控制逻辑,或在系统中加入刷新控制逻辑电路。

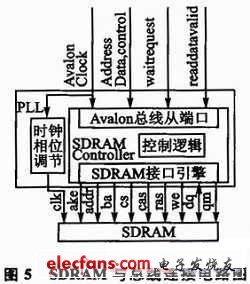

在NiosII系统中,SDRAM主要用于存放运行程序和数据,并且其运行速度比Flash快很多。所以在SOPC系统中,当系统启动后,NiosII CPU首先从复位地址0x0处读取启动代码,在完成系统的初始化后,程序代码一般应调入SDRAM中运行,以提高系统的运行速度。平台使用的是hynix57V641620HGT,其存储容量为4Bank×1M×16位(64 Mb)。SDRAM与总线的连接关系如图5所示,其刷新频率是靠FPGA内的PLL经过相移来提供。

3 SOPC系统结构

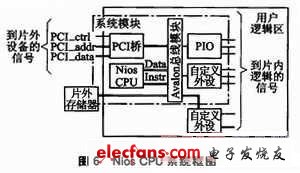

SOPC Builder是一个能够生成复杂硬件系统的工具,将软硬件的设计结合起来,提供给客户一个很好的开发环境。利用SOPC Builder可以将Nios CPU和其他应用模块嵌入到FPGA内部,实现一个可重构的嵌入式系统,其中Nios CPU是整个系统的核心。图6是典型Nios系统的框图,其中片内逻辑是指实现在FPGA内部的电路设计,系统模块指的是由SOPC Builder自动生成的设计。SOPC Builder会根据用户选择的IP生成相应的HDL描述文件(系统模块文件),这些文件与用户逻辑区域内的设计描述文件一起由QuartusII软件综合,然后下载到FPGA内,这样就构成了系统的硬件基础。

采用NiosII单处理器,多个特定功能专用IP核的系统体系结构,软件部分由处理器进行,而硬件部分功能由下载到FPGA上的IP核实现。硬件之间的通信以及与处理器的通信由Altera公司定义的Avalon片内总线实现,而硬件和软件之间的通信则是通过由IDE根据硬件系统生成的硬件抽象层HAL来实现的。

4 总结

近年来FPGA技术的飞速发展,各大FPGA厂商也相继推出针对SOPC开发的各种功能强大的开发套件,这使得FPGA在嵌入式系统设计中相对于传统的ASIC器件具有设计灵活、功能强大、一次性投入低、设计周期短等优势,在嵌入式系统设计中得到越来越广泛的应用。

-

如何去实现一种基于SoPC的软硬件协同设计呢2021-12-24 1976

-

基于SoPC的嵌入式软硬件协同设计性能怎么优化?2020-04-08 2078

-

如何进行SoPC与嵌入式系统软硬件协同设计?2019-11-11 3007

-

嵌入式软硬件协同设计的过程2018-07-12 1332

-

软硬件协同设计机遇与挑战分析2017-11-25 1023

-

基于嵌入式网络的无线传感器网络平台软硬件设计2017-01-12 1225

-

基于SoPC的状态监测装置的嵌入式软硬件协同设计2013-01-22 3569

-

基于SoPC的状态监测装置的嵌入式软硬件协同设计与实现2013-01-16 8093

-

基于SOPC的嵌入式文字识别系统设计2011-09-01 997

-

嵌入式软硬件协同设计在气象主采集器中研究2011-08-04 1057

-

FPGA-SoPC软硬件协同设计2011-05-09 1153

-

基于EDA 的嵌入式系统软硬件划分方法2009-12-05 789

-

[转帖]FPGA培训--基于SOPC的软硬件协同设计2009-07-10 3641

-

北京第十二期FPGA研修班(sopc的软硬件协同设计)2008-12-19 3635

全部0条评论

快来发表一下你的评论吧 !