基于FPGA的NCO设计方案

FPGA/ASIC技术

描述

随着数字通信技术的飞速发展,软件无线电的应用愈加的广泛, 而影响软件无线电性能的关键器件数控振荡器NCO(Numerical CONtrolled Oscillator) 的设计至关重要直接数字频率合成(DDS)技术是一种从相位概念出发直接合成所需要的波形的新的全数字频率合成技术。同传统的频率合成技术相比,DDS 技术具有频率精度高、转换时间短、频谱纯度高以及频率相位易编程、输出的频率稳定度与系统的时钟稳定度相同等一系列优点, 广泛应用于现代各种通信系统中,包括数字上下变频、中频变换、频率合成以及扩频系统和各种频率相位数字调制解调系统中。

在软件无线电及通信领域, 经常使用正交的数字信号;针对此类应用, 本文给出了一种基于FPGA 的正交NCO 设计方法,可以实现正交的、连续相位、高性能、高精度、可重利用的数控振荡器,适合于多种应用场景的片上系统的设计。

1 NCO 实现原理

直接数字频率合成(DDS)技术是一种全数字技术,同传统的频率合成技术相比,DDS 技术具有多项优点: 频率切换时间短、频率分辨率高、相位变化连续、容易实现对输出信号的多种调制等。

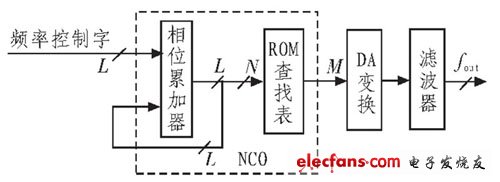

DDS 的原理框图如图1 所示, 其实质是以基准频率源(系统时钟)对相位进行等间隔的采样。由图1 可见,DDS 由相位累加器和波形存储器(ROM 查询表)构成的数控振荡器(NCO)、数模转换器(DAC)以及低通滤波器(LPF)3 部分组成。而DDS 的核心是NCO 的设计与实现,NCO 一般是由相位累加器和正余弦查找表两部分组成,其中相位累加器的设计较简单,故设计NCO 的关键是设计正、余弦函数发生器。

实现函数发生器的方法为查表法(LUT),对于一个相位位数为L,输出信号幅度位数为M 的NCO,所需查找表的大小为M×2L。

图1 DDS 基本原理框图

在每一个时钟周期,L 位相位累加器与其反馈值进行累加,其结果的高N 位作为ROM 查询表的地址,然后从ROM中读出相应的幅度值送到DAC。低通滤波器LPF 用于滤除DAC 输出中的高次谐波。因此通过改变频率控制字K 就可以改变输出频率fout。容易得到输出频率fout与频率控制字K 的关系为:fout=Kfc /2L,其中fc为相位累加器的时钟频率,L 为相位累加器的位数。定义当K=1 为系统频率分辨率,即f=fc /2L。

2 NCO 几种常见设计方法

常见的NCO 实现的方法目前主要有计算法、CORDIC(Coordinated RotATIon Digital Computer)算法和查表法等。

计算法是一种以软件编程的方式通过实时计算产生正弦波样本, 该方法耗时多且只能产生频率相对较低的正弦波,而需要产生高速的正交信号时,用此方法不能很好的满足要求。

CORDIC 算法即坐标旋转数字计算方法, 其基本思想是用一系列固定角度的不断偏摆逼近所需旋转的角度,实现包括乘除、平方根、三角函数、向量旋转(即复数乘法) 以及指数运算,该算法往往需要通过乘法器和查找表才能实现多种超越函数的计算,这会导致硬件电路实现复杂、运算速度降低,此外它能够计算的角度范围也有限,故CORDIC 算法在实际使用时有较大的限制条件。

在实际应用中一般采用最有效、最简单的查表法,即事先根据各个NCO 正弦波相位计算好相位的正弦值, 并以相位角度作为地址把该相位的正弦值数据存储在表中,然后通过相位累加产生地址信息读取当前时刻的相位值在表中对应的正弦值,从而产生所需频率的正弦波;同时由于正余弦波形的对称性,只需要存储部分数据即可完成全相位的数值输出。这种实现方法,设计简单、运算速度较高,可以很好的满足在数字变频、扩频、调制解调等多种场合的要求。

3 正交NCO 的查找表实现方法

基于FPGA 的正交NCO 设计原理框图如图2 所示,主要由3 部分组成: 可变模计数器、正余弦查找表和输出单元3个模块组成。

图2 NCO 的设计原理框图

下面以输入的频率控制字为1 200 Hz 为例进行设计。

Fre_sample, 表示系统采用时钟;Fre_cnt_word 表示频率控制字。

1)可变模计数器的设计

可变模计数器是根据频率控制字,计算出正余弦表的查表所需的地址;同时要保证产生的正余弦波的相位保持连续(有些应用场合常常要求输出的相位连续),即置于相应的余数值。在第1 个工作时钟周期读入频率控制字,第2 个工作时钟周期内计算出mod(Fre_sample,Fre_cnt_word)作为相位控制字,第3 个工作时钟周期内部计数器复位置入相位控制字,第4 个时钟周期开始以频率控制字为步长,相位控制字为初始值进行计数输出。

2)正余弦查找表的设计

正余弦查找表是根据可变模计数器的输出查表得到相应载频波形的输出。

基于FPGA 的NCO 设计的一个关键就是波形存储器ROM 相位累加器的输出地址作为ROM 的地址输入,经查表和运算后,ROM 输出正余弦波形的量化数据; 设计中主要是要节省存储器资源的开销,即减小ROM 存储表的空间;由于存储表的尺寸随着地址位数或数据位数的增加呈现指数级递增关系,所以在满足频率分辨率、信号性能的前提下,主要考虑较小ROM 存储表的开销;在实际的应用中,可以充分利用正余弦信号在一个周期内的对称性来减少ROM 存储表的开销, 例如正弦信号, 在一个周期内对于X 轴是对称的,基于此可以将ROM 存储表减少至原来的1 /2, 再利用半周期内的左右对称性,又可以将ROM 存储表减少至原来的1 /2,因此通过一个正弦查找表的前1 /4 周期就可以变换得到整个正弦波周期查找表,这样就节省了3 /4 的存储器资源。

正余弦表的具体设计思想如下: 取频率分辨率为df=1 Hz ; 假设频率控制字为1 200 Hz 的频率左右, 现考虑对1 200 Hz 的正余弦波形每一个周期采8 个样点,则可得采样率为fs =1 200×8=9 600 Hz.设对于每一个样点值取8 bit 量化,则每个表格共需存储9.6 kB;(如果考虑到正、余弦信号的对称性,设计时可优化为上每个表格存储1/4 个波形即可,即每个表格只需存储2.4 kB;)使用时是用步长STep 来调节输出频率, 同时保证输出的正余弦波的相位连续。如果每隔0样点取1,即step=1,输出频率为1 Hz;每隔1 点取1,即step=2,输出频率为2 Hz;……;每隔1 199 点取1,step=1 200, 输出频率为1 200 Hz.

3)正余弦表的装载

采用Quartus 软件中的。mif 文件格式可以方便的完成存储表的装载; 同时对于装载文件的生成可以使用matlab 输出。mif 的文件格式很方便的生成; 如下文中给出了位宽为8 bit ,深度为9 600,地址为无符号数,数据为十进制数的9 600 个单元的mif 文件,在初始化RAM 时,按照Quartus 软件的引导直接配置即可。

WIDTH=8;

DEPTH=9600;

ADDRESS_RADIX=UNS;

DATA_RADIX=DEC;

CONTENT BEGIN

0 : 0;

1 : 2;

2 : 10;

3 : 30;

4 : 50;

5 : 50;

6 : 10;

7 : 100;

……

9598 : 0;

9599 : 0;

END

4 设计实现及其仿真波形

本次设计采用性价比较高的ALTERA 公司的STRATIX芯片进行设计仿真,该系列芯片是基于1.5 V 工作电压、0.13 μm全铜布线SRAM 工艺的FPGA 芯片。此系列芯片拥有最多114 140 个逻辑单元(Les)和最多10 Mbits 的内部RAM.该系列芯片支持多种I/O 标准,提供了最多可达12 个的用于处理复杂时钟信号的锁相环(PLLs)。同时,STRATIX 系列芯片提供了最多可达28 个的数字信号处理单元(DSP),它们由总共224 个内置硬件乘法器(9 位乘9 位)组成,利用它们可以有效地实现例如快速傅立叶变换(FFT)、有限冲击响应(FIR)滤波器、无限冲击响应(IIR)滤波器等高性能的数字信号处理单元或者乘法器。

图3 NCO 模块的主要端口定义

2)Quartus 仿真输出波形,如图4 所示。

图4 NCO 的仿真输出波形

此仿真波形为3 个频点的NCO 输出波形, 用matlab 绘出输出的载波的波形如图5 所示。

图5 输出载波的波形

由上面的仿真结果可以看出,NCO 正确输出了3 个频点的仿真波形;同时通过实际的FPGA 硬件测试和验证,该设计达到了所要求的性能指标。

5 资源占用情况

使用Altera 公司的STRATIX 芯片进行编译、综合,所得的资源占用结果如图6 所示。

图6 NCO 资源占用情况

6 结束语

本文给出了一种基于FPGA 的正交NCO 的设计方法,在实际应用过程中可参考给出的设计实例,通过改变频率控制字、系统采样频率、存储正余弦查找表的深度和存储表的位宽,即可得到不同输入频率范围的NCO;同时如果涉及需要的精度及频率较高, 也可采用外置的存储器, 如FLASH,SRAM 等与FPGA 配合使用, 较大的扩展存储表的深度和位宽,可最终达到设计的要求。

-

基于CPLD/FPGA的多串口扩展设计方案2023-10-27 614

-

基于FPGA的伪随机数发生器设计方案2021-06-28 4995

-

基于CPLD/FPGA的半整数分频器设计方案2021-06-17 1150

-

基于FPGA的二进制相移键控设计方案2021-05-28 1261

-

基于FPGA的数据无阻塞交换设计方案,不看肯定后悔2021-04-29 1555

-

基于FPGA的调焦电路设计方案资料下载2018-05-07 1393

-

基于FPGA的OLED真彩色显示设计方案2017-01-18 1019

-

基于FPGA的变频器设计方案,利用simulink仿真2014-09-10 3140

-

FPGA典型设计方案精华汇总2012-08-16 12209

-

FPGA设计大赛设计方案提交规则和截止时间须知2012-05-04 20910

-

数字控制振荡器(NCO)的FPGA实现2011-05-09 19299

-

从ASIC到FPGA的转换系统时钟设计方案2011-03-02 2941

-

多种EDA工具的FPGA设计方案2010-05-25 937

-

利用FPGA的无线通信收发模块设计方案2009-11-26 42269

全部0条评论

快来发表一下你的评论吧 !