存储百倍提升! IBM纳米技术1比特12原子

电子技术

描述

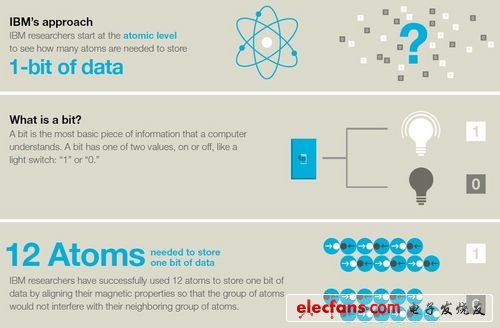

提到存储,比特(bit)是最小的单位,然而一比特需要多少个原子呢?最近IBM的研究人员用纳米技术诠释了这一概念,存储一比特信息仅需12个原子。该项技术能大大提升了存储的密度,相比于现在的硬盘,同单位面积能够存储的信息量有百倍以上的提升。集成电路的晶体管随着摩尔定律越来越密集,在晶体管大小越来越达到的物理极限的形势下,迫使人们寻求新的技术,才能将性能进一步提升。一比特仅需12各原子,存储性能达到如今硬盘的百倍以上,在信息时代下大数据的趋势中无疑将发挥重要的作用。

一比特仅需12原子

比特是计算机信息单元的基本单位,一比特有两个值:0和1。IBM采用铁原子磁矩的方向组合来存储计算机语言中的0和1,也许大家会说了,为什么不直接用铁原子的磁矩方向代表0和1呢?这样只需一个原子就可存储1比特的信息,何须12个原子?

一比特仅需12原子

这里的问题是,相邻的铁原子磁矩会互相干扰,相信大家都玩过磁铁,两块磁铁相互靠近时,会有相互作用,或是排斥或是吸引。微观世界中的原子磁矩也是如此。因此才需要找到稳定的铁原子磁矩的方向组合来存储计算机语言中的0和1。

一比特仅需12原子

比特这一计算机信息最小单位,需要多少个原子呢?有些资料显示,如今的硬盘虽然已经能达到单个TB级的容量,但是存储1比特的信息也要百万个原子。

12个铁原子微观示意图

IBM通过使用扫描隧道显微镜(STM)将12个反磁性关联原子组合在一起,存储一个比特的数据,并在低温下维持了几个小时之久,证明代表0或1的原子磁矩稳定组合的原子数可以远比之前想象少得多。存储密度能够达到当今机械硬盘或是固态硬盘的百倍以上。>>

IBM加州阿尔马登研究院原子存储首席研究员Andreas Heinrich说到:“芯片产业会继续追求半导体技术的进步,但随着原件的缩小,终究会到达不可回避的终点:原子。我们反其道而行之,直接从单个原子这一最小单元入手,利用一个一个的原子去搭建计算设备。”

原子磁矩存储示意图

IBM的研究人员利用原子磁矩存储技术,通过不同的磁矩组合代表0和1,存储了“THINK”五个字母的ASCII码。

原子磁矩存储THINK

有点眼熟吧,IBM有过类似的手法,也许大家对下面这张IBM的图会比较熟悉,当时IBM首次实现操控原子,摆出了IBM字母。现在IBM实现原子级别上的存储技术,存储的信息是THINK这一单词,由当初的公司名称IBM,换成了IBM的百年来的公司文化理念THINK。

IBM

从数据存储的最小单元比特着手,寻求到一比特仅需要12个原子,IBM发现磁性存储的密度至少可以达到机械硬盘、固态硬盘的100倍。

存储性能百倍提升

利用纳米技术还可以操纵单个原子,形成所谓的反铁磁性(antiferromagnetism),能让人们在同样的空间内塞下100多倍的信息。也就是说,利用原子磁矩存储技术,现如今的1TB硬盘,能够提升到100T的容量。>>

在集成电路的晶体管数目的规律上,业界有一个著名的摩尔定律。摩尔定律指出,当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。该定律是由英特尔创始人之一摩尔提出,这些年来一直与芯片的发展相符。

硅晶元

然而随着集成电路上的晶体管密度越来越大,其在密度上得增加就越来越困难。摩尔定律势必将晶体管的大小带到了一个物理上的极限。

intel纳米技术发展

作为集成电路的代表CPU芯片,其制程由早先的130nm、到65nm、45nm、22nm以及之后的14nm,硅晶体管的尺寸越来越接近物理的极限。

为了进一步提升CPU、内存等芯片的性能,科学家们想到了结构和技术上的方法。在芯片结构上,3D芯片成为众多企业追逐的领域。而在技术上,碳纳米管、PCM相变存储以及现如今的原子磁矩存储技术,也为芯片性能的提升展示一个美好的前景。

芯片“摩天大楼”

2011年10月中旬,相关媒体报导,IBM与3M公司推出摩天大楼的处理器芯片,通过一种特殊的硅胶粘合剂将芯片组合在一起,成为芯片“摩天大楼”。IBM和3M宣称,这种摩天大楼的微处理器能比普通的处理器性能提升1000倍。

Hybrid Memory Cube(HMC)

不仅是CPU追求3D,内存也是一样,IBM和美光公司Hybrid Memory Cube(HMC)项目就是很好的例子。两家公司表示新型3D芯片的内存所需能源和空间较少,并且每秒能传输128G左右的数据,这一速度比目前的内存芯片快十倍左右。这种3D芯片的内存产品预计于2012年下半年出货。>>

新型的存储技术也是各厂商提高芯片性能所追逐的领域,在HMC项目上同样与美光公司有合作的三星,在新型PCM相变存储领域的研究也试图和IBM一较高下,PCM作为下一代存储的热门领域,有望取代目前普遍应用的闪存。去年7月份IBM展示的90nm制程工艺的PCM芯片,比闪存快约100倍。而近日三星宣布将在明年发布的8G相变存储芯片,制程工艺则更进一步达到20nm。

PCM原理

据了解,三星公司将在今年年2月举行的2012年国际固态电路会议(ISSCC)上发布20nm的PCM相变存储芯片元件,相比于去年2月发布的PCM芯片,制程工艺从58nm提升到了20nm,而且大小从1G增大到8G。

ISSCC 2012

作为芯片设计界的“奥运会”,ISSCC大会往往汇集了芯片设计的最前沿科技,2012年的ISSCC将在2月19日至23日在旧金山举行,本次大会收录的202篇论文中,亚洲地区占了73篇(36%),美洲占了68篇(34%),这也是ISSCC大会举办59届以来,来自亚洲的论文数量首次超过美洲。本次ISSCC 2012的会议主题是“Silicon Systems for Sustainability(以可持续性为目标的硅系统)”。CPU内存等芯片都属于这一范畴。

ISSCC 2012主题是“以可持续性为目标的硅系统”,现在的集成电路大多是基于硅晶体管,硅晶体管在尺寸上达到极限时,寻找另外一种材料突破硅晶极限也颇为重要。前些日子英特尔宣布14nm的硅晶体芯片已经在实验中开始测试,而IBM研制的新型晶体管比10nm还要小,采用的是碳纳米材料。

碳纳米材料结构

在IEEE的一个电子设备会议上,IBM的科学家向世界展示了全球第一个小于10nm的晶体管,与目前一般的硅晶体管不同的是,其采用的是碳纳米材料。相比之下英特尔14nm的硅晶体管在尺寸上就相形见绌了。

存储上,IBM则是推行原子水平的磁矩存储技术,相比于目前的存储技术,IBM的原子磁矩存储技术有上百倍的提升。

晶体管尺寸达到物理极限是个必然,就像世界能源从当初的煤、再到后来的石油、以及现在的天然气,有人分析称每一个能源在达到极限时,必然会有另外一种替代品。同样,随着人类的探索与科技的不断进步,新技术势必取代如今的集成电路中的技术。

-

关于MEMS和纳米技术的综述2022-11-15 675

-

纳米技术在生活中的应用2021-08-31 2080

-

纳米技术是怎么回事看完你就懂了2021-05-13 1813

-

纳米技术的定义_生活中哪些是纳米技术2020-04-09 25359

-

什么样的币可能是百倍币2019-07-18 6046

-

纳米技术在医疗的应用2019-03-16 19783

-

纳米技术的应用领域2018-09-21 3652

-

氢原子存储技术,存储密度相比提升超过700倍2018-08-04 1027

-

氢原子存储技术:实现了0与1的数据存储,存储密度提升超过700倍2018-07-31 1451

-

纳米技术将使芯片速度快1000倍2016-11-16 6370

-

2013年韩国首尔纳米技术展NANO KOREA2013-02-24 3525

-

IBM研究存储设备取得大突破:有望更小巧轻便2012-01-16 719

-

什么是纳米技术电池?2009-10-26 1547

全部0条评论

快来发表一下你的评论吧 !