Allegro PCB Editor实现单板拼版设计

描述

制造过程连接着设计师和大规模生产 PCB 的公司。设计者必须了解,该过程涉及相关成本,这意味着工作时间和工程材料的表面积都需要优化。拼版是一种用于同时大规模生产多块电路板的技术,这些电路板放置在一个阵列中,以加快装配进度。

在整个 PCB 设计结束后,电路板需要在 SMT 贴片流水线上安装元器件。每个 SMT 加工工厂会根据流水线的加工要求,对电路板的合适尺寸做出规定。如果电路板尺寸过小或过大,流水线上固定电路板的工装将无法固定。那么,如果电路板本身尺寸小于工厂规定的尺寸怎么办?这就需要对电路板进行拼板,将多个电路板拼成一整块。拼板对于高速贴片机和波峰焊都能显著提高效率。拼板主要是为了主要是减少材料的浪费,提高生产效率。

Cadence从SPB17.4版本开始,将Fab Panelization Tool作为PCB Editor的基本功能,让设计师们,在完成了单板设计后,很方便地在Allegro PCB Editor环境中,快速实现单板的拼版设计,以优化制造过程。Cadence的Allegro PCB Editor中的Fab Panelization Tool是一个简化拼版文档处理的应用程序。

1

Fab Panelization Tool拼版功能涵盖:

• 拼版仅在布局的基础上设置,不需要原理图。

• 实际的Board数据链接到拼版数据进行自动更新。

• 也支持混合拼版,这意味着可以将不同的电路板数据引入到同一个拼版数据中。

• Board可以单独放置,也可以通过指定阵列来放置。

• 每块Board都可以在拼版数据中进行单独旋转和/或镜像。

• 更新过程是完全自动化的。

• 如果需要更新,包括自动和手动通知(Board已修改)

• 使用来自PCB Editor的经过验证的mdd技术(设计重用,Replicate放置)。

为了让设计师尽快掌握Fab Panelization Tool工具的使用,本文将介绍如何使用AllegroPCB Editor 进行拼版设计。

01

创建brd数据

进行拼版设计,必须创建一个新的brd数据。在新的brd数据中,必须添加Design_Outline、Outline、Route_Keepin、Package_Keepin等信息,添加标记、切割标记等机械信息来准备新的brd数据。由于PCB板制造商使用不同的尺寸,建议将拼版数据定义为Mechanical Symbol形式以供重复使用。

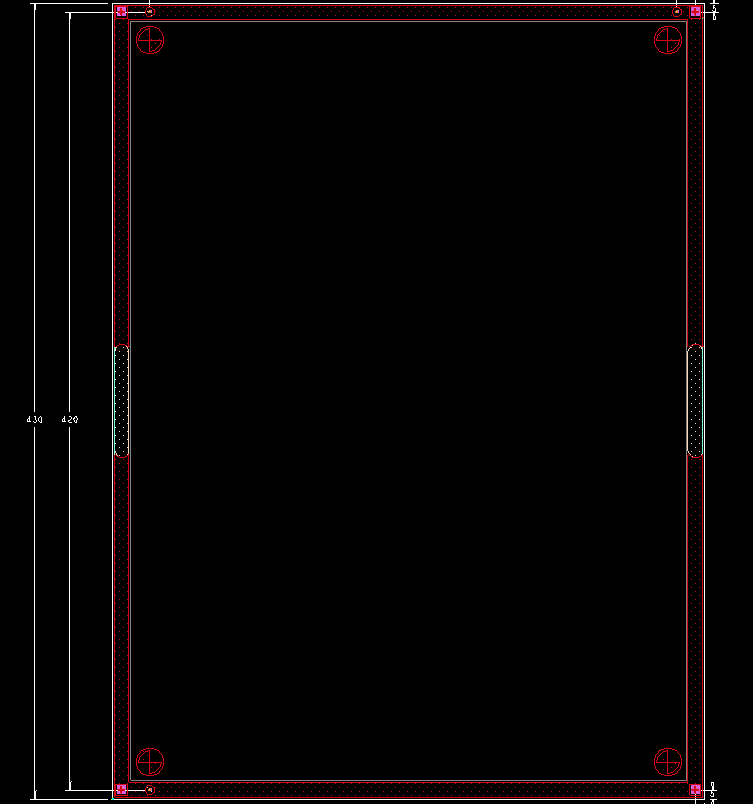

启动PCB Editor工具,打开pcb_context目录下的panel_start.brd文件,如图所示:

02

Fab Panelization Tool

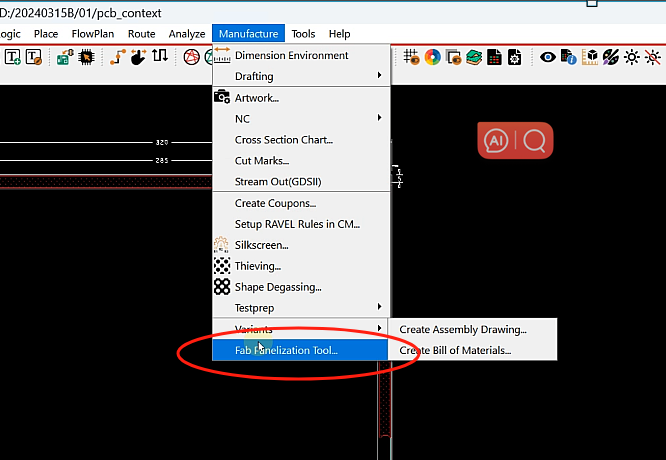

在PCB Editor中,选择Manufacture下拉菜单选择Fab Panelization Tool,如图所示:

03

03

设置数据

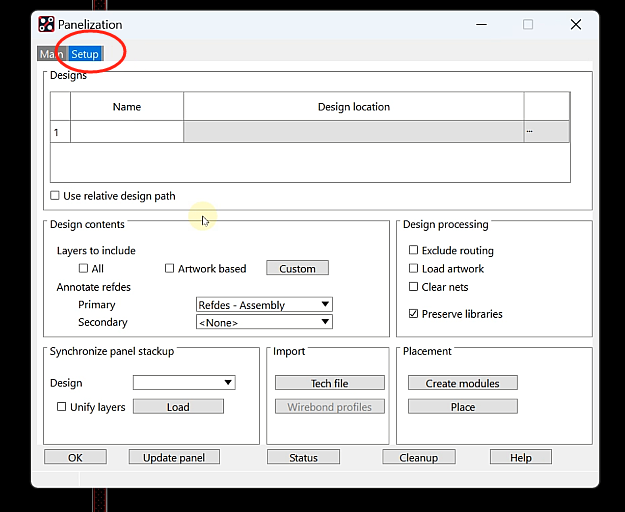

当进入Panelization界面后,选择Setup选项卡,如图所示:

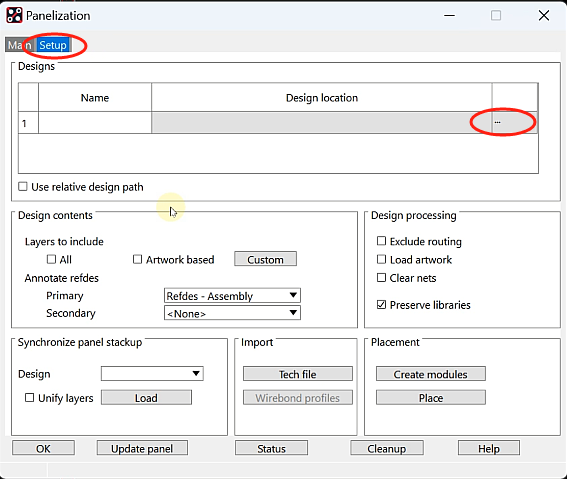

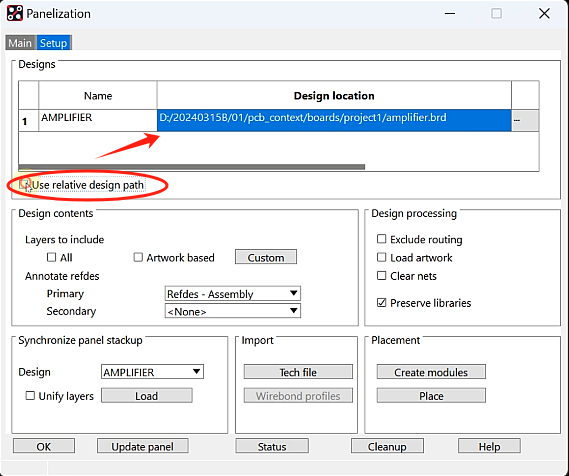

1)在Designs区域里,第一行中点击Browse字段,会出现一个文件浏览器,导航到您想要定义拼版的brd数据。选择pcb_context/boards/project1/amplifier.brd文件,如图所示:

在这一步,如果勾选了Use relative design path,Design location将显示为brd数据的相对路径,如图所示:

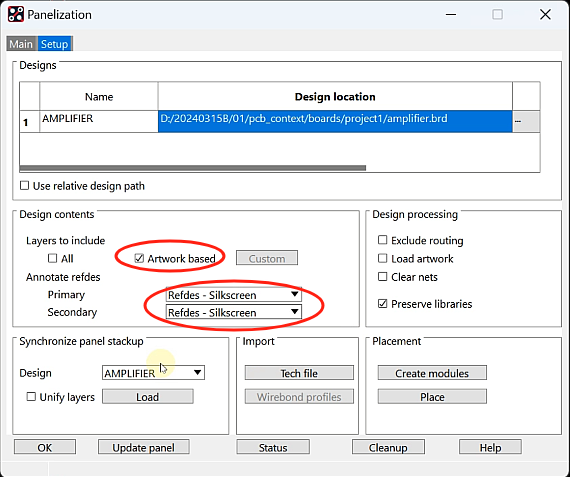

2)在拼版设计过程中,希望生成拼版的装配图,包括原始(非前缀)Refdes,拼版中的每一块子板保持原始的Refdes维持不变。因此,需要在Design ontents中,勾选Artwork based,确保系统自动将原始brd中的Refdes-Silkscreen层的信息,分别复制到系统新建的Package Geometry-Pnl_Refdes层中,设置如图所示:

04

04

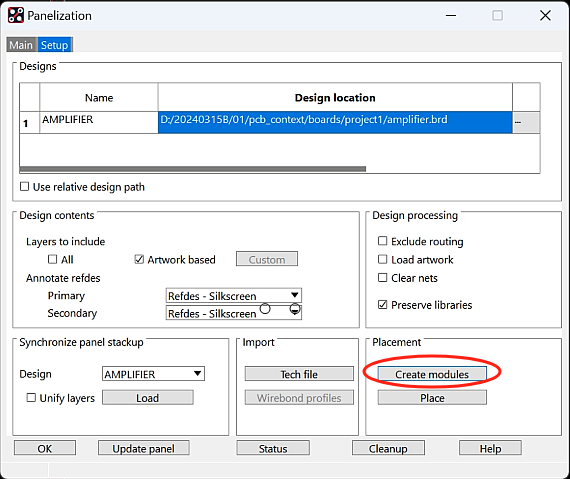

创建模块(Module)

点击Create Modules,按下此按钮 ,PCB Editor将打开Designs栏中指定的brd板,并为其创建一个模块。此外,将提取交互式放置所需的尺寸信息和实际轮廓数据。如图所示:

05

放置模块

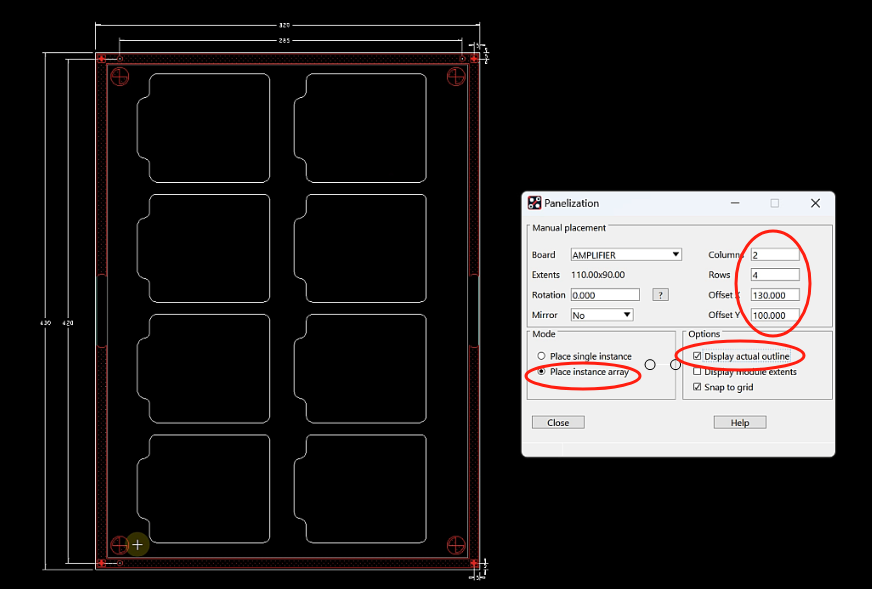

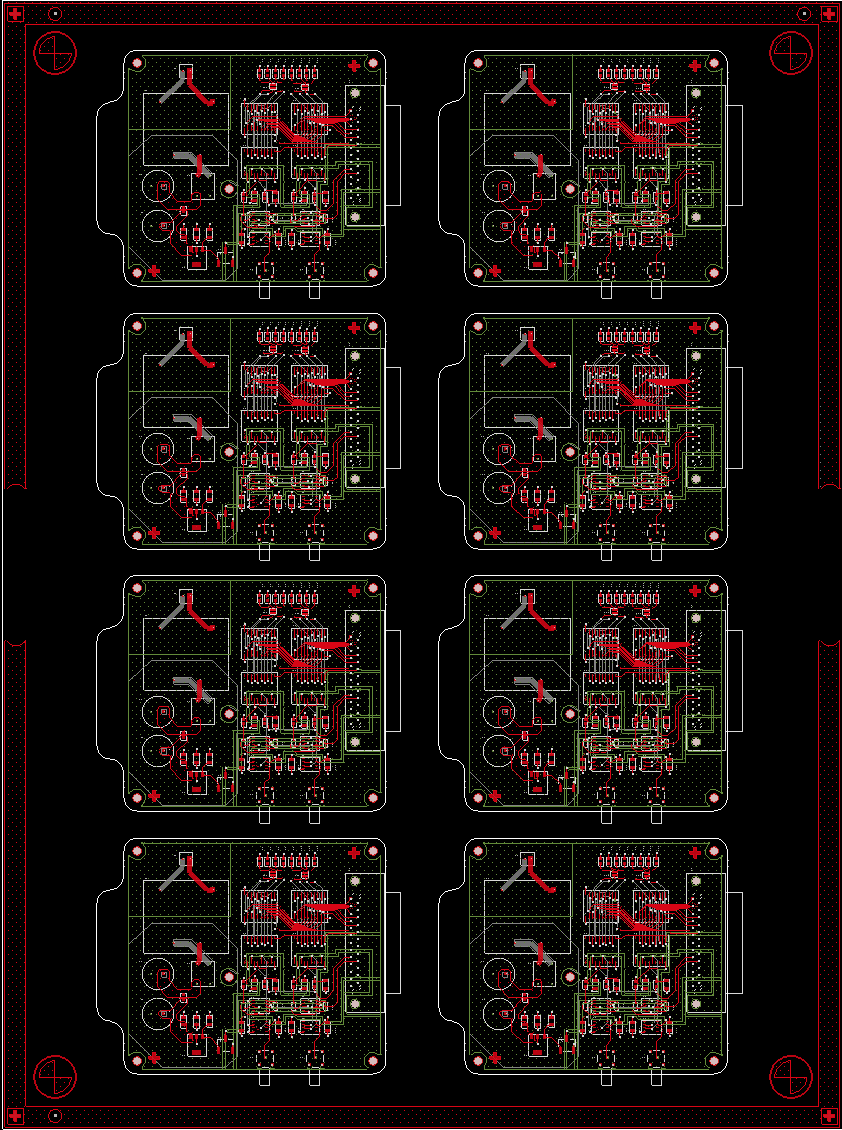

点击Place,系统将弹出Panelization放置界面,在Manual placement区域,设置Columns为2、Rows为4、Offset X为130、Offset Y为100;在Mode区域,选择Place instance array;Options区域,勾选Display actual outline,系统将以实际PCB板的Outline为PCB板边框显示轮廓,如图所示:

一旦您在拼版数据中指定了位置,板子将显示为模块实体。

-

PCB拼版设计技巧2025-02-26 1780

-

Allegro PCB Editor实现混合拼版设计2024-03-30 5741

-

拼版不合理案例详解2023-12-04 1002

-

实用PCB拼版攻略 | 您的拼版合理吗?2023-11-03 1372

-

使用Allegro PCB Editor制作Logo封装2023-06-21 4815

-

SMT-PCB拼版设计规范2023-06-15 2570

-

PCB拼版心得2022-07-23 6691

-

PCB拼版设计时的注意事项资料下载2021-04-17 1281

-

allegro中拼版操作流程分享!2019-09-08 20355

-

Allegro PCB Editor 16.2菜单中英文对照资料分享2015-05-20 13257

-

Allegro_PCB_Editor电路板设计教程2013-08-13 3179

-

allegro pcb editor规则设置类别优先顺序2011-11-22 6505

全部0条评论

快来发表一下你的评论吧 !