深入解析FPGA的层次化设计思想

可编程逻辑

描述

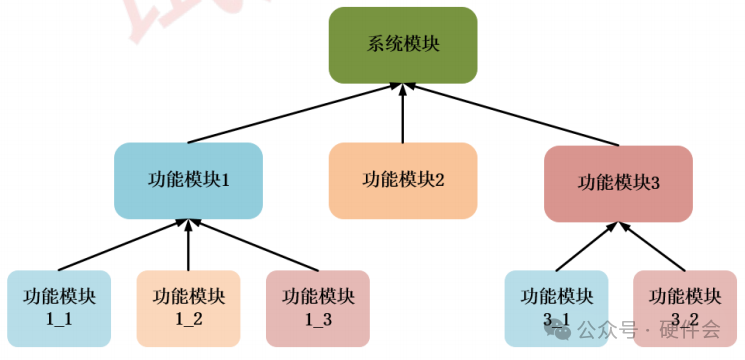

众所周知FPGA开发实质是硬件描述,无论是语言还是FPGA内部都可以理解为是在设计硬件电路。设计一个系统电路,首先要对系统有宏观的理解,然后再对系统模块逐一慢慢分解为一个个小的功能单元,这些功能单元可以是IP核或者其它项目开发好的单元。如下图所示:

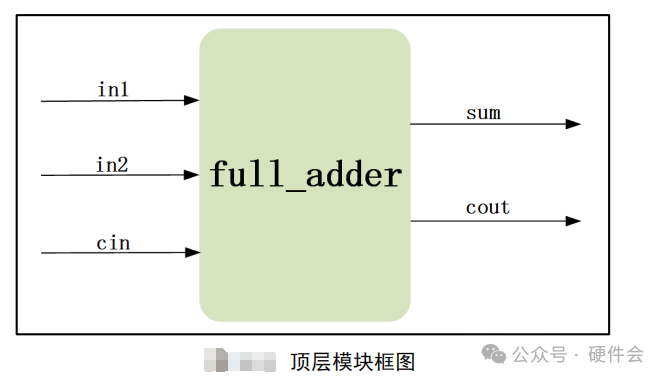

自上而下的设计是把系统模块作为基本单元,然后再逐一分解,一直这样分解下去,直到无法进一步分解,可以用EDA元件库中的元件来实现为止。 下边以设计一个全加器为例,全加器和半加器不同的是除了两个加数以外还有一个加数,第三个加数是上一级加法器的进位信号,这样就相当于是三个1bit的数相加。首先给顶层模块取一个名字为full_adder,框图如下:

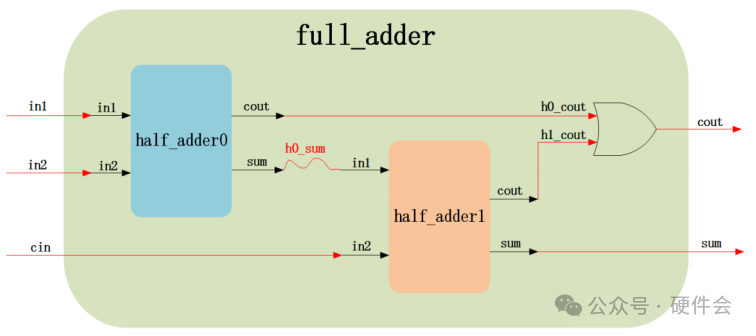

我们用一个方法推导一下:全加器有三个 1bit 的加数,我们可以先实现两个数的加和,再加上第三个数并不会影响最后的结果。我们知道两个数的加和就是半加器所实现的功能,所以先进行的两个数的加和运算需要用到一个半加器来实现,然后输出求和信号和进位信号,求和信号再和第三个加数加和需要再使用一个半加器,然后输出进位信号和最后的总和号。但是进位信号有两个,这两个进位信号都是有用的,但又不会同时为存在,一个有效即有效,所以将两个半加器的进位信号用一个或门运算后作为最后的输出进位信号(也可以用逻辑表达式的方式推导)

本例中全加器可以用两个半加器组成,两个进位信号用或门输出。

红色的为顶层的信号线,黑色的为底层模块的信号线,信号的颜色变化也代表层的变化。

将half_adder0 的 sum 信号和 half_adder1 的 in1 信号连接,连接线还单独取了一个名字为h0_sum 用于将 sum 信号的数据传到顶层(否则两个独立模块是没有任何交集的)。 每一个模块都相当于一个实体的“芯片”,而框图中的 half_adder0 和 half_adder1 就相当于两个不同的半加器芯片,再加上一个或门芯片就可以实现一个具有全加器功能的系统,这做好的这个全加器也是一个模块,如有需要也可以把这个模块当成一个“芯片”用在其他的系统中。所以设计的时候我们可以把每个模块都做好,特别是具有通用性功能的模块,等用到的时候我们不必关心其内部结构是怎样的,只需知道其功能和端口信号,直接拿过来使用即可,是不是很方便。

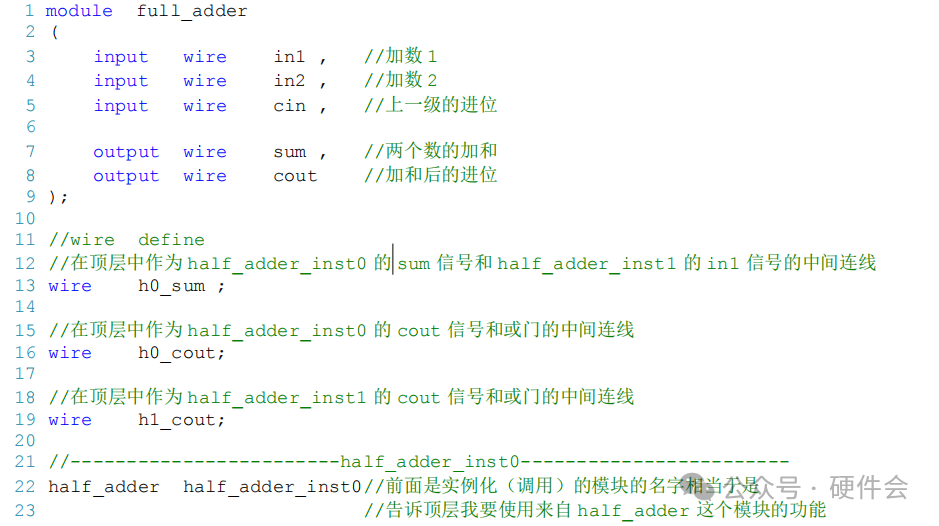

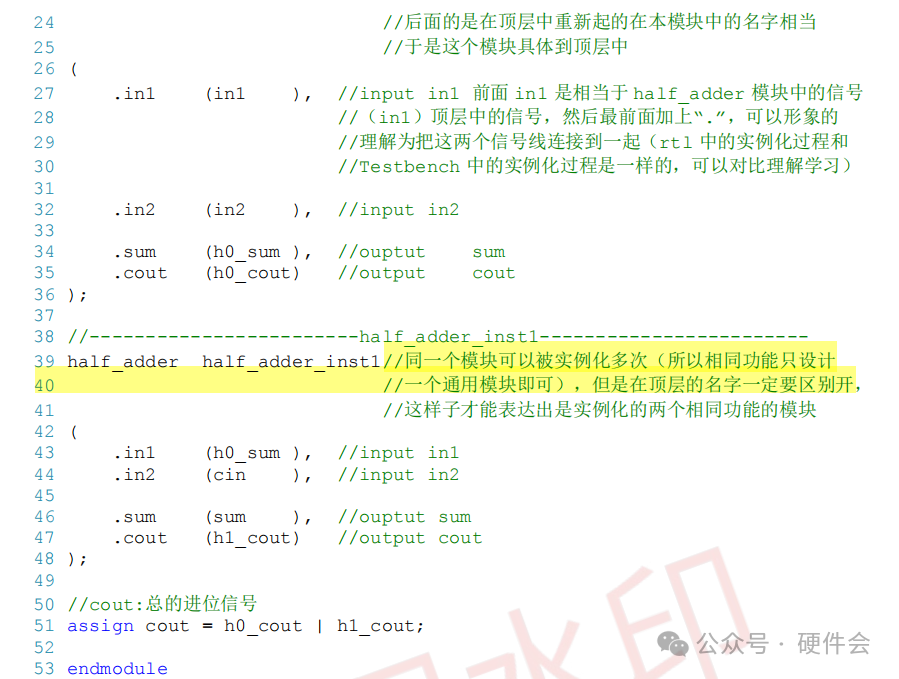

顶层模块代码如下所示:

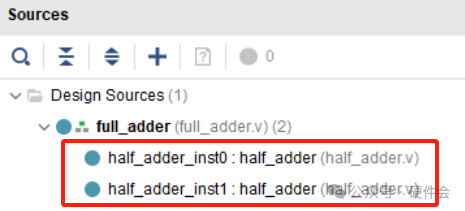

将开发好的半加器文件引用进去即可。如下图:

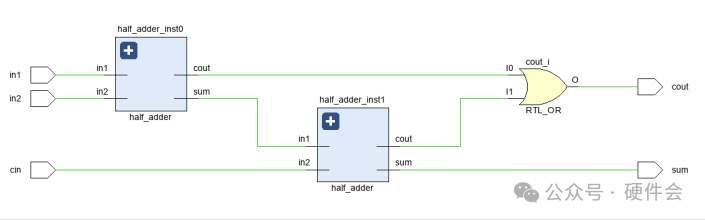

代码进行RTL综合,得到电路框图如下所示:

在以后设计中有很多情况具有特定功能的模块需要再次调用,可能会有数十个模块要调用,为了方便调用,我们往往把具有独立功能的模块做成通用模块,日积月累,当我们积累的越来越多,开发也会变的很容易。 层次化设计有个问题,就是直接验证顶层模块,如果子模块有问题,这样我们再分析时往往很复杂,所以推荐要先对子模块进行单独验证,这样不至于当整个设计太大的时候直接验顶层模块而导致错误很难查找,养成习惯会让设计越来越轻松,越来越顺利。

审核编辑:黄飞

-

常用FPGA/CPLD设计思想与技巧2023-05-18 1148

-

常用的FPGA/CPLD设计思想与技巧有哪些?2021-04-29 1275

-

FPGA/CPLD的设计思想2016-02-17 829

-

FPGA开发流程及编程思想2016-01-18 641

-

如何快速学习FPGA之炼狱传奇层次化2015-06-18 4234

-

FPGA设计重要思想、同步设计2014-11-14 8205

-

FPGA之设计思想2013-01-05 3473

-

FPGA 设计的四种常用思想与技巧2012-08-11 6792

-

NAND闪存深入解析2012-08-09 2661

-

FPGA/CPLD设计思想与技巧2010-11-04 859

-

FPGA设计思想与技巧2010-01-11 691

-

FPGA设计的四种常用思想与技巧2009-10-29 521

-

FPGA设计(设计思想与技巧)2009-08-15 8051

全部0条评论

快来发表一下你的评论吧 !