如何确保ADC输出接地的准确性

模拟技术

描述

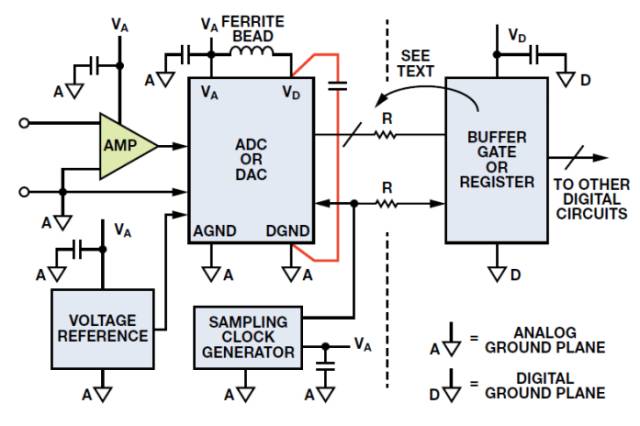

虽然很多转换器具有三态输出/输入,但这些寄存器仍然在芯片上。它们使数据引脚信号能够耦合到敏感区域,因而隔离缓冲区依然是一种良好的设计方式。某些情况下,甚至需要在模拟接地层上紧靠转换器输出提供额外的数据缓冲器,以提供更好的隔离。

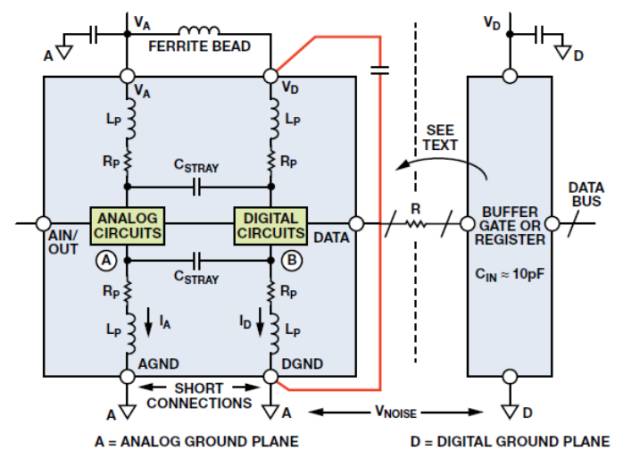

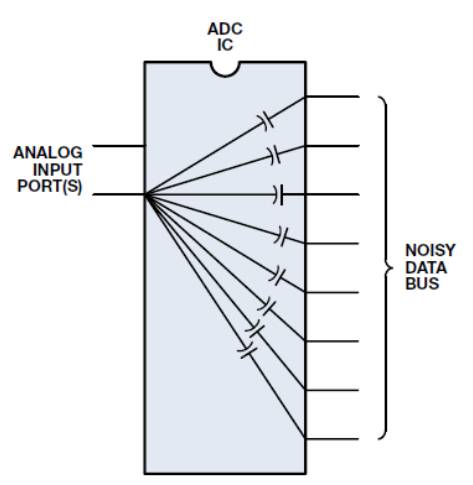

将数据缓冲器放置在转换器旁不失为好办法,可将数字输出与数据总线噪声隔离开(如图 1 所示)。数据缓冲器也有助于将转换器数字输出上的负载降至最低,同时提供数字输出与数据总线间的法拉第屏蔽(如图 2 所示)。

图 1.具有低内部数字电流的混合信号 IC 的正确接地

图 2. 在输出端使用缓冲器/锁存器的高速 ADC 具有对数字数据总线噪声的增强抗扰度

ADC 输出与缓冲寄存器输入间的串联电阻(图 1 中标示为“R”)有助于将数字瞬态电流降至最低,这些电流可能影响转换器性能。电阻可将数字输出驱动器与缓冲寄存器输入的电容隔离开。此外,由串联电阻和缓冲寄存器输入电容构成的RC网络用作低通滤波器,以减缓快速边沿。

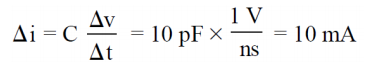

典型 CMOS 栅极与PCB走线和通孔结合在一起,将产生约 10 pF 的负载。如果无隔离电阻,1 V/ns的逻辑输出压摆率将产生10 mA的动态电流:

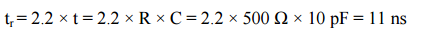

驱动10 pF 的寄存器输入电容时,500 Ω 串联电阻可将瞬态输出电流降至最低,并产生约 11 ns的上升和下降时间:

由于TTL寄存器具有较高输入电容,可明显增加动态开关电流,因此应避免使用。

缓冲寄存器和其他数字电路应接地并去耦至 PC 板的数字接地层。请注意,模拟与数字接地层间的任何噪声均可降低转换器数字接口上的噪声裕量。由于数字噪声抗扰度在数百或数千毫伏水平,因此一般不太可能有问题。模拟接地层噪声通常不高,但如果数字接地层上的噪声(相对于模拟接地层)超过数百毫伏,则应采取措施减小数字接地层阻抗,以将数字噪声裕量保持在可接受的水平。任何情况下,两个接地层之间的电压不得超过 300mV,否则 IC可能受损。

最好提供针对模拟电路和数字电路的独立电源。模拟电源应当用于为转换器供电。如果转换器具有指定的数字电源引脚(VD),应采用独立模拟电源供电,或者如图 3 所示进行滤波。所有转换器电源引脚应去耦至模拟接地层,所有逻辑电路电源引脚应去耦至数字接地层,如图 3 所示。如果数字电源相对安静,则可以使用它为模拟电路供电,但要特别小心。

图 3. 接地和去耦点

某些情况下,不可能将 VD连接到模拟电源。一些高速IC 可能采用+5 V电源为其模拟电路供电,而采用+3.3 V或更小电源为数字接口供电,以便与外部逻辑接口。这种情况下,IC 的 +3.3 V引脚应直接去耦至模拟接地层。另外建议将铁氧体磁珠与电源走线串联,以便将引脚连接到+3.3 V数字逻辑电源。采样时钟产生电路应与模拟电路同样对待,也接地并深度去耦至模拟接地层。

针对高频工作的接地

一般提倡电源和信号电流最好通过“接地层”返回,而且该层还可为转换器、基准电压源和其它子电路提供参考节点。但是,即便广泛使用接地层也不能保证交流电路具有高质量接地参考。

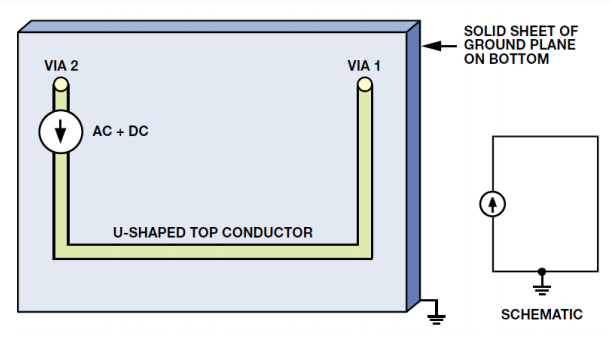

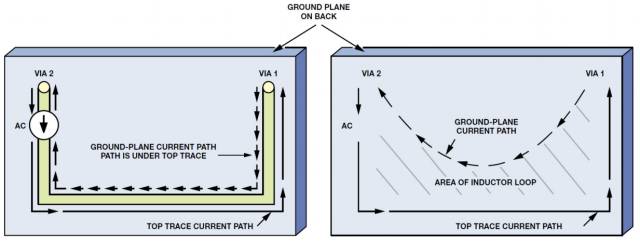

图 4 所示的简单电路采用两层印刷电路板制造,顶层上有一个交直流电流源,其一端连到过孔 1,另一端通过一条 U 形铜走 线连到过孔2。两个过孔均穿过电路板并连到接地层。理想情况下,顶端连接器以及过孔 1 和过孔2之间的接地回路中的阻抗为零,电流源上的电压为零。

图4 . 电流源的原理图和布局,PCB 上布设 U 形走线, 通过接地层返回

这个简单原理图很难显示出内在的微妙之处,但了解电流如何在接地层中从过孔1流到过孔2,将有助于我们看清实际问题所在,并找到消除高频布局接地噪声的方法。

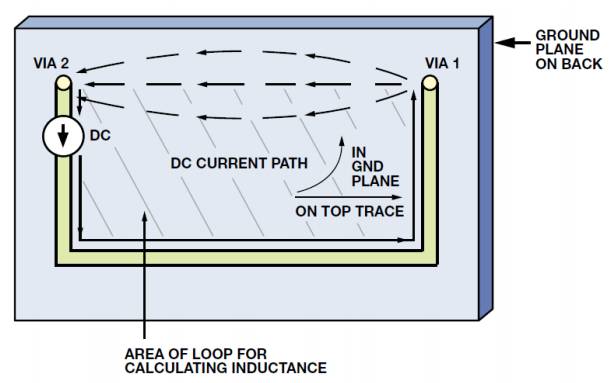

图 5. 图 4 所示 PCB 的直流电流的流动

图 5 所示的直流电流的流动方式,选取了接地层中从过孔 1 至过孔 2 的电阻最小的路径。虽然会发生一些电流扩散,但基本上不会有电流实质性偏离这条路径。相反,交流电流则选取阻抗最小的路径,而这要取决于电感。

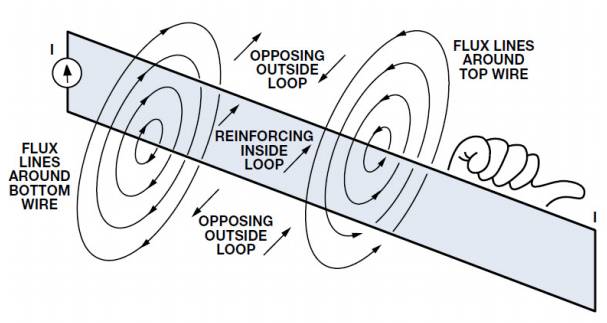

电感与电流环路的面积成比例,二者之间的关系可以用图 6 所示的右手法则和磁场来说明。环路之内,沿着环路所有部分流动的电流所产生的磁场相互增强。环路之外,不同部分所产生的磁场相互削弱。因此,磁场原则上被限制在环路以内。环路越大则电感越大,这意味着:对于给定的电流水平,它储存的磁能(Li2)更多,阻抗更高(XL = jωL),因而将在给定频率产生更大电压。

图 6. 磁力线和感性环路(右手法则)

电流将在接地层中选取哪一条路径呢?自然是阻抗最低的路径。考虑 U 形表面引线和接地层所形成的环路,并忽略电阻,则高频交流电流将沿着阻抗最低,即所围面积最小的路径流动。

在图中所示的例子中,面积最小的环路显然是由 U 形顶部走线与其正下方的接地层部分所形成的环路。图 5 显示了直流电 流路径,图 7 则显示了大多数交流电流在接地层中选取的路径,它所围成的面积最小,位于 U 形顶部走线正下方。实际应用中,接地层电阻会导致低中频电流流向直接返回路径与顶部导线正下方之间的某处。不过,即使频率低至 1 MHz 或 2 MHz,返回路径也是接近顶部走线的下方。

图 7. 接地层中不含电阻(左图)和含电阻(右图)的交流电流路径

采样时钟考量

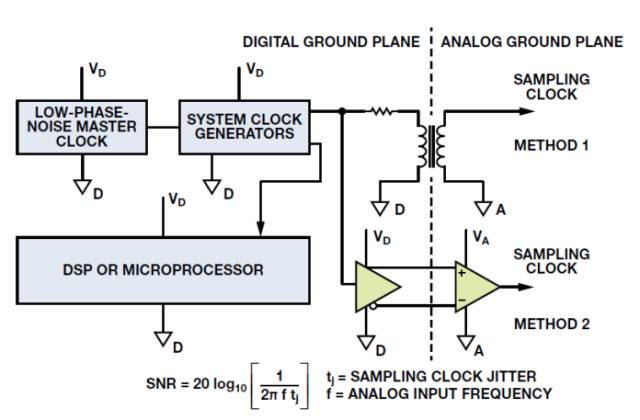

在高性能采样数据系统中,应使用低相位噪声晶体振荡器产生 ADC(或 DAC)采样时钟,因为采样时钟抖动会调制模拟输入/输出信号,并提高噪声和失真底。采样时钟发生器应与高噪声数字电路隔离开,同时接地并去耦至模拟接地层,与处理运算放大器和 ADC 一样。

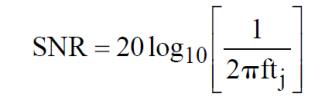

采样时钟抖动对ADC信噪比(SNR)的影响可用以下公式近似计算:

其中,f 为模拟输入频率,SNR 为完美无限分辨率 ADC 的 SNR,此时唯一的噪声源来自 rms 采样时钟抖动 tj。通过简单示例可知,如果 tj = 50 ps (rms),f = 100 kHz,则 SNR = 90 dB,相当于约 15 位的动态范围。

应注意,以上示例中的 tj 实际上是外部时钟抖动和内部 ADC 时钟抖动(称为孔径抖动)的方和根(rss)值。不过,在大多数高性能 ADC 中,内部孔径抖动与采样时钟上的抖动相比可以忽略。

由于信噪比(SNR)降低主要是由于外部时钟抖动导致的,因而必须采取措施,使采样时钟尽量无噪声,仅具有可能最低的相位抖动。这就要求必须使用晶体振荡器。有多家制造商提供小型晶体振荡器,可产生低抖动(小于 5 ps rms)的 CMOS 兼容输出。

理想情况下,采样时钟晶体振荡器应参考分离接地系统中的模拟接地层。但是,系统限制可能导致这一点无法实现。许多情况下,采样时钟必须从数字接地层上产生的更高频率、多用途系统时钟获得,接着必须从数字接地层上的原点传递至模拟接地层上的ADC。两层之间的接地噪声直接添加到时钟信号,并产生过度抖动。抖动可造成信噪比降低,还会产生干扰谐波。

通过使用小型射频变压器(如图8所示)或高速差分驱动器和接收机,将采样时钟信号作为差分信号传输,可在一定程度上解决这个问题。如果使用后者,应该选择ECL来最大程度地减小相位抖动。在单个+5 V电源系统中,ECL逻辑可在地面和+5 V(PECL)之间连接,输出端交流耦合到ADC采样时钟输入。不管是哪种情况,原始主系统时钟必须从低相位噪声晶体振荡器产生。

图 8. 从数模接地层进行采样时钟分配

审核编辑:黄飞

-

如何确保电能质量在线监测装置运行日志的准确性?2025-12-17 732

-

确保X光设备检测的有效性和准确性的关键技巧2025-11-18 574

-

如何保障电能质量监测装置的准确性?2025-09-23 1076

-

如何确保电能质量在线监测装置的数据校验的准确性?2025-09-18 756

-

测缝计测量数据的准确性和校准方法解析2025-07-07 807

-

如何提高电位测量准确性2024-12-28 1717

-

如何提升ASR模型的准确性2024-11-18 3614

-

如何保证测长机测量的准确性?2024-10-25 1643

-

影响电源纹波测试准确性的因素2024-08-02 2019

-

测量时钟信号的探头要求:确保准确性与稳定性2024-04-22 2159

-

拉力试验机夹具的重要性:如何确保测试的准确性和可靠性?2023-06-27 1997

-

如何确认延时函数时间的准确性?2022-01-27 2412

-

检查其可用性和准确性确保PCB设计成功2019-10-31 2409

-

如何提高投标报价编制的准确性2010-01-08 816

全部0条评论

快来发表一下你的评论吧 !