FPGA布局布线优化方案

可编程逻辑

描述

大多数为FPCA布局图(通常认为两个主要的布局图阶段:布局和布线)的实现工具提供设计者成打的优化选项,设计者利用这些选项运行中的问题类似于用综合优化运行中的问题,即一般不完全理解所有这些选项的含义。所以,一些优化常常利用在不需要它们的地方,对性能有显著影响的其他优化则没有利用。

本章描述布局布线优化最重要的方面,提供实际的立即可以被读者利用的探索。在这章的课程期间,将讨论以下的内容:

在布局布线之前产生优化的约束

布局和布线之间的关系。

用逻辑复制减少布线延时

把寄存器封装进 I/O 缓冲器

封装因子的用途

当封装逻辑进 RAM 时

寄存器排序

改变布局的种子

与布局布线的指导更大的一致

1.优化约束

在着手实际的布局布线优化本身之前,强调定义一组完全的时序约束的重要性是必要的。这个内容首先列出的原因是要保证,在本章中包含的优化直到足够的时间已经花费在产生准确的设计约束后才讲述。

应该在任何优化发生之前产生一组完全的约束

对每个设计必须包含的约束包括全部时钟的定义、VO延时、引脚位置、以及任何放宽的含有多周期和假路径的约束。虽然一个实际的路径可能不是关键的时序路径,常常对无关路径放宽技术要求,布局和布线资源可能对更多的关键路径是随意的。关于这些约束的更多信息见第18 章。

常常不被FPGA典型的时序分析覆盖的一类约束(不包含在第18章)包括电压和温度技术条件。电压/温度技术条件在这组约束中间是最常被设计者忽略的,但是在许多情况提供最方便的方式达到显著的时序改善。

大多数设计者知道,所有的FPGA器件(类似大多数半导体器件)规定最坏条件的电压和温度,在这些条件下器件可以运行。从FPCA时序分析的角度,最坏条件的温度是最高的温度,最坏条件的电压是最低的电压,因为这二者的约束将增加传播延时(一般不担忧FPGA中的保持延时,因为最小的延时建立在布线矩阵中)。例如,XilinxFPGA高端的商用温度范围是85℃,最坏条件的电压标称值通常在推荐的运行电压的5%和10%之间变化,对应地有1.2V电源电压近似为1.14V,3.3V电源电压近似为3V,依此类推。

当执行最坏条件的时序分析时,这些情况的电压和温度条件缺省被使用。但是,几乎没有系统要求FPCA运行在85℃(FPGA的结温度)和电源电压下降10%的极端条件。事实上,大多数系统只经历远低于极端的条件。

如果 FPGA 运行其中的系统设计在确定的温度和电压条件内,则FPGA时序分析可以并且应该在相同的条件下执行。

当注意到这个时,许多工程师发现,可以把全部纳秒从关键路径削去(当然取决于器件的工艺),如果时序冲突比这个增量改善少的时候,工程师发现与时序冲突的斗争实际不存在。

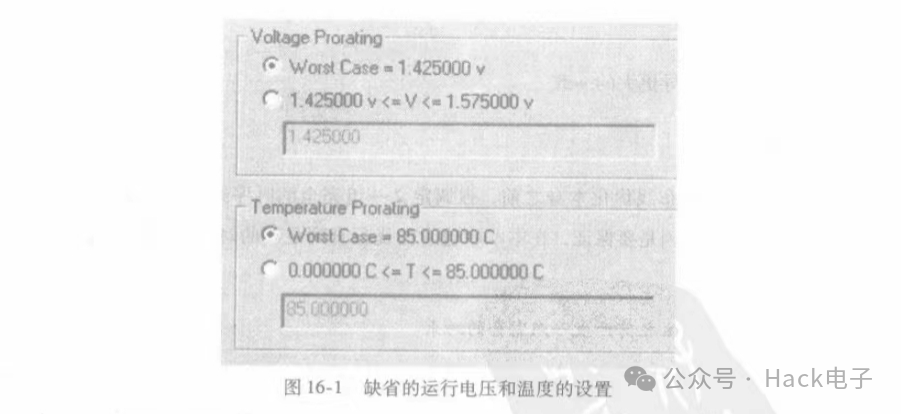

考虑16位计数器的例子,在缺省时序分析条件下,这个计数器在VirtexⅡ器件中运行在276MHz。在图16-1的菜单中表示缺省的电压和温度设置,它们将传递到Xiinx的时序分析工具。

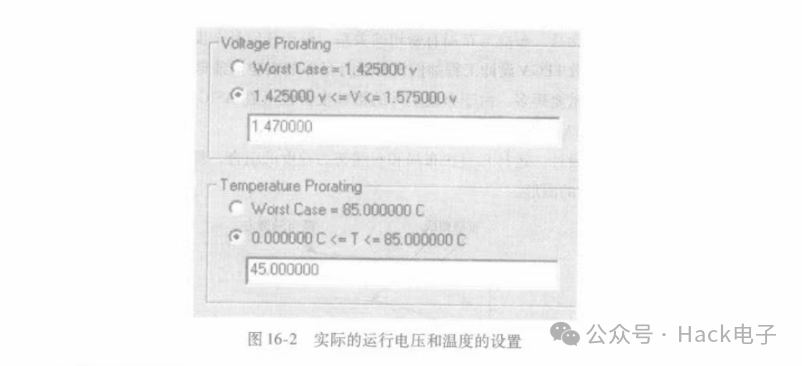

在这个情况中,最坏条件的电压设置为规定的供电电压的95%,5%的电压变化对开关电源是合理的,但是如果这是线性电源的运行偏离,可以比足够的电流更多的提供给芯核,这个技术条件是过多的。此外,结温度设置在85℃,功能设计大概不会产生这样一个温度,因此这个技术条件又是过多的。对假定的“轻便”系统可以减少这些要求到更合理的参数,其中供电电压只变化2%,温度从不超过45℃(图16-2)。

结果是计数器现在运行在290MHz之下。这个性能改善不要求FPGA任何实际的改变,只是在正确的条件下分析设计的简单事情。

调整电压和温度设置不要求FPGA 实现任何改变,可以提供一个方便的手段增量地改善最坏条件的性能。

这种方法的唯一缺点是,在厂商允许存取到这个选项之前,器件需要按照电压和温度完全表征。由于在FPCA厂商之间持续的竞争,在他们的竞争之前生产更快的FPGA,一般在器件特性已经完成之前释放器件。事实上,如果已经利用新品种工艺,通常可以计及没有生效的这个选项。在时序分析工具中,这个选项是不可使用的。这是利用一个带适度成熟的器件的优点之一

2.布局和布线之间的关系

大多数现代的FPGA布局布线工具做很好的工作,达到时序与自动算法一致,因此人工布局和/或布线不再是平常的。但是,许多FPCA设计工程师已经被自动实现工具“损害”到除了极高速设计之外从不考虑布局图的程度。缺少这方面的注意已经产生缺乏理解,所以十分无效地利用各种对布局图有效地实现选项。目标为速度或面积的所有这些选项最重要的是与处理器努力有关的布局布线的关系。

特别是我们认为提供给设计者与后端工具的挂钩,允许设计者调整处理器的努力程度和相应的布局布线算法的精致程度。这些选项几乎总是独立地引入和控制,不幸的是由于它们具有

很强的关系。在基本的训练中,工程师们被告知,他们可以增加布局布线的努力来达到更好的结果。我们在实验经历中实践增加努力的程度和观察其改善。实际上,我们看到类似的改善。所以,是什么问题?问题是如果向上调整布线器的努力程度,在有一个最佳布局之前超出平常的努力,实际是浪费时间。因为大多数项目带有最后期限的进度表,大多数FPGA设计者在达到时序闭合之前经历许多次迭代,一些事情确实值得考虑。

这里理解的基本概念是,布线与布局有密切的关系。对于任何复杂度的设计,好的布线只用好的布局来达到。大多数FPGA设计工程师们没有运行足够的实验来独自地认识这个关系,但是布局比布线对性能是更重要得多。由于布线矩阵的粗粒度特性(在ASIC中有更多的灵活性用布线产生),这特别对FPCA成立。

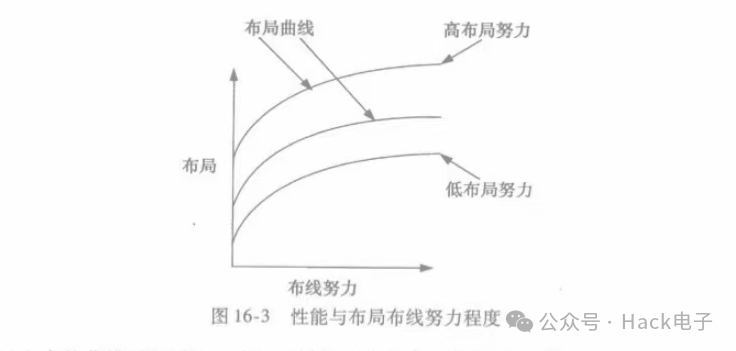

如果做一个典型的设计,运行几百次布局和布线努力程度的组合,然后绘图数据,似乎看到十分类似于图16-3 所示的图形。

从图16-3中的曲线可以看出,布局对设计性能有主要的影响(称它为一阶影响),布线有相对小的影响。

布局努力对性能有主要的影响,而布线努力有相对小的影响。

为了决定最佳的布局布线努力程度,设计者应该遵循这个过程:

1)设置布局布线努力程度为最小。2)运行布局布线确定是否最坏条件的时序是由于次优的布局图,不是由于过大的逻辑层次。

3)增量布局努力直到时序满足,或者最大的努力已经达到。

4)如果最大布局努力的时序不满足,开始增量地增加布线的努力。

5)如果时序闭合不可以满足,重新回到设计的结构。

6)如果要求高的布线努力来满足时序,回到设计结构优化时序(见第1章)可能是好的主意。

审核编辑:黄飞

-

优化 FPGA HLS 设计2024-08-16 1114

-

FPGA去耦电容如何布局布线2017-08-22 10354

-

PCB布局和布线求解!2018-04-03 5590

-

PCB布局和布线的设计技巧2018-11-22 2853

-

布局布线技术的发展2009-03-25 875

-

高速PCB的布局布线优化2011-09-27 1250

-

FPGA并行时序驱动布局算法2018-02-26 1017

-

在FPGA高速AD采集设计中的PCB布线解决方案浅析2019-03-07 7512

-

FPGA设计的塑封式布局和布线介绍2019-05-17 3768

-

FPGA的布局布线2020-10-25 9313

-

fpga布局布线算法加速2023-12-20 2047

-

FPGA布局布线的可行性 FPGA布局布线失败怎么办2024-03-18 1932

-

FPGA布局布线优化技术2024-03-29 997

-

Vivado之实现布局布线流程介绍2024-12-06 3045

-

深入探讨PCB布局布线的专业设计要点与常见挑战2026-01-04 412

全部0条评论

快来发表一下你的评论吧 !