基于DDS理论的多模式多波形雷达信号源设计

电源设计应用

描述

雷达信号源的设计在雷达测试中有着非常重要的作用。DDS在相对带宽、频率转换时间、相位连续性、正交输出、高分辨力以及集成化等方面都远远超过了传统频率合成技术所能达到的水平,为系统提供了优于模拟信号源的性能。

FPGA具有集成度高、通用性好、设计灵活、编程方便等诸多优点,因此采用AD9854和FPGA来设计雷达信号源。

1 系统方案概述

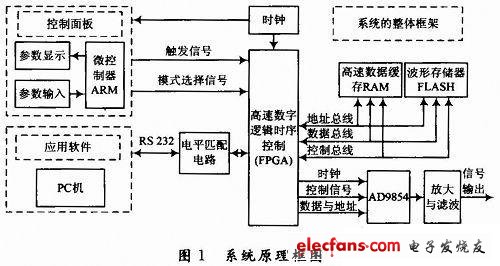

根据雷达信号源系统设计的要求,总体框图如图1所示。

该系统主要由FPGA时序控制部分、AD9854频率合成部分、波形存储三部分组成。在此重点阐述FPGA设计和AD9854硬件设计两部分。

系统的主体部分主要由高速数字逻辑时序控制模块(FPGA)和DDS芯片AD9854构成,还包括放大模块、滤波模块、存储模块、时钟模块、电源模块。该部分通过FPGA对整个电路的数字部分进行时序控制,包括给AD9854发送数据、地址、时钟以及控制信号。AD9854是DDS芯片,能产生所需要的信号。存储部分采用了FLASH和SRAM;FLASH主要用来存储波形文件,而SRAM主要是在开机时暂存数据文件。

通过控制面板发送触发信号和模式选择信号对系统信号产生进行控制。当FPGA接收到触发信号时,FPGA才开始工作,并且给AD9854发送数据以产生信号。模式选择信号是3位的二进制数,可以产生8种状态。控制面板和FPGA通过RS 422电平相连,通过差分数据线来传输数据。

PC机应用软件完成所需各种软件的波形数据的计算,包括起始频率FTW,频率分辨率DFW,时间分辨率RRC等数据,然后将所得的数据转化成.dat格式。PC通过串口与系统主板进行数据通信,通过MAX3232进行电平转化。数据最后存储到主板的存储器中(FLASH和SRAM);当系统工作时,FPGA从FLASH中读取波形文件来产生信号。

2 AD9854模块

2.1 AD9854芯片介绍

数字频率合成芯片AD9854是用于高端DDS技术的一款芯片,该芯片带有两个高速、高性能的正交D/A转换器,可以同时输出I/Q两路正交信号。当参考时钟源很精确时,AD9854能够产生高稳定度的,频率、相位、幅度均可编程的正弦和余弦曲线,被广泛地应用于通信、雷达、仪器等应用领域。AD9854的高速DDS内核能够提供48 B的相位累加器和频率累加器(在300 MHz的系统时钟下,可达1μHz的频率分辨率);其中17 B的相位-幅度映射位数能够确保该芯片优良的无杂散动态范围(SFDR)性能。

2.2 AD9854芯片工作模式

AD9854具有5种可编程操作模式,通过改变控制寄存器(并行寻址方式下的地址为1FH)的控制位即可以选择相应的模式。根据本方案,主要对单频(Single Tone)模式和调频(Chirp)模式进行探讨。5种模式的选择表如表1所示。

2.2.1 单频模式

系统上电或硬件复位时,AD9854自动进入该默认模式,此时芯片输出的信号是直流信号。当对频率控制字进行设定后,即可输出单频信号。

2.2.2 调频模式

此处的调频模式即为常见的脉冲调频模式。AD9854同时支持线性和非线性这两种调频模式。该雷达信号源要求既能产生线性调频信号,也能产生非线性调频信号,所以AD9854完全能满足要求。脉冲调频信号的时宽主要是由update clock来决定。当第一个update clock信号到来时,AD9854把I/O缓存中的FTW,DFW,RRC以及其他的控制字都送到可编程寄存器中,AD9854开始工作。当脉冲调频信号结束时,通过FPGA再发送一个update clock信号,然后就把I/O缓存中的清零数据送入了可编程寄存器中。

3 系统硬件实现

3.1 电源和时钟设计

在该系统中,采用线性电源LT1764进行电平转换,把5 V转成3.3 V和1.5 V,为FPGA和AD9854等芯片提供电源。滤波电容分为旁路电容和去耦电容。旁路电容把前级携带的高频杂波滤去,还可以有效地旁路地和电源上的地弹噪声。旁路电容一般容值都比较小,根据谐振频率一般是0.1μF和0.01μF。去耦电容也称退耦电容,是把输出信号的干扰作为滤除的对象。去耦电容一般比较大,取值为47μF和10μF。如图2所示。

时钟电路与FPGA的电源面要隔离开(可以在同一个层),只通过铁氧体磁珠(ferritebead)相连。铁氧体磁珠在低频时阻抗很低,而在高频时阻抗很高,可以抑制高频干扰,这样外面的高频干扰不会影响时钟芯片,而时钟芯片内部产生的振荡信号也不会影响到外面的电路。时钟部分的地和整个PCB的地是一个统一的整体,不要分割。

在时钟芯片的电源引脚处放一个容值为10μF的钽电容,不仅可以防止由于电压波动引起的电流涌动,还可以抑制低频干扰;同时大电容的后面并联一个0.1μF的小电容,且所放的位置要尽可能地靠近电源引脚,这样可以减小外来的电源噪声。在靠近时钟输出的引脚要串接一个50 Ω的电阻以减小输出电流,提高时钟波形的质量。时钟线尽量少使用过孔,因为过孔使阻抗发生变化,影响信号的质量,进而产生EMI辐射和抖动问题。

3.2 存储模块设计

在该系统中,采用FLASH和SRAM作为存储器。FLASH主要用于存储波形文件,掉电时,数据也不会丢失。而SRAM是做高速数据缓存的,掉电后数据会丢失。首先FPGA从FLASH中读取波形文件,然后再存储到SRAM中,需要这些波形数据时候,再从SRAM中去读取。这样的设计是因为FLASH的读/写速度比较慢,而SRAM的读/写速度比较快。但是FLASH中的数据掉电不会丢失,而SRAM中的数据掉电要丢失。

3.3 放大及滤波电路设计

为了提高DDS信号产生系统的带负载能力,同时实现AD9854芯片内嵌数/模转换器输出的电流转换,需要在其后加入运算放大器(见图3)。该运算放大器性能的好坏将决定信号的输出质量及系统带负载的能力。由于方案中信号输出的最高频率为120 MHz,所以应保证放大器在较高频率范围内具有很好的线性度,防止放大器自激。根据频率源的设计要求,该方案中的放大器模块应满足以下要求:放大器的增益可调、放大器的带宽应大于120 MHz、输出带载能力强、信号输出质量较好。综合以上要求,选择ADI公司的宽带运算放大器AD8014作为放大器模块的核心器件。AD8014的主要性能特点有:低功耗;稳定增益G=1;高速,Slew Rate 4 000 V/μs,24 ns的建立时间;

在该方案中,放大电路采用串连电压负反馈-反相比例放大电路。

采用串联电压负反馈将使放大器的输入阻抗增大,输出阻抗减小,提高电路输出信号的带负载的能力。在电路中,反馈电阻R16采用可调电阻,使电路的增益可调;同时在放大器的正、负电源输入端加电容去藕滤波电路,以减小电源纹波对放大器的影响。

根据AD8014的要求,在进行PCB布线时,需在其周围均铺上了地网;但是,为了降低寄生电容对电路输入的影响,其输入脚附近没有铺地。在进行器件布局时,反馈电阻R16应尽量靠近AD8014的反向输入端。

为使中频模拟器有较好的通用性,而雷达中频变化范围较宽,考虑到在滤除谐波分量的同时要尽可能减少相位的不连续性,因此设计了一个带宽为40MHz的9阶无源低通滤波器。

4 FPGA实现

4.1 FPGA设计概述

FPGA用于建立与DDS芯片(AD9854),FLASH(E28F128J3A)以及SRAM(IS61LV10248)之间的联系,主要负责以下两个方面:

(1)发送DDS控制字并控制DDS芯片的时序;

(2)控制存储芯片的时序,并发送或读取所要存储的波形数据。FPGA内部采用原理图和Verilog HDL相结合的方式进行软件设计。

下面重点介绍DDS控制部分的实现。

4.2 DDS控制模块

DDS控制模块负责读取片内双口RAM中的DDS控制字,并将AD9854的时序写入DDS芯片,控制DDS的工作。

DDS控制模块在每次写AD9854控制字之前先对RAM发出读使能,同时给出读地址,读取当前控制字,然后按照时序要求写入DDS芯片。Quartus中仿真的时序图如图4所示。

以下将介绍控制AD9854,的流程。

首先对AD9854进行复位,FPGA发送高电平给AD9854第71管脚,高电平持续的时间长度要超过20个周期的AD9854采样时钟。复位信号使AD9854的所有寄存器恢复到默认状态。需要注意的是,复位信号的长度必须满足一定的要求,否则在实际操作中可能会出现错误。

当FPGA接收到外部发送的触发信号以后,DDS控制模块就开始工作了。首先从双口RAM中读取波形数据,包括起始频率(FTW),增量频率字(DFW),斜率时钟(RRC)以及控制信号。DDS控制模块给双口RAM送读使能和读地址,然后把双口RAM中的数据读到数据选择模块中。之后接收波形模式选择信号。这个信号是三位二进制数,总共有8种工作模式,总的来说分为工作模式和测试模式。当系统为工作模式的时候,该系统就是雷达发射机的中频信号模块。在工作模式下,该中频信号模块能发射4种模式的波形:时宽是0.2μs的正弦波,时宽为5μs的线性调频波,时宽为30μs的线性调频波和时宽80μs的线性调频波。当发射信号为时宽是0.2μs的正弦波或时宽为5μs的线性调频波时,对近区的目标进行搜索;当发射信号是时宽为30μs的线性调频波时,对中区的目标进行搜索;当发射信号为时宽为80μs的线性调频波时,对远区的目标进行搜索。当系统为测试模式的时候,也分为时宽为0.2μs,5μs,30μs,80μs这4种模式的信号,但是当信号时宽为0.2μs时,信号中加入了多普勒频率,这样就为信号处理机检测测速单元提供了方便。该系统为测试模式时主要且模拟雷达回波信号的作用。如图5所示。

当接收到模式选择信号以后,DDS控制模块开始给AD9854送数据。这时,FPGA给AD9854传送的数据都保存在I/O缓存区内。接着,FPGA就给AD9854发送update clock。这样,I/O缓存区内的数据就送入AD9854的寄存器中,AD9854开始产生信号。最后,给AD9854的控制寄存器地址为1F的第七位送高电平,这样就把信号清零,从而产生了脉冲信号。

5 系统测试

5.1 系统测试框图

根据该设计系统的设计思想和工作原理,结合系统测试指标要求,提出系统测试方案和使用仪器。测试仪表主要包括信号源、频谱仪、万用表、电源、示波器等。

按照框图连接测试仪表,设置直流电源输出电压为±5 V,通过相应接口送入雷达信号产生器的电源接口。设置信号源,输出中心频率为30 MHz,功率为(0±1)dBm线性调频波。测试时雷达信号产生器工作于外触发模式下,当接收到外部触发信号时开始产生波形。雷达信号源的信号送入示波器(泰克的DPO4104),测试信号的时域参数,包括时宽,幅度,脉冲前后沿,本底噪声等。雷达信号源的信号送入频谱仪(罗德与施瓦茨的频谱仪FSMR)测试信号的频域参数,包括信号的频率、带宽、谐波和带内杂散等。

系统测试框图如图6所示。

5.2 系统测试结果

时域测试结果如图7所示。

图8,图9为频域测试结果。

通过测试结果分析,可见该雷达信号产生器系统可产生多种不同时宽、带宽和脉冲重复频率的LFM、NLFM、脉冲信号,能够满足工程应用的需要。

6 结语

通过对雷达信号源的工程实现进行研究,利用ADI公司的DDS芯片和FPGA实现了多模式多波形的雷达信号源。通过优化硬件设计,改进系统的结构,优化了系统的性能,并给出系统实际测试的结果。为DDS实现雷达信号源提供了设计参考。

-

基于Verilog的多路相干DDS信号源该怎么设计?2019-10-08 2186

-

基于DDS的信号源设计论文资料2017-07-19 1174

-

基于DDS的高性能信号源的设计2016-12-17 945

-

基于DDS的雷达中频信号源设计与实现2016-10-25 945

-

基于DDS技术的多路同步信号源的设计2016-05-27 9161

-

基于AD9959的高精度多通道雷达信号源设计2012-09-24 1709

-

【FPGA参赛作品】基于FPGA的简易DDS信号源设计2012-05-12 103405

-

DDS器件AD9858实现复杂雷达信号源2011-08-24 3279

-

基于DDS的雷达校准信号源设计2011-05-03 848

-

基于FPGA和DDS的信号源设计2010-02-21 2094

-

基于FPGA的DDS信号源设计与实现2010-02-11 956

-

基于AD9959的多体制雷达信号源的设计2009-11-05 3068

-

虚拟多波形信号源的原理和应用2009-06-22 3347

-

用DDS器件AD9858实现复杂雷达信号源 (图)2008-09-22 3668

全部0条评论

快来发表一下你的评论吧 !