如何实现一种基于FPGA的红外线遥控系统设计呢?

描述

前言

红外线(Infrared)是波长介乎微波与可见光之间的电磁波,波长在760纳米(nm)至1毫米(mm)之间,比红光长的非可见光。 红外线遥控是目前使用最广泛的一种通信和遥控手段。由于红外线遥控装置具有体积小、功耗低、功能强、成本低等特点,因而,继彩电、录像机之后,在录音机、音响设备、空凋机以及玩具等其它小型电器装置上也纷纷采用红外线遥控。现在工业设备中,也已经广泛在使用。

设计原理

红外遥控系统主要由红外的发送装置和接收装置组成,发送装置可由按键,编码模块,发射电路等组成,接收装置由红外接收电路,遥控,解码模块等组成,此次设计我们用到的硬件平台式是Altera的DE1_SOC,晶振为50MHZ。

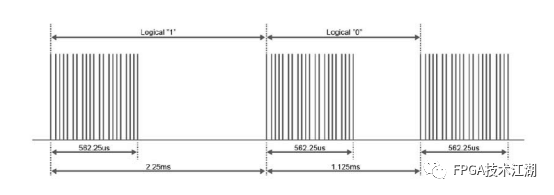

在红外的编码中,我们对1 和 0 的编码是通过38KHZ的脉冲来定义的,在红外的的编码中每个脉冲的为256.25us长的38KHZ载波频率(26.3us),对0,1的脉冲的定义的时间如下图:

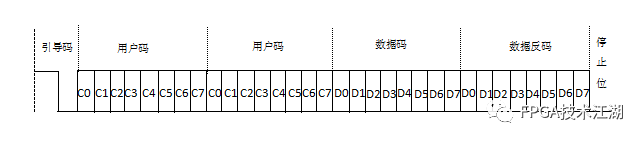

红外的数据格式为包括引导码,用户码,数据码和数据纠错码,停止位编码总为32位。数据反码是数据码反相后的编码,可用于对数据的纠错。此外第二段的用户码可以在遥控应用电路中设置为第一段用户码的反码。

数据格式如下图:

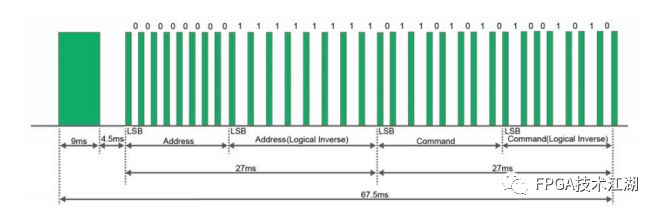

一帧数据在发送时先发送9MS的高电平,然后发送4.5MS的低电平的起始位,然后发送用户码,数据码,数据反码。然后再发送一位的停止位。不发送数据时数据线一直为低。

发送的时序图如下:

接受的时,接收到的时序和发送的时序恰恰相反,如发送时先发送9ms的高,4.5ms的低,接收为接收9ms的低电平,4.5ms低电平。

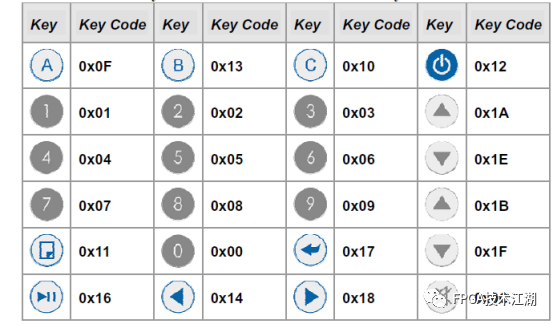

接收的控制器我们用的时红外遥控装置,按键发送的数据如下图所示:

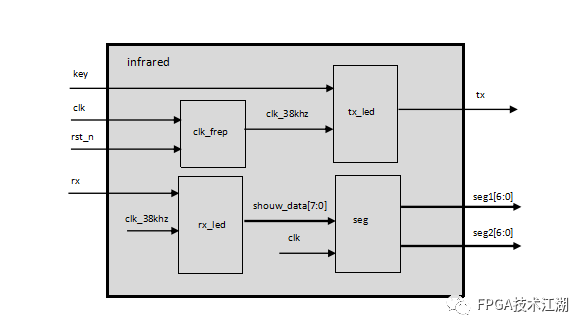

设计框架

设计的总框架如下图:

在设计中分频模块提供所需要的38KHZ的时钟,当按键按下时发送我们的发送模块发送一个给定的数值,我用户码为8'b0,第二段用户码为8'hff,然后发送给定的数据码,和数据反码。上电后我们的设计会发一次我们给定的数据码,然后在接受模块会接受到其发送的数据并在数码管上显示出来,之后我们可以用我们我的遥控键盘来发送数据,接收模块接收显示出来,通过验证我们接收和发送的正确。

设计代码

顶层模块infrared代码:

module infrared(clk, rst_n, key, tx, seg1, seg2, rx);

input clk, rst_n;

input key;

output tx;

input rx;

wire [7:0] show_data;

output [7:0] seg1,seg2;

wire [31:0] data_n;

wire clk_38khz;

clk_frep clk_frep_dut(

.clk(clk),

.rst_n(rst_n),

.clk_38khz(clk_38khz)

);

encode encode_dut(

.clk(clk_38khz),

.rst_n(rst_n),

.d_out(data_n),

.key(key)

);

tttxxx tx_dut(

.clk(clk_38khz),

.rst_n(rst_n),

.data_n(data_n),

.tx(tx),

.key(key)

);

seg seg01(

.clk(clk),

.rst_n(rst_n),

.seg7(seg1),

.data_in(show_data[3:0])

);

seg seg02(

.clk(clk),

.rst_n(rst_n),

.seg7(seg2),

.data_in(show_data[7:4])

);

rx_led led_dut(

.clk(clk_38khz),

.rst_n(rst_n),

.rx(rx),

.show_data(show_data)

);

endmodule

发送模块tttxxx代码:

module tttxxx(clk, rst_n, data_n, tx, key);

input clk, rst_n;

input key;

input [31:0] data_n;

output reg tx;

reg [31:0] temp;

reg [8:0] count;

reg [2:0] state;

reg data;

reg [13:0] num;

reg [31:0] d_data;

parameter T9ms = 342; //9000/26.3;

parameter T4500us = 171; //4500/26.3;

parameter T0 = 21; //(1125-562.25)/26.3;

parameter T1 = 63; //(2250-562.25)/26.3;

parameter T562us = 21; //562.25/26.3;

parameter T = 2666;

reg T9_flag;

reg T45_flag;

reg T0_flag;

reg T1_flag;

reg T9_down;

reg T45_down;

reg T0_down;

reg T1_down;

reg [9:0] cnt9;

reg [9:0] cnt45;

reg [9:0] cnt0;

reg [9:0] cnt1;

reg [9:0] cnt562;

reg t0_clk, t1_clk;

always @ (posedge clk)

if(!rst_n)

begin

count <= 0;

state <= 0;

tx <= 0;

data <= 0;

num <= 0;

temp <= 0;

d_data <= {8'b0,8'hff, 8'b10100010, 8'b01011101};

end

else

case (state)

0 : if(count < 10)

begin

tx <= 0;

count <= count + 1;

end

else if(!key)

begin

count <= 0;

state <= 1;

T9_flag <= 1;

tx <= 1;

end

1 : if(T9_down)

begin

state <= 2;

T45_flag <= 1;

tx <= 0;

T9_flag <= 0;

end

else

begin

tx <= 1;

state <= 1;

end

2 : if(T45_down)

begin

state <= 3;

tx <= 0;

T45_flag <= 0;

end

else

tx <= 0;

3 : if(count < 32)

begin

count <= count + 1;

if(!d_data[31 - count])

begin

T0_flag <= 1;

state <= 4;

T1_flag <= 0;

end

else

begin

T1_flag <= 1;

state <= 5;

T0_flag <= 0;

end

end

else

begin

count <= 0;

state <= 6;

T0_flag <= 0;

T1_flag <= 0;

end

4 : if(T0_down)

begin

state <= 3;

tx <= 0;

end

else

begin

tx <= t0_clk;

end

5 : if(T1_down)

begin

state <= 3;

tx <= 0;

end

else

tx <= t1_clk;

6 : if(count < T562us - 1)

begin

count <= count + 1;

tx <= 1;

end

else

begin

tx <= 0;

end

default: state <= 0;

endcase

always @ (posedge clk)

if(!rst_n)

begin

T9_down <= 0;

cnt9 <= 0;

end

else if (T9_flag)

begin

if(cnt9 < T9ms - 1)

begin

T9_down <= 0;

cnt9 <= cnt9 + 1;

end

else

begin

T9_down <= 1;

cnt9 <= 0;

end

end

always @ (posedge clk)

if(!rst_n)

begin

T45_down <= 0;

cnt45 <= 0;

end

else if (T45_flag)

begin

if(cnt45 < T4500us - 1)

begin

T45_down <= 0;

cnt45 <= cnt45 + 1;

end

else

begin

T45_down <= 1;

cnt45 <= 0;

end

end

reg [9:0] cnt00;

always @ (posedge clk)

if(!rst_n)

begin

t0_clk <= 0;

T0_down <= 0;

cnt0 <= 0;

cnt00 <= 0;

end

else if (T0_flag)

begin

if(cnt0 < T562us - 1)

begin

t0_clk <= 1;

cnt0 <= cnt0 + 1;

T0_down <= 0;

end

else

begin

if(cnt00 < T0 - 1)

begin

cnt00 <= cnt00 + 1;

t0_clk <= 0;

T0_down <= 0;

end

else

begin

T0_down <= 1;

cnt0 <= 0;

cnt00 <= 0;

end

end

end

reg [9:0] cnt11;

always @ (posedge clk)

if(!rst_n)

begin

t1_clk <= 0;

T1_down <= 0;

cnt1 <= 0;

cnt11 <= 0;

end

else if (T1_flag)

begin

if(cnt1 < T562us - 1)

begin

t1_clk <= 1;

cnt1 <= cnt1 + 1;

T1_down <= 0;

end

else

begin

if(cnt11 < T1 - 1)

begin

cnt11 <= cnt11 + 1;

t1_clk <= 0;

T1_down <= 0;

end

else

begin

T1_down <= 1;

cnt1 <= 0;

cnt11 <= 0;

end

end

end

endmodule

接收模块rx_led代码:

0 module rx_led(clk, rst_n, rx, show_data);

1

2 input clk, rst_n;

3 input rx;

4 output reg [7:0] show_data;

5

6 reg [1:0] state;

7 reg [7:0] cnt;

8 reg temp;

9 reg [9:0] num;

10 reg flag;

11 reg [31:0] data;

12 reg [1:0] state_s;

13 reg flag_x;

14 reg [12:0] count;

15

16 parameter T = 2566; // 一帧数据的时间

17

18 //这个模块是中因为接受的32位编码数据中,不管是位0还是位1,接受的低电平都是相同的,

19 //我们可以通过来判断高电平的时间来确定为位1 还是位0,位’1‘ 1.68MS,位0 562.25us

20 always @ (posedge clk)

21 if(!rst_n)

22 begin

23 num <= 0;

24 data <= 0;

25 state_s <= 0;

26 flag_x <= 0;

27 count <= 0;

28 end

29 else

30 begin

31 case (state_s)

32 0 : if(!rx) //判断起始位,是否接受=收数据

33 begin

34 state_s <= 1;

35 flag_x <= 0;

36 count <= count + 1;

37 end

38 else

39 begin

40 flag_x <= 0;

41 state_s <= 0;

42 count <= count + 1;

43 end

44

45 1 : if(num < (342 + 171 - 1)) //延迟9ms + 4.5ms的起始时间

46 begin

47 num <= num + 1;

48 state_s <= 1;

49 count <= count + 1;

50 end

51 else

52 begin

53 num <= 0;

54 state_s <= 2;

55 count <= count + 1;

56 end

57

58 2 : if(flag && num < 32) //flag来的时候表示接到了位1 ,或者位0,

59 //通过移位寄存器来获取32位数据

60 begin

61 data <= {data[30:0],temp};

62 state_s <= 2;

63 num <= num + 1;

64 count <= count + 1;

65 end

66 else if(num == 32)

67 begin

68 state_s <= 3;

69 num <= 0;

70 count <= count + 1;

71 end

72 else

73 state_s <= 2;

74

75 3 : if(num < 21 - 1) //延迟结束位的时间

76 begin

77 num <= num + 1;

78 count <= count + 1;

79 end

80 else

81 begin

82 if(count == T - 1) //延迟一帧数据的时间后,发送一个标志位

83 begin

84 num <= 0;

85 state_s <= 0;

86 flag_x <= 1;

87 count <= 0;

88 count <= count + 1;

89 end

90 else

91 count <= count + 1;

92 end

93 default: state_s <= 0;

94 endcase

95 end

96

97 always @ (posedge clk)

98 if(!rst_n)

99 begin

100 cnt <= 0;

101 state <= 0;

102 temp <= 0;

103 flag <= 0;

104 end

105 else

106 if(state_s > 1 && state_s < 3)

107 case (state)

108 0 : if(rx)

109 begin

110 cnt <= cnt + 1;

111 state <= 1;

112 flag <= 0;

113 end

114 else

115 begin

116 state <= 0;

117 flag <= 0;

118 end

119

120 1 : if(!rx)

121 begin

122 cnt <= cnt;

123 state <= 2;

124 end

125 else

126 cnt <= cnt + 1;

127

128 2 : if(400 < cnt * 26 && cnt * 26 < 600) //判断高电平的时间

129 begin

130 temp <= 0;

131 flag <= 1;

132 state <= 0;

133 cnt <= 0;

134 end

135 else if (1400 < cnt * 26 && cnt * 26 < 1700) //判断高电平的时间

136 begin

137 temp <= 1;

138 flag <= 1;

139 state <= 0;

140 cnt <= 0;

141 end

142 else

143 begin

144 state <= 0;

145 cnt <= 0;

146 end

147 default: state <= 0;

148 endcase

149

150 always @ (*) //接收完一帧数据后,当标志位来的时候通过对数据的纠错来捕获数据

151 //我们接收的数据用的是左移,而发送的时候先发的是低位

152 if(!rst_n)

153 show_data <= 0;

154 else if((data[7:0] == ~data[15:8]) && (data[31:24] == ~data[23:16]) && flag_x)

155 begin

156 show_data[0] <= data[15];

157 show_data[1] <= data[14];

158 show_data[2] <= data[13];

159 show_data[3] <= data[12];

160 show_data[4] <= data[11];

161 show_data[5] <= data[10];

162 show_data[6] <= data[9];

163 show_data[7] <= data[8];

164

165 end

166 else

167 show_data <= show_data;

168

169 endmodule

数码管seg模块:

0 module seg(clk, rst_n, seg7, data_in); 1 2 input clk; 3 input rst_n; 4 input [3:0] data_in; 5 6 output reg [7:0] seg7; 7 8 9 `define T1ms 50_000 //分频出1k的时钟 10 //`define T1ms 5 11 reg [15:0] count; 12 reg flag; 13 always @ (posedge clk or negedge rst_n) 14 if(!rst_n) 15 begin 16 count <= 15'b0; 17 flag <= 1; 18 end 19 else 20 if(count == `T1ms /2 - 1) 21 begin 22 count <= 15'b0; 23 flag <= ~flag; 24 end 25 else 26 begin 27 count <= count + 1'b1; 28 end 29 30 always @ (posedge flag) 31 if(!rst_n) 32 seg7 <= 8'b1010_0100; 33 else 34 begin 35 case (data_in) 36 0:seg7 <= 8'b1100_0000; 37 1:seg7 <= 8'b1111_1001; 38 2:seg7 <= 8'b1010_0100; 39 3:seg7 <= 8'b1011_0000; 40 4:seg7 <= 8'b1001_1001; 41 5:seg7 <= 8'b1001_0010; 42 6:seg7 <= 8'b1000_0010; 43 7:seg7 <= 8'b1111_1000; 44 8:seg7 <= 8'b1000_0000; 45 9:seg7 <= 8'b1001_0000; 46 10:seg7 <= 8'b1000_1000; 47 11:seg7 <= 8'b1000_0011; 48 12:seg7 <= 8'b1100_0110; 49 13:seg7 <= 8'b1010_0001; 50 14:seg7 <= 8'b1000_0110; 51 15:seg7 <= 8'b1000_1110; 52 default:; 53 endcase 54 end 55 56 endmodule

分频模块clk_frep代码:

0 module clk_frep(clk, rst_n, clk_38khz); 1 2 input clk, rst_n; 3 output reg clk_38khz; 4 5 reg [9:0] count; 6 7 //分频出红外模块所用的38Khz的时钟 8 //也可以用占空比为1:3的38khz的时钟 9 10 always @ (posedge clk or negedge rst_n) 11 if(!rst_n) 12 begin 13 count <= 0; 14 clk_38khz <= 1; 15 end 16 else if(count == (50_000_000 / 38000 / 2 - 1)) 17 begin 18 clk_38khz <= ~clk_38khz; 19 count <= 0; 20 end 21 else 22 count <= count + 1'd1; 23 24 endmodule仿真测试

测试模块infrared_tb代码:

0 `timescale 1ns/1ps 1 2 module infrared_tb(); 3 4 reg clk, rst_n; 5 reg key; 6 wire tx; 7 wire [7:0] show_data; 8 9 //因为我们代码中只发送一次数据,所以可以把key一直拉低 10 11 initial begin 12 clk = 1; 13 rst_n = 0; 14 key = 1; 15 16 #100.1 rst_n = 1; 17 18 #200 key = 0; 19 20 end 21 22 always # 10 clk = ~clk; 23 24 infrared dut( 25 .clk(clk), 26 .rst_n(rst_n), 27 .key(key), 28 .tx(tx), 29 .rx(rx), 30 .seg1(seg1), 31 .seg2(seg2) 32 ); 33 34 endmodule

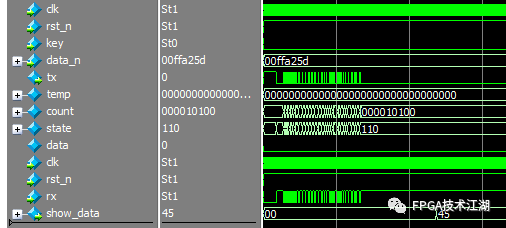

仿真图:

仿真中我们可以把数码管模块的计数器的值改小一点,便于仿真。

如图中所示的我们发的是32’h00ffa25d,那么数据为是8’b1010_0010,那么先发送时就时就按下面的序列开始0100_0101接收到的为45,所以工程正确。

审核编辑:刘清

-

源码系列:基于FPGA的红外线遥控系统设计(附源工程)2024-05-01 1749

-

红外线遥控器使用方法2023-12-20 12295

-

怎样去使用一种红外线遥控器呢2021-11-18 1729

-

红外线的基本特性有哪些2021-02-13 44313

-

红外线遥控系统的设计2020-10-25 3793

-

基于单片机的红外线遥控系统2018-11-05 2825

-

关于红外线遥控的原理分析2018-07-15 5717

-

红外遥控系统的组成及红外线遥控器解码程序的介绍2017-11-16 1738

-

遥控红外线接收头设计实现2017-01-24 1079

-

红外线遥控解码原理2010-08-16 899

-

红外线是什么,红外线简介2010-03-10 3668

-

红外线遥控器解码程序2010-02-02 3749

-

工业控制计算机红外线遥控键盘的设计2009-08-21 541

-

红外线遥控电路图2009-07-08 1591

全部0条评论

快来发表一下你的评论吧 !