FPGA布局布线优化进阶篇

可编程逻辑

描述

逻辑复制

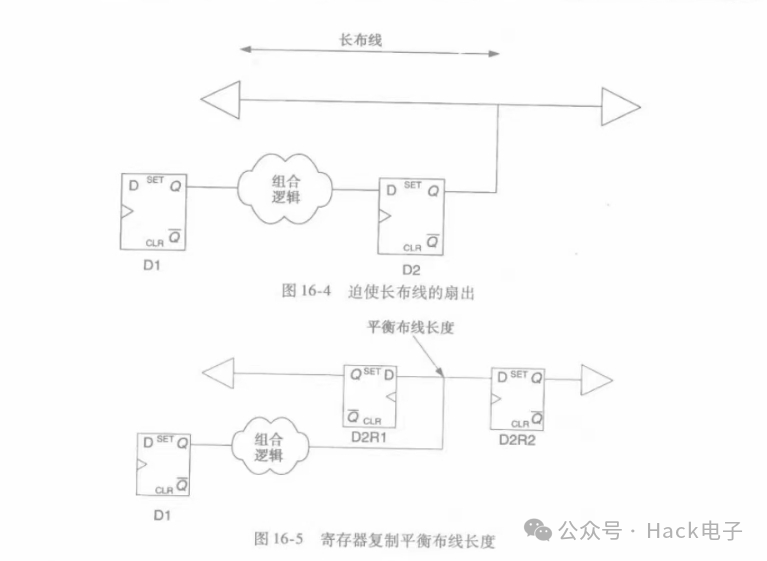

逻辑复制在布局过程的早期发生,为了扇出到其他逻辑元件的结构,这些元件不可以(由于任何理由)存在于相同的近邻。这里强调的问题在图16-4中说明。在这种情况下,D2的输出扇出到两个相互有一定距离的结构,不管驱动放置在哪里最终的布线是到驱动元件之一的长度,为了消除潜在的长布线延时将复制驱动器,如图16-5所示。

逻辑复制应该只利用在关键路径网线,它带有不可能实际放置的多个负载。

这个复制的效果是各个驱动器可以放置更接近于每个负载,所以最小化布线长度和布线的延时。明显地,这个优化将减少布线延时,但增加面积。如果器件的利用率已经很高时,这个优化可能引起差的结果。如果布局工具不是足够智能到只是对关键路径布线执行这个优化,这个选项可能需要禁止,复制用相应的“don't touch”属性添加到RTL保证综合工具不优化这个复制的结构。

跨层次优化

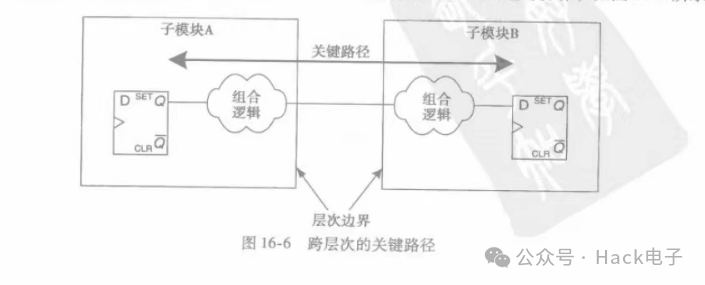

跨层次边界的优化将允许任何布局算法在路径跨模块边界扩展时进行操作,如图16-6所示

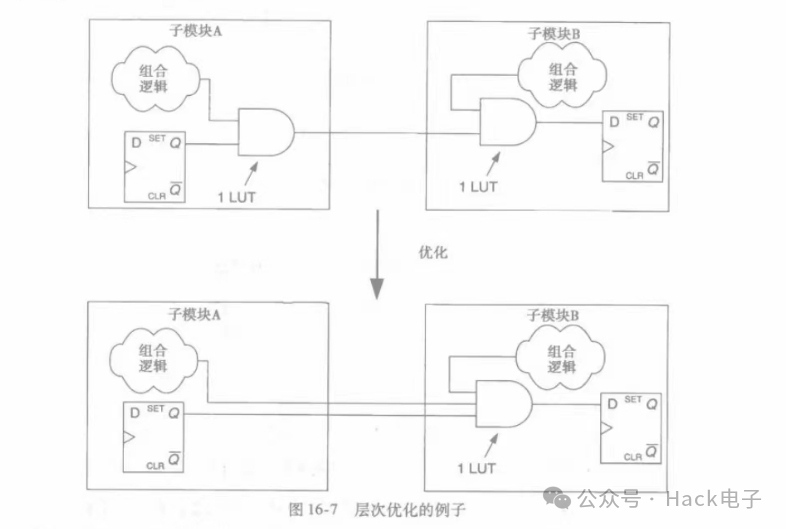

一般地,如果希望一个特定的优化,把它应用到模块之间的接口以及简化模块本身内部的路径是有好处的。常常在模块边界的逻辑没有完全占用整个LUT。一个例子表示在图16-7中。

在这个图的上部,分开的LUT用来在每个模块边界中实现与非(NAND)操作,通过跨边界的优化,每一个逻辑操作可以组合进单个LUT,所以减少这个操作的一半面积利用率。

不希望出现的主要情况是门级仿真需要在实现后的网表上运行。在这个情况中,原封不动的一个层次是十分合乎需要的。

在要求门级仿真时跨层次优化不是合乎需要的。

如果在反向注释的网表上要求诊断,一个保持的层次允许设计者不仅横跨设计,并且也方便识别在模块边界可以为诊断利用的信号。

审核编辑:黄飞

-

RT-Thread驱动开发指南进阶篇-动手驱动先楫未适配的外设LCD2024-02-25 5661

-

【OK210试用体验】进阶篇(2)视频图像采集之MJPG-streamer编译(arm移植)2015-09-20 6387

-

【2017年新资料】《HELLO FPGA》- 项目进阶篇书籍 & 视频下载(包含摄像头/ADDA/HDMI/USB/网络等功能的讲解)2017-01-05 107229

-

《HELLO+FPGA》-项目进阶篇2017-09-27 11456

-

电源设计人员必看资料 开关电源基础知识进阶篇2019-06-19 4900

-

嵌入式工程师资料合集(软件进阶篇)2022-10-12 8912

-

高速PCB的布局布线优化2011-09-27 1246

-

USB HID设备应用(进阶篇)2015-12-07 811

-

Xilinx FPGA设计进阶2015-12-29 696

-

FPGA设计的塑封式布局和布线介绍2019-05-17 3751

-

fpga布局布线算法加速2023-12-20 2028

-

RK3568驱动指南|驱动基础进阶篇-进阶8 内核运行ko文件总结2024-01-31 2434

-

RK3568驱动指南|驱动基础进阶篇-进阶5 自定义实现insmod命令实验2024-02-20 1712

-

FPGA布局布线的可行性 FPGA布局布线失败怎么办2024-03-18 1920

-

RK3568驱动指南|驱动基础进阶篇-进阶7 向系统中添加一个系统调用2025-05-21 820

全部0条评论

快来发表一下你的评论吧 !