数字设计的信号完整性基础知识

模拟技术

描述

1、简介

传统上,数字设计是一件相对不复杂的事情。设计人员可以开发工作频率高达 30 MHz 的电路,而不必担心与传输线路效应相关的问题,因为在较低频率下,信号仍然在数据特性范围内,使系统可以正常运行。然而,随着系统性能的提高,设计者面临的挑战变得更加困难 — 更高的频率对系统的影响意味着设计者不仅要考虑数字特性,还要考虑系统内的模拟效应。

一些最大的设计挑战与 I/O 信号有关,传输线路效应可能对发送的数据产生显著影响。在低速时,频率响应对信号的影响很小,除非传输介质特别长。然而,随着速度的提高,高频效应占据主导地位,即使是最短的线路也会出现振铃、串扰、反射和地弹反射等问题,严重阻碍信号的响应,从而破坏信号完整性。在现实中,这些问题可以通过良好的设计技术和遵循简单的布局准则来克服。Altera 提供了有助于克服这些问题的信息。

传输线路效应

传输线路是能够在发送器和接收器之间传输信号的连接。传统上,传输线路被认为是长距离工作的基于电信的电缆。但随着数字信号的高速传输,即使是最短的无源印刷电路板 (PCB) 走线也会受到传输线路效应的影响。

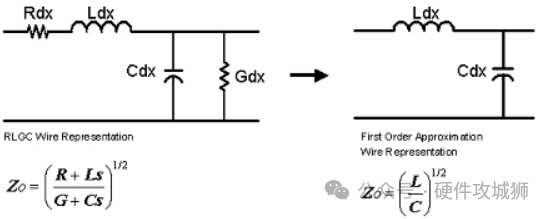

在低频率下,导线或 PCB 走线可能是没有电阻、电容或电感的理想电路。但在高频率下,交流 (AC) 电路特性占主导地位,导致阻抗、电感和电容在导线中普遍存在。如下面的图 1 所示,可以计算一个电路模型,使用它来确定导线或走线的特性阻抗。这个导线阻抗极其重要,因为传输路径中的任何不匹配都将导致信号质量降低。

阻抗不匹配

当源的输出阻抗 (ZS)、线路的阻抗 (ZO) 和接收器或负载的阻抗 (ZL) 不相等时,将导致阻抗不匹配。这意味着传输的信号在接收器内没有被完全吸收,多余的能量将反射回发送器。此过程将反复持续进行,直到所有能量都被吸收为止。在高数据速率下,这会对信号产生危险的影响,导致过冲、下冲、振铃和阶梯波形,所有这些都会在信号中产生错误。

当收发器缓冲区与传输介质匹配时,阻抗不匹配问题就解决了。对于 PCB,这可以通过仔细选择介质和使用适当的端接方案来实现。

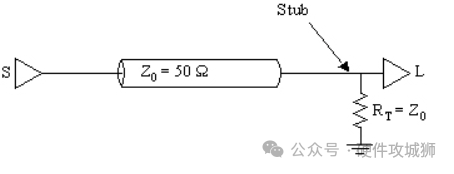

可以使用多种不同的终端方法来克服此问题,具体取决于应用。这些方法可能包括对 Stratix GX 设备进行简单的并行端接(如图 2 所示),还可能包括使用更复杂的阻容 (RC) 端接,其中 RC 网络提供了一个低通滤波器来去除低频效应,但允许高频信号通过。

虽然外部元件通常有助于改善状况,但它们需要 PCB 基板面,还可能需要额外的短桩线,这可能会引入新的问题。

英特尔 FPGA 高速 I/O 解决方案提供了片上可编程端接,以减少对外部元件的需求。Stratix 和 Stratix GX 设备均提供片上端接技术。该技术针对串行和差分 I/O 提供了接收器和发送器驱动器阻抗匹配。Stratix GX 设备上的高速收发器模块在高速收发器电路内额外提供了一个可编程端接方案,可支持大多数高速 I/O 标准。除了端接,还可以使用良好的 PCB 设计技术来克服这些问题。

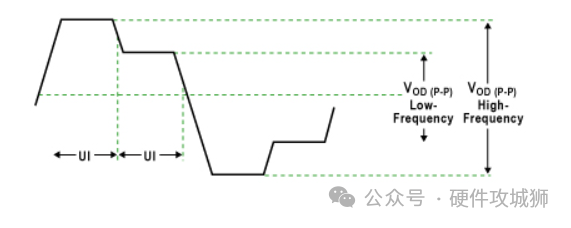

2、信号衰减

高频信号在传输线路上会有损耗,这会干扰接收器解释信息的能力。表 1 列出了用来传输信号的传输介质导致损耗的一些原因。

表 1.传输线路损耗的原因

| 原因 | 描述 |

| 介电吸收 | 高频信号会使绝缘体中的分子变得活跃,导致其吸收信号能量。这使得信号强度降低。介电吸收与使用的印刷电路板 (PCB) 材料有关,可以通过仔细选择材料来改善。 |

| 集肤效应 | 交流和高频信号引起的变化的电流波形往往在导体表面传播。这导致材料的自感以高频率产生更大的感抗,迫使电子流向材料表面。导电面积的有效减少导致电阻增加,从而使信号衰减。增加走线宽度可以减少集肤效应,但这并不总是可行的。图 3 说明了此问题。 |

串扰

每当沿着一条导线驱动信号时,该导线周围都会产生磁场。如果两根导线相邻放置,两个磁场可能会相互作用,导致信号之间的能量交叉耦合,称为串扰。表 3 说明了主要引起串扰的耦合类型。

表 3.导致串扰的耦合类型

| 耦合 | 描述 |

| 互感 | 这是来自驱动导线或干扰源的感应电流的效应,通过磁场出现在安静导线或受干扰线路上。互感导致受干扰线路的近端(最靠近发送器)出现正波,造成近端电感,而传输线路的远端(较靠近接收器)出现负波,造成远端串扰。 |

| 互电容 | 这是两个电场的耦合,其中与驱动器中的电压变化率成正比的电流被注入到受干扰线路中。互电容会导致传输线路的两端都出现正波。 |

仔细的 PCB 设计可以显著降低串扰。以下步骤描述了如何减少微带或带线布局中的串扰:

在布线限制允许的范围内,尽可能扩大信号线之间的间距

设计传输线路,使导线尽可能靠近地平面;这将使传输线路与地平面紧密耦合,并有助于使其与相邻信号去耦

尽可能使用差分布线技术,尤其是对于关键 PCB 走线

将信号线布在不同的层,如果有明显耦合,则使线路相互正交

尽量减小信号之间的平行运行长度;使用短的平行段进行布线,尽量减少网间的长耦合段

3、同时切换输出

随着数字电路速度的提高,输出切换时间缩短。由于负载电容会放电,开关时间越快,输出中产生的瞬态电流越大。如果多个输出同时从逻辑高电平切换到逻辑低电平,电荷将存储在 I/O 负载电容中,流入器件。这个突然的电流会离开器件,经过内部电感流到电路板地,导致电压产生。这导致器件和电路板地之间出现电压差,在高于地平面的 I/O 上短暂产生一个低电压信号。这称为“地弹反射”。反弹效应可能导致输出低电平被电路板上的其他器件视为高电平。

通过遵循 AN 315:高速 FPGA PCB 设计指南 (PDF) 中介绍的一些基于电路板的设计规则,可以减少地弹反射。 Altera 高速解决方案提供了引脚压摆率控制,使设计人员可以降低驱动器的速度,从而减少反弹效应。此外,这些器件还包括多个电源和接地引脚,从而使设计人员可以将高速 I/O 引脚放置在靠近接地引脚的位置,以降低同时切换输出 (SSO) 的效应。 需要一些额外的努力来应对高速设计的挑战,以确保信号完整性。这可以通过遵循一些简单的模拟设计规则和使用仔细的 PCB 布局技术来实现。Altera 高速可编程逻辑器件提供了许多有助于支持高速设计、可编程压摆率控制和片上端接技术的功能,让设计人员的工作更轻松。

审核编辑:黄飞

-

信号完整性测试基础知识2025-04-24 3663

-

PCB信号完整性分析入门2023-06-09 1543

-

信号完整性为什么写电源完整性?2021-11-15 1451

-

电源完整性基础知识2021-11-08 835

-

信号完整性基础知识2019-04-11 2280

-

保障信号完整性,这九大方法不可不知2017-09-13 10444

-

信号完整性分析基础知识2016-01-06 777

-

信号完整性分析2011-11-30 7725

-

信号完整性基础知识与应用技巧2011-09-06 3105

-

信号完整性原理分析2009-11-04 1204

全部0条评论

快来发表一下你的评论吧 !