半导体制造工艺 - 晶圆制造的过程

制造/封装

描述

本文从晶圆制造开始,到光刻,再到蚀刻和离子注入,薄膜沉积,至最后的封装测试,简单而又全面地介绍芯片制造工艺流程。

芯片制造是当今世界最为复杂的工艺过程。这是一个由众多顶尖企业共同完成的一个复杂过程。本文努力将这一工艺过程做一个汇总,对这个复杂的过程有一个全面而概括的描述。

半导体制造工艺过程非常多,据说有几百甚至几千个步骤。这不是夸张的说法,一个百亿投资的工厂做的可能也只是其中的一小部分工艺过程。对于这么复杂的工艺,本文将分成五个大类进行解说:晶圆制造、光刻蚀刻、离子注入、薄膜沉积、封装测试。

半导体制造工艺 - 晶圆制造(Wafer Manufacturing)

晶圆制造(Wafer Manufacturing)又可分为以下5 个主要过程:

(1)拉晶 Crystal Pulling

◈

掺杂多晶硅在1400度熔炼

◈ 注入高纯氩气的惰性气体

◈ 将单晶硅“种子”放入熔体中,并在“拔出”时缓慢旋转。

◈

单晶锭直径由温度和提取速度决定

(2)晶圆切片 (Wafer slicing)

用精密的“锯(Saw)”将硅锭切成独立的晶圆。

(3)晶圆研磨、侵蚀(Wafer lapping,etching)

◈ 切片的晶圆片使用旋转研磨机和氧化铝浆料进行机械研磨,使晶圆片表面平整、平行,减少机械缺陷。

◈ 然后在氮化酸/乙酸溶液中蚀刻晶圆,以去除微观裂纹或表面损伤,然后进行一系列高纯度RO/DI水浴。

(4) 硅片抛光、清洗 (Wafer polishing and Cleaning)

◈ 接下来,晶圆在一系列化学和机械抛光过程中抛光,称为CMP(Chemical Mechanical Polish)。

◈ 抛光过程通常包括两到三个抛光步骤,使用越来越细的浆液和使用RO/DI水的中间清洗。

◈ 使用SC1溶液(氨,过氧化氢和RO/DI水)进行最终清洗,以去除有机杂质和颗粒。然后,用HF除去天然氧化物和金属杂质,最后SC2溶液使超干净的新的天然氧化物在表面生长。

(5) 晶片外延加工 (Wafer epitaxial processing)

◈ 外延工艺(EPI)被用来在高温下从蒸汽生长一层单晶硅到单晶硅衬底上。

◈ 气相生长单晶硅层的工艺被称为气相外延(VPE)。

SiCl4 + 2H2 Si + 4HCl

该反应是可逆的,即如果加入HCl,硅就会从晶圆片表面蚀刻出来。

另一个生成Si的反应是不可逆的:

SiH4 → Si + 2H2(硅烷)

◈ EPI生长的目的是在衬底上形成具有不同(通常较低)浓度的电活性掺杂剂的层。例如,p型晶圆片上的N型层。

◈ 约为晶圆片厚度的3%。

◈ 对后续晶体管结构无污染。

半导体制造工艺 - 光刻 (Photolithography)

近年大量提及的光刻机,只是众多工艺设备中的一个。即使是光刻,也有很多的工艺过程和设备。

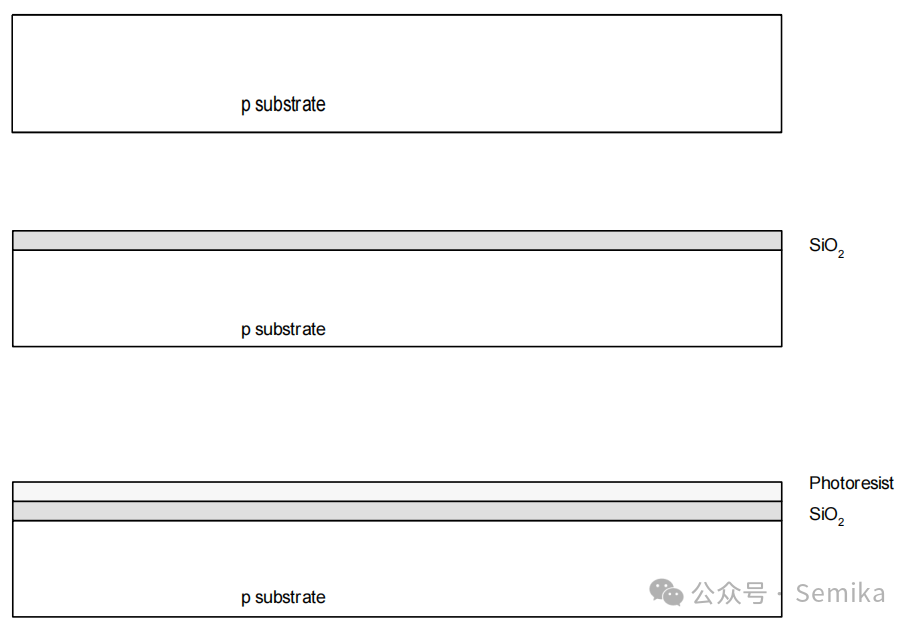

(1)光刻胶涂层 Photoresist coating

光刻胶是一种光敏材料。将少量光刻胶液体加在晶圆片上。晶圆片在1000到5000 RPM的速度下旋转,将光刻胶扩散成2到200um厚的均匀涂层。

光刻胶有两种类型:负胶和正胶。

正胶:暴露于光下可以分解复杂的分子结构,使其易于溶解。

负胶:曝光使分子结构变得更复杂,更难以溶解。

每个光刻步骤所涉及的步骤如下

◈ 清洁晶圆片

◈ 沉积屏障层SiO2,Si3N4,金属

◈ 涂上光刻胶

◈ 软烤

◈ 对齐蒙版

◈ 图形曝光

◈ 显影

◈ 烘焙

◈ 蚀刻

◈ 去除光刻胶

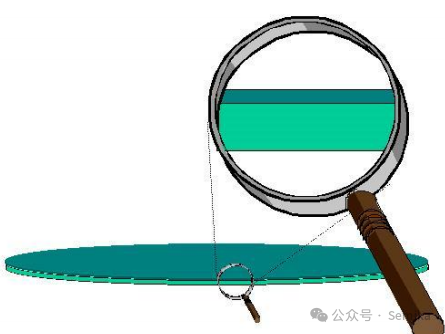

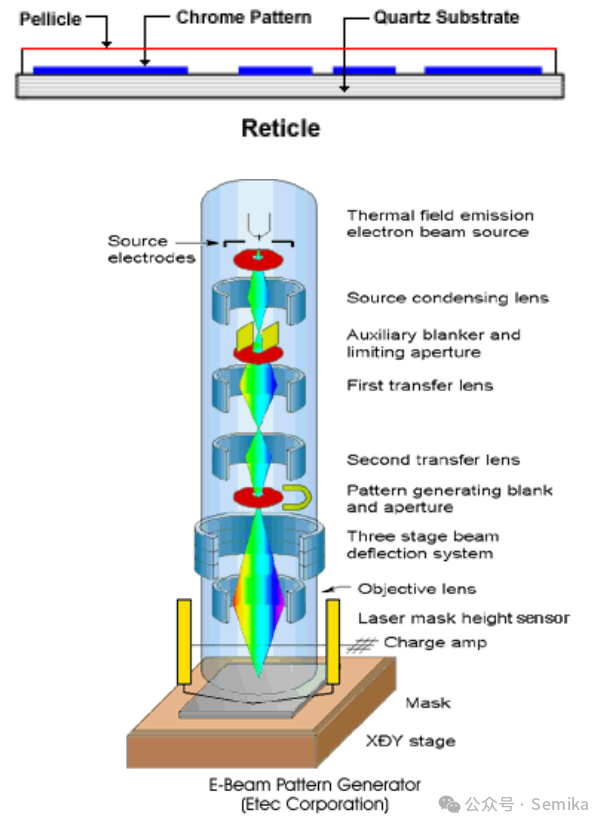

(2)图案准备 Pattern Preparation

IC设计人员使用CAD软件设计每层的图案。然后使用激光图案发生器或电子束将图案转移到具有图案的光学透明石英衬底(模板)上。

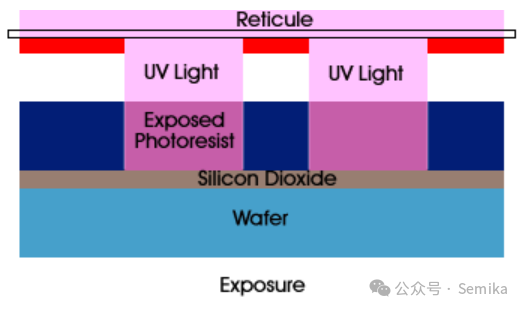

(3)图案转移(曝光)

这里使用光刻机,将图案从模板上,投影复制到芯片层板上。

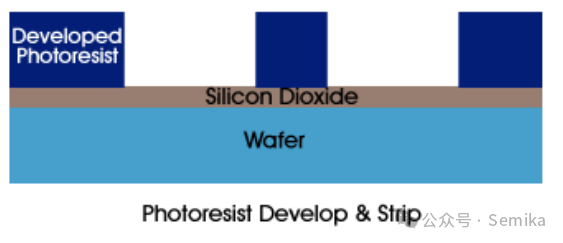

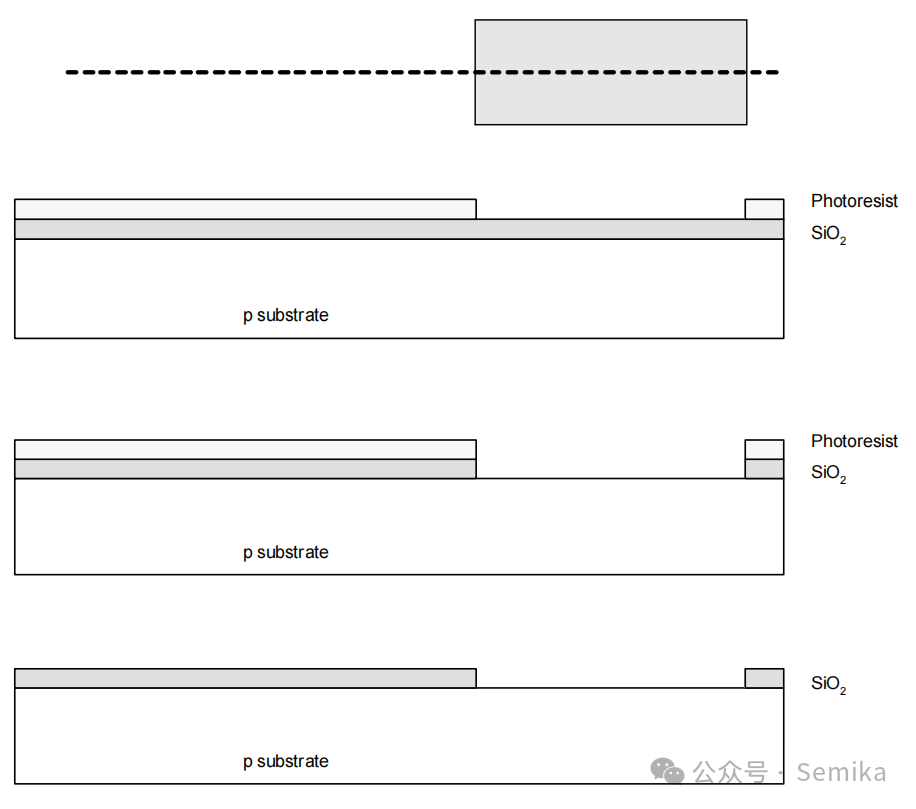

(4)显影、烘烤

◈ 曝光后,晶圆片在酸溶液或碱溶液中显影,以去除光刻胶的暴露区域。

◈ 一旦除去暴露的光刻胶,晶圆片将在低温下“烘烤”以硬化剩余的光刻胶。

半导体制造工艺 - 蚀刻和离子注入 (Etching and Ion Implantation)

(1)湿式和干式蚀刻

◈ 在大型湿平台上进行化学蚀刻。

◈ 不同类型的酸,碱和苛性碱溶液用于去除不同材料的选定区域。

◈ BOE,或缓冲氧化物蚀刻剂,由氟化铵缓冲的氢氟酸制备,用于去除二氧化硅,而不会蚀刻掉底层的硅或多晶硅层。

◈ 磷酸用于蚀刻氮化硅层。

◈ 硝酸用来蚀刻金属。

◈ 用硫酸去除光刻胶。

◈ 对于干式蚀刻,晶圆片被放置在蚀刻室中,通过等离子体进行蚀刻。

◈ 人员安全是首要问题。

◈ 许多晶圆厂使用自动化设备执行蚀刻过程。

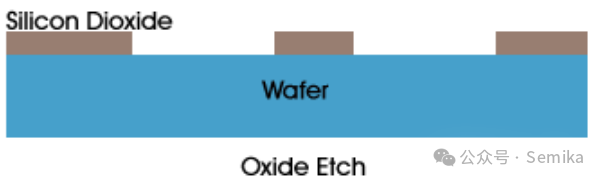

(2)抗蚀剂剥离

然后光刻胶完全从晶圆上剥离,在晶圆上留下氧化物图案。

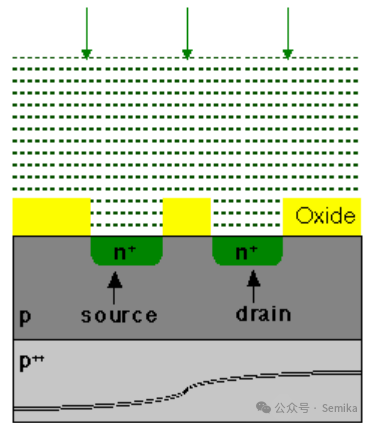

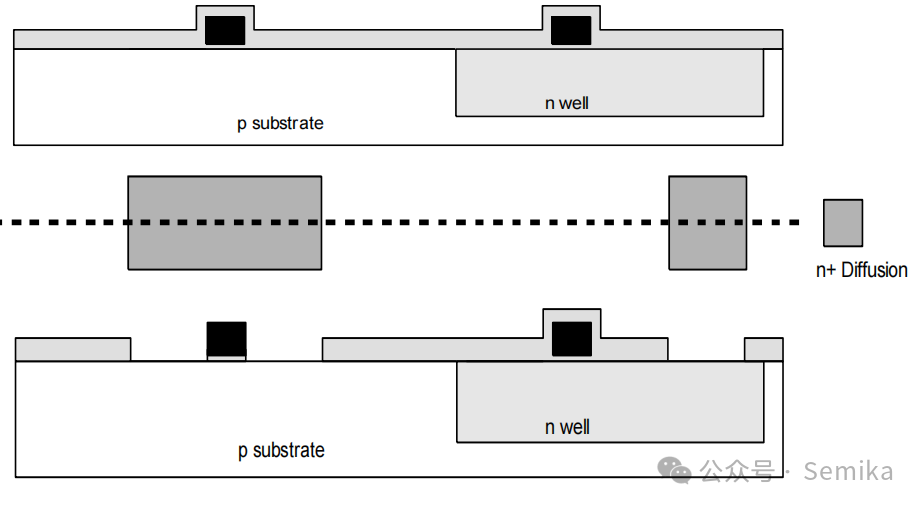

(3)离子注入

◈ 离子注入改变晶圆片上现有层内精确区域的电特性。

◈ 离子注入器使用高电流加速器管和转向聚焦磁铁,用特定掺杂剂的离子轰击晶圆表面。

◈ 当掺杂化学物质沉积在表面并扩散到表面时,氧化物充当屏障。

◈ 将硅表面加热到900℃来进行退火,注入的掺杂离子进一步扩散到硅片中。

半导体制造工艺 - 薄膜沉积 (Thin Film Deposition)

薄膜沉积的方式和内容也比较多,下面逐个说明:

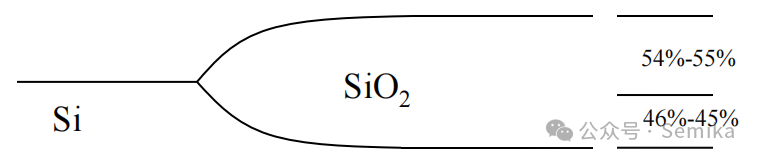

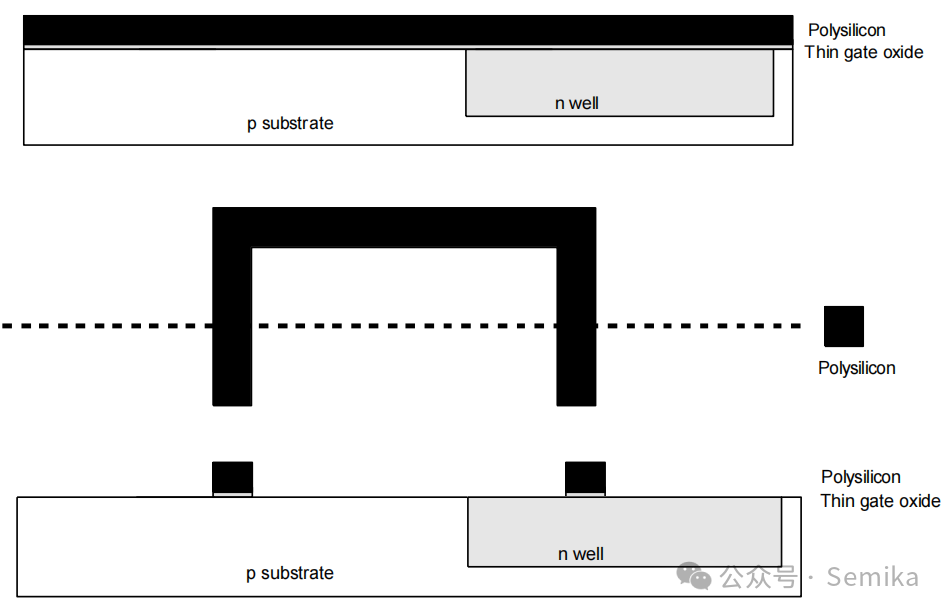

(1)氧化硅

当硅在氧气中存在时,SiO2会热生长。氧气来自氧气或水蒸气。环境温度要求为900 ~ 1200℃。发生的化学反应是

Si + O2 → SiO2

Si +2H2O —> SiO2 + 2H2

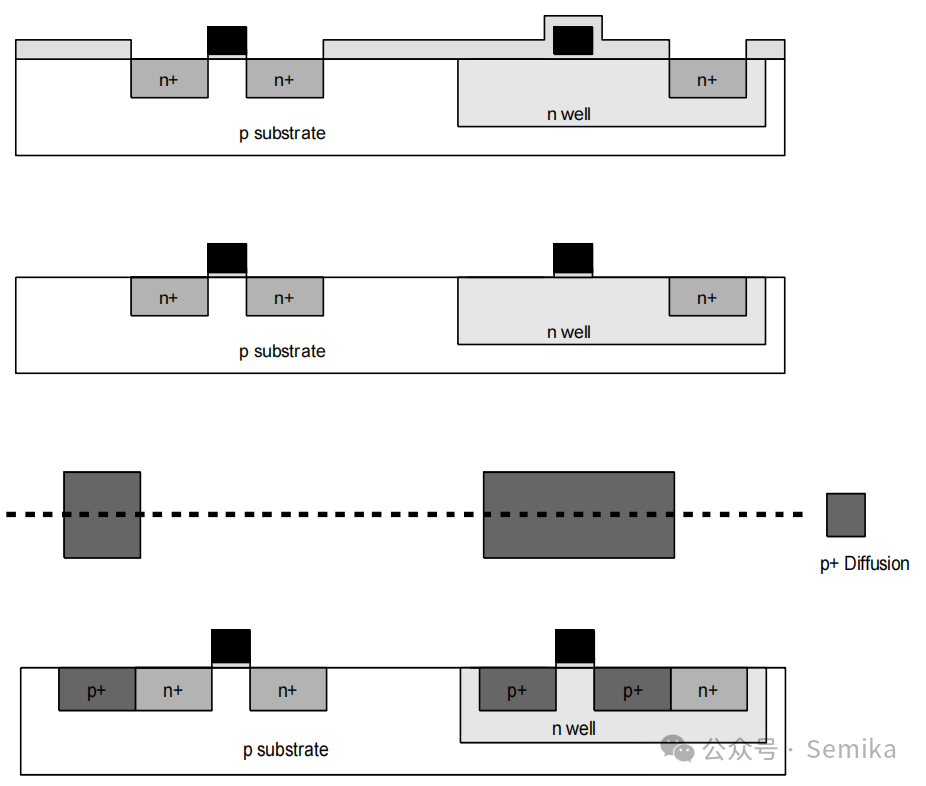

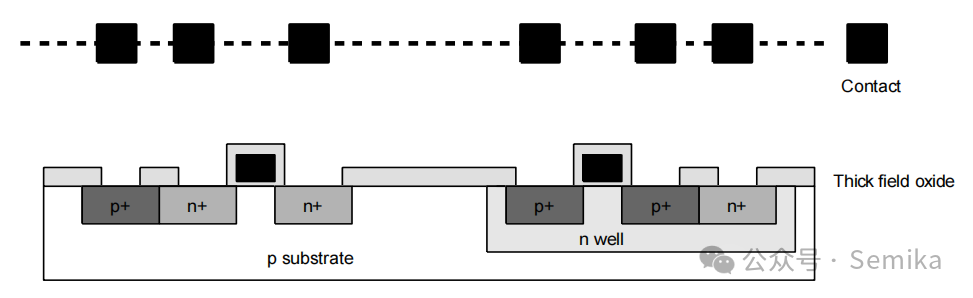

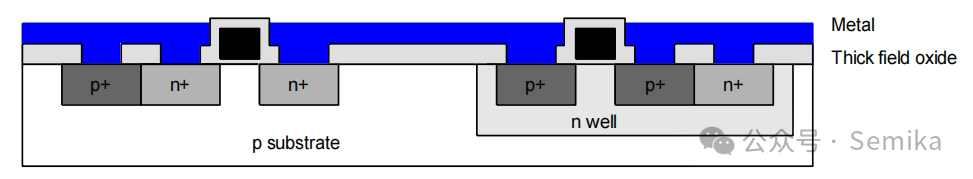

选择性氧化后的硅片表面如下图所示:

氧气和水都会通过现有的SiO2扩散,并与Si结合形成额外的SiO2。水(蒸汽)比氧气更容易扩散,因此蒸汽的生长速度要快得多。

氧化物用于提供绝缘和钝化层,形成晶体管栅极。干氧用于形成栅极和薄氧化层。蒸汽被用来形成厚厚的氧化层。绝缘氧化层通常在1500nm左右,栅极层通常在200nm到500nm间。

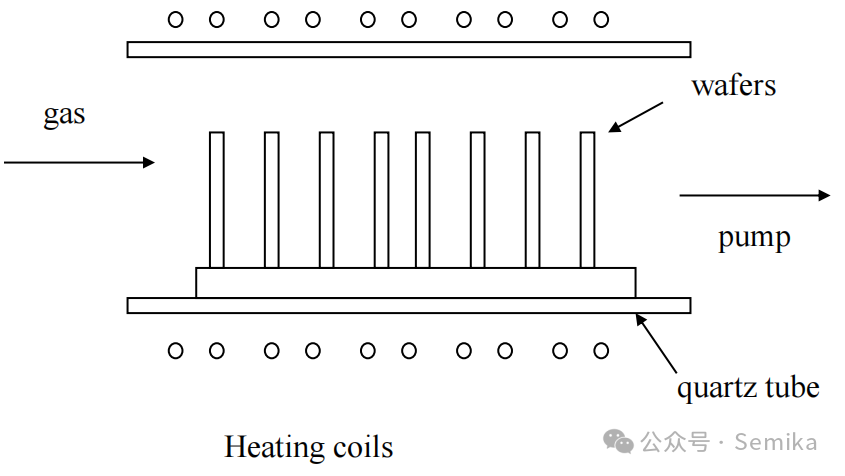

(2)化学气相沉积 Chemical Vapor Deposition

化学气相沉积(CVD)通过热分解和/或气体化合物的反应在衬底表面形成薄膜。

CVD反应器有三种基本类型:

◈ 大气化学气相沉积

◈ 低压CVD (LPCVD)

◈ 等离子增强CVD (PECVD)

低压CVD工艺示意图如下图所示。

CVD的主要有下面几种反应过程

i). 多晶硅 Polysilicon

SiH4 —> Si + 2H2 (600℃)

沉积速度 100 - 200 nm /min

可添加磷(磷化氢)、硼(二硼烷)或砷气体。多晶硅也可以在沉积后用扩散气体掺杂。

ii). 二氧化硅 Dioxide

SiH4 + O2→SiO2 + 2H2 (300 - 500℃)

SiO2用作绝缘体或钝化层。通常添加磷是为了获得更好的电子流动性能。

iii). 氮化硅 Siicon Nitride

3SiH4 + 4NH3 —> Si3N4 + 12H2

(硅烷) (氨) (氮化物)

(3)溅射

目标被高能离子如Ar+轰击,目标中的原子将被移动并输送到基材上。

金属如铝、钛可以用作靶材。

(4)蒸镀

Al或Au(金)被加热到蒸发点,蒸汽将凝结并形成覆盖晶圆片表面的薄膜。

下面用一个案例,来详细说明一下光刻、蚀刻,到离子沉积的过程中,硅片上的电路是如何一步步成型的:

半导体制造工艺 - 封装测试 (Post-processing)

(1)晶圆测试 Probe Test

在最终线路制备完成后,使用自动化探针测试方法测试晶圆上测试器件,剔除不良品。

(2) 晶圆切割 Wafer Dicing

探针测试后,晶圆片被切成单个的芯片。

(3) 接线、封装

◈ 单个芯片连接到引线框架,铝或金引线通过热压缩或超声波焊接连接。

◈ 通过将设备密封到陶瓷或塑料包装中来完成包装。

◈ 多数芯片还需要经过最后的功能测试,才会送到下游用户手上。

审核编辑:黄飞

-

WD4000系列晶圆几何量测系统:全面支持半导体制造工艺量测,保障晶圆制造工艺质量2024-06-01 1932

-

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺2024-12-30 3377

-

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测2025-04-15 1793

-

《半导体制造工艺》学习笔记2012-08-20 68005

-

半导体制造2012-07-11 5185

-

单片机晶圆制造工艺及设备详解2018-10-15 7167

-

晶圆制造工艺的流程是什么样的?2019-09-17 12312

-

半导体制造的难点汇总2020-09-02 4935

-

《炬丰科技-半导体工艺》IC制造工艺2021-07-08 4747

-

什么是半导体晶圆?2021-07-23 4281

-

浅谈晶圆制造工艺过程2018-04-16 15367

-

两种标准的半导体制造工艺介绍2022-03-14 8374

-

ALD是什么?半导体制造的基本流程2023-07-11 6914

-

半导体制造过程解析2024-10-16 4440

-

半导体晶圆制造工艺流程2024-12-24 6049

全部0条评论

快来发表一下你的评论吧 !