FPGA布局布线优化技术

可编程逻辑

1396人已加入

描述

映射逻辑到 RAM

在高端FPCA中起作用的主要是基于SRAM的FPCA,这意味着逻辑功能编码进LUT,这些LUT是小的SRAM单元,分布在整个FPGA,对一般的逻辑实现有效。似乎为此的自然扩充可以在大的专用RAM 块中实现逻辑(实际像RAM一样利用),特别当利用率变低时。虽然这个可能概念上有意义,与此有关的问题是性能。

小的分布RAM单元将有十分小的延时,逻辑通过这些LUT相对于其他逻辑元件十分快速和有效地传播。另一方面,较大的RAM块将有与其有关更大的延时,进而将产生十分慢的实现。通常,依靠逻辑封装进专用RAM块是不明智的,只有在极其高密度和慢的设计中作为最后的手段可能是有用的。

寄存器排序

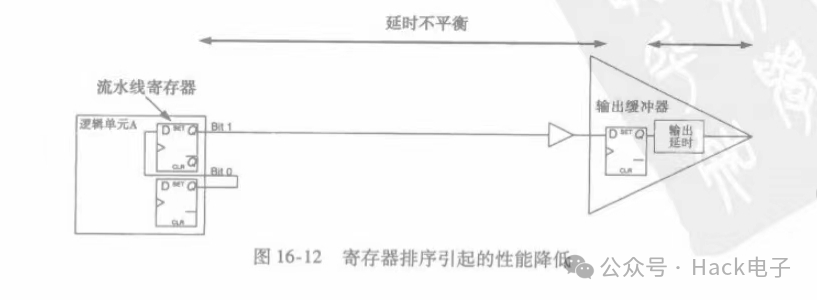

寄存器排序是布局工具把多位寄存器的相邻位分组放进单个逻辑元件所利用的方法。大多数基于单元的逻辑元件有不止一个触发器,因此,相邻位放置在一起,时序可以被优化,如图16-11 所示

用寄存器排序引起的问题是它可能阻止为布线平衡已加流水线的一组寄存器分组在一起,这将阻止附加的寄存器按照原始的意图分割布线延时。当封装寄存器进VO缓冲器时,考虑延时来平衡上述利用的寄存器。

如在图16-12中可以看到的,由于已经相邻地放置到它的驱动器,流水线寄存器的优势已经消除。

当额外的寄存器已经添加来分割布线延时,不应该利用寄存器排序。

审核编辑:黄飞

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

EDA技术与FPGA设计应用2008-06-26 6640

-

高速高密度多层PCB设计和布局布线技术2012-08-12 2809

-

PCB设计技巧Tips30:布局布线技术的发展2014-11-19 4145

-

FPGA去耦电容如何布局布线2017-08-22 10348

-

FPGA-PCB优化技术降低制造成本2018-09-20 1981

-

PCB布局和布线的设计技巧2018-11-22 2851

-

PCB布局布线技术的发展2010-06-09 823

-

布局布线技术的发展2009-03-25 873

-

高速PCB的布局布线优化2011-09-27 1246

-

FPGA设计的塑封式布局和布线介绍2019-05-17 3762

-

PCB布局布线技术是怎么样发展的2020-01-21 4257

-

FPGA的布局布线2020-10-25 9304

-

fpga布局布线算法加速2023-12-20 2038

-

FPGA布局布线的可行性 FPGA布局布线失败怎么办2024-03-18 1929

-

FPGA布局布线优化方案2024-03-26 2041

全部0条评论

快来发表一下你的评论吧 !