sr锁存器不定状态怎么理解

描述

sr锁存器不定状态怎么理解

SR锁存器,结构简单,一般由两个与非门或者两个或非门组成,原理比较简单,就是具有保持和锁存电平的作用,但是也有缺陷不定态存在,很多书上指出只要输入满足SR=1,输出就是不确定状态,但事实真的如此?

1 SR锁存器原理

先根据电路粗略讲解一下SR锁存器功能,熟悉的同学可以跳过这部分。

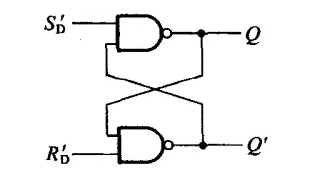

1图1 与非门构成的SR锁存器

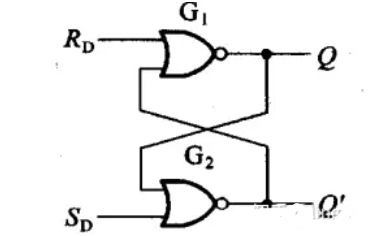

图2 或非门构成发SR锁存器

上面两图分别是使用两个与非门和两个或非门组成的SR锁存器,本文以图2两个或非门组成的SR锁存器进行功能分析。

当SD=1,RD=0时,或非门G2一端以SD作为输入,故G2输出低电平,G2和RD作为G1的输入,所以G1输出为高电平,此时SR锁存器输出Q端为高电平,Q‘为低电平。Q的次态与Q的现态无关,输出端Q均为高电平,故SD被称为置数端。

当SD=0,RD=1时,因为或非门G1的RD端输入高电平,所以G1输出端输出低电平,或非门G2输入均为低电平,则Q非为高电平,故SR锁存器Q输出为低电平,Q’输出高电平。Q的次态与Q现态无关,输出端均为低电平,RD被称为SR锁存器清零端。

当SD=0,RD=0,Q的现态为0时,则Q‘的次态为高电平,进而推出或非门G1的输出为低电平,所以Q的次态为0;当Q的现态为1时,则或非门G2的输出为0,或非门G1将RD和或非门G2输出作为输入,所以或非门G1输出高电平,即Q的次态为高电平,由此可知,Q端的次态和现态保持相同,所以当SD与RD端输入数据均无效时,SR锁存器具有保持功能。

SR锁存器不定态

分析1:SD端与RD端均有效,即SD=1且RD=1时,由于两个或非门G1,G2均有一个输入端为高电平,则Q和Q‘均为低电平,此时SR锁存器的输出是确定的,并不是所谓的不定态。

分析2:继分析1,当SD端和RD端输入均为高电平时,Q与Q’均输出低电平,此时SD由高电平变为低电平,RD保持高电平。由于或非门G2输入均为低电平,所以G2输出高电平,即Q‘为高电平。而或非门G1输入均为高电平,故G1输出为低电平,即Q为低电平,此时SR锁存器的输出也是确定的。

分析3:继分析1,当SD端和RD端输入均为高电平时,Q与Q’均输出低电平,此时RD由高电平变为低电平,SD保持高电平。则或非门G1输入均为低电平,G1输出则为高电平,即Q输出高电平。

SR锁存器不定状态的出现,主要是由于理想状态与实际工作状况之间的差异。理论上,SR锁存器的各种组合都有明确的输出状态,但在实际使用中,由于器件本身的差异以及信号噪声的影响,每个端口从“0逻辑电平电压”升高到“1逻辑电平电压”的时间并不相同。

具体来说,当SR同时从00变为11时,由于上述因素的影响,中间会引入“01”或“10”这样的中间状态,而具体引入哪种状态无法确定,这就是“状态不定”的根本原因。

因此,在实际应用中,需要避免SR同时为高电平的情况,以防止SR锁存器进入不定状态。同时,对于电路的设计和布局也需要进行细致的考虑,以减少信号噪声和器件差异对SR锁存器工作的影响。

此外,时序问题也可能导致SR锁存器出现不定状态。RS锁存器是异步的,对输入的变化没有时钟信号的依赖,输入信号的瞬时变化可能导致不确定的输出。

审核编辑:黄飞

-

d锁存器解决了sr锁存器的什么问题2024-08-28 2148

-

两种SR锁存器的约束条件2024-07-23 2821

-

SR锁存器和D锁存器的特点2023-02-27 11810

-

[6.2.1]--5.2.1SR锁存器学习电子知识 2022-11-16

-

分析一下SR锁存器的原理2022-08-20 8284

-

关于modelsim后仿真锁存器出现不定态的问题2021-09-26 5880

全部0条评论

快来发表一下你的评论吧 !