浅析SoC芯片的DVFS技术

描述

很多同学问DVFS技术怎么实现的,这里小编就和大家掰扯掰扯SoC芯片的DVFS技术吧。

1. DVFS技术介绍

DVFS(Dynamic Voltage and Frequency Scaling)即动态电压频率调节技术,是一种高效的低功耗技术,它通过动态调整工作电压和时钟频率,以达到降低功耗的目的。

在CMOS电路中,功耗主要由动态功耗和静态功耗两部分组成,而DVFS技术主要通过调整这两部分来实现功耗的降低。

2. 动态功耗与静态功耗

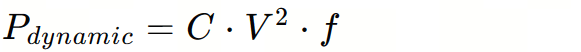

在CMOS电路中,动态功耗由以下公式给出:

其中,C 代表负载电容的容值,V 是工作电压,f 为工作频率。从公式可以看出,动态功耗与电压的平方和频率成正比。因此,通过降低电压和频率可以有效减少动态功耗。

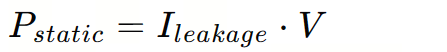

静态功耗主要由漏电流引起,可以用以下公式表示:

其中,I 是漏电流,V 是工作电压。由于静态功耗与电压成正比,降低电压也能显著减少静态功耗。

3. DVFS的实现方式

1)电压

为了实现DVFS,芯片的电源模块需要能够提供多级输出电压,通常是通过多个不同输出电压的LDO(Low Dropout Regulator)和选择开关来实现。DVFS控制逻辑会输出控制向量以选择所需的电压,电源管理模块会自动完成电压源的切换。

2)时钟

时钟频率的控制则是通过集成在芯片内部的CGU(Clock Generator Unit)来实现,它可以为系统提供特定频率的时钟信号,对时钟源进行分频或升频。

DVFS技术的实现主要依赖于对工作电压和频率的动态调整。具体来说,可以通过以下两种方式实现:

DVS (Dynamic Voltage Scaling): 通过固定电压-频率对应点来调节电压,适用于对性能要求较为稳定的应用场景。

AVS (Adaptive Voltage Scaling): 能够在一定范围内自由调节电压数值,适用于对性能要求更为灵活的应用场景。

4. DVFS的挑战与策略

在实际应用中,DVFS技术面临着一些挑战,主要包括:

时序收敛: 由于电压和频率的变化,需要在多个工作模式和条件下进行时序收敛,增加了设计的复杂度。

工作负载预测: 为了有效降低功耗,需要准确预测未来的工作负载,选择合适的供电电压和时钟频率。

针对这些挑战,可以采取以下策略:

负载模型: 在一个时间窗口内统计模块工作的时间长度,并设定不同阈值,以触发DVFS转换。就是工作负载的粗略模型可以通过在一个时间窗口内统计模块工作的时间长度来建立,并设定不同的阈值。高阈值对应高电压高频率,低阈值对应低电压低频率。每当统计值穿过阈值边界时,就会触发DVFS的转换。

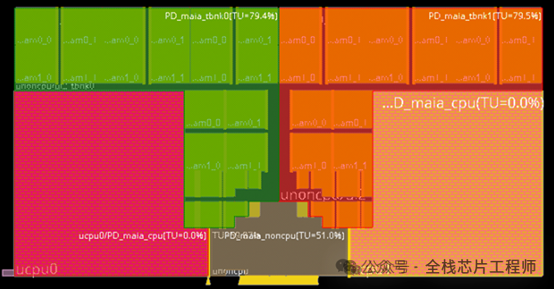

在实际的系统中,每个CPU或DSP可能有自己的独立DVFS调节系统,因此可以根据本模块的特点制定出更精确的负载模型,以取得更优的功耗表现。

调节顺序: 安全的调节机制是,提升功率时先提升电压再提升频率,降低功率时先降低频率再降低电压。

在当前的芯片实现工艺下,更高的频率通常需要更高的供电电压。这是因为更高的频率意味着动态功率消耗的增加,而更高的供电电压可以提供更大的电源功率以满足需求。因此,再次强调,安全的调节机制是:

当需要提升功率时,应先提升供电电压,然后提升时钟频率。

当需要降低功率时,应先降低时钟频率,再降低供电电压。

调节算法可以是软件实现,也可以是硬件实现,具体取决于资源消耗情况和DVFS响应时间的要求。

5. 总结

DVFS技术是数字后端设计中重要的低功耗技术之一。通过动态调整工作电压和频率,可以有效降低芯片的功耗,延长设备的使用寿命,并减少能源消耗。然而,DVFS技术的实施需要克服时序收敛的复杂性和工作负载预测的准确性等挑战。通过合理的策略和精确的控制,DVFS技术能够在保证性能的同时,实现功耗的优化。

审核编辑:黄飞

-

技术科普 | 芯片设计中的LEF文件浅析2024-11-13 1274

-

最新SOC芯片技术发展2024-10-31 2856

-

linux cpu dvfs介绍2023-03-07 3060

-

语音接口技术浅析2022-11-01 698

-

soc芯片的相关资料推荐2022-01-25 3935

-

怎样用SoC技术去设计系统芯片?2021-06-21 2114

-

请问是否有其他文档详细的描述Omap-l132芯片的DVFS使用方法?2019-08-23 1542

-

关于DVFS与AVS2018-06-21 4396

-

DVFS对程序性能影响模型2017-12-30 970

-

简单介绍SoC与SiP中芯片解密的应用2017-06-28 3088

-

SoC系统级芯片2016-05-24 7139

-

东芝开发出SoC省电技术,工作中也能深度休眠2014-04-29 2234

-

浅析语音芯片与语音合成芯片的异同2010-04-21 1494

-

SoC芯片验证技术的研究2009-08-31 808

全部0条评论

快来发表一下你的评论吧 !