下一代晶体管王牌:何种技术领跑22nm时代?

测试/封装

描述

在22nm,或许是16nm节点,我们将需要全新的晶体管。而在这其中,争论的焦点在于究竟该采用哪一种技术。这场比赛将关乎到晶体管的重新定义。在22/20nm逻辑制程的开发中,业界都争先恐后地推出各种新的晶体管技术。英特尔三栅极(tri-gate)元件已取得重大进展。许多研究人员也正努力推动FinFET元件的研究工作。而包括ARM在内的多个主要的欧洲组织,以及美国的Globalfoundries则专注于研发完全耗尽型SOI (fully-depleted SOI, FDSOI)技术。不过,最近新创业者SuVolta和富士通也提出了另外一种崭新的选择。

晶体管设计会对所有下游的设计工作带来深远影响──从制程设计到物理设计都包括在内,其涵盖领域甚至包含了逻辑设计师在功率和时序收敛方面的权衡。

问题在哪里?

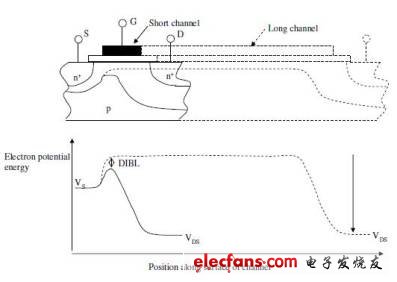

为何制程工程师们痛下决心革新晶体管设计?最简单的回答是短沟道效应。不断追逐摩尔定律(Moore‘s Law)的结果是MOSFET沟道长度不断缩减。这种收缩提高了晶体管密度,以及其他的固定因素和开关速度等。但问题是,缩短这些沟道却也带来了诸多严重问题。针对这些问题,我们可以简单地归纳为:当漏极愈接近源极,栅极便愈来愈难以夹断(pinch off)沟道电流(图1)。这将导致亚阈值漏电流。

图1:沟道上的栅极控制可消除短沟道效应

自90nm节点以来,这场对抗漏电流的战役已经持续许久。向全high-k/金属栅极(HKMG)的转移,让栅极能在不让漏电流失控的情况下更好地控制沟道电流。但到了22nm节点,许多人认为,平面MOSFET将输掉这场战役。目前还没有办法在足够的性能条件下提供良好的漏电流控制。“HKMG解决了栅极漏电流,”一位专家表示。“现在,我们必须解决沟道漏电流了。”

平面晶体管:又一次?

并非所有人都同意平面MOSFET将走入历史。其中最主要的代表是台积电,该公司2月起在20nm制程中采用平面晶体管。但此举召来了许多强烈反对,包括来自Globalfoundries的警告。设计人员对短沟道平面MOSFET的所有缺点都已经很熟悉了。看来,重新调整单元库和硬IP模组还比较干脆。漏电流和阈值的变异或许会比在28nm时更糟,但设计师们现在有了更多可用工具,包括改进过的电源管理、变异容错电路,以及统计时序分析等,都可协助他们应对这些问题。而当把所有问题端上台面时,代工厂必须知道,他们的主要客户──FPGA供应商、网络IC巨擘,甚至包括ARM在内,会提出什么样的问题。

不过,仍有许多人持怀疑态度。“台积电表示会在20nm节点使用替换性金属栅极(replacement-metal-gate)平面制程,”Novellus公司副总裁Girish Dixit观察道,“但这个决定可能已经改变。HKMG可以控制漏电流,但平面晶体管仍然具有I-on/I-off特征缺陷。”若台积电的早期采用者发现自己因为平面晶体管而处于竞争劣势,他们可能会逼迫这家代工巨擘改采FinFET半节点。而这种对峙态势也可能出现在移动市场,在这个领域,ARM的无晶圆硅晶伙伴们将面临来自英特尔采用最新22nm三栅极Atom处理器的竞争。

Fin的崛起

有关下一代晶体管的争论已经持续了10年之久,但英特尔在五月宣布的22nm三栅极制程象征着新晶体管技术的一大进展。不过,英特尔的大动作或许是为了回应ARM在移动领域的快速扩张态势,而非完全着重在原先对新晶体管技术的电路设计、大幅降低讯号杂讯的讨论范畴之中。

英特尔三栅极元件是纯粹而简单的FinFET。业界专家们并不认为英特尔试图营造出显著的差异化。业界已经为新晶体管技术努力了10年之久,整个产业都致力解决短沟道效应,除了英特尔,IMEC也在开发相同的技术。“这个产业中许多人都在开发FinFET技术,”一位制程专家表示。“不同的是,他们选择了先行发布。”

事实上,包含FinFET在内的所有下一代晶体管技术,都有一个共同的概念:全耗尽型沟道。这个概念能在沟道中赋予栅极更多在电场上的控制能力,让栅极能完全耗尽沟道载流子。这当然也消除了沟道中的主要传导机制,并有效地让晶体管关闭。

FinFET解决方案的优势便在其沟道,可以选择硅表面或是绝缘氧化层,并在生成的fin上悬垂HKMG栅极堆叠。这些鳍状(fin-shaped)沟道非常薄(图2),而且可三面运作,其栅极可成功地建构一个完全阻塞沟道的耗尽区。

FinFET元件为电路设计人员提供了自130nm以来他们便梦寐以求的V-I曲线。但也同时带来一些问题。其中之一种是便是如何构建这种元件。“要制造这些Fin结构,并在后续的处理过程中维持它们是非常困难的任务,”应用材料(Applied Materials)公司硅晶系统部门副总裁兼技术长Klaus Schuegraf说。“你必须对高耸结构的边缘进行蚀刻,对复杂3D表面进行均匀的掺杂,并在栅极堆叠中放置所有不同的薄膜,让他们能完全符合这些fin的表面。这些需求都为材料和设备带来了许多变化。掩膜层的数量或许没有太多改变,但制程步骤必然会增加许多。”

图2:Fin结构非常复杂和微妙

Fin以及其他选择

这也可能为芯片设计带来一些问题。Fin的宽度将是最小的制程尺寸。为了形成这些fin,双重图案(double-patterning)光刻技术或许会成为必要方法之一。但双重图案将会施加“非常严格的设计规则,”Schuegraf说。英特尔元件研究总监Mike Mayberry则表示:“大多数的设计规则是光刻为主。一旦你能在22nm进行表征,一部份规则是具体针对三栅极结构的。”

FinFET也将改变电路设计。其中最明显的一点,是你无法改变fin的宽度或高度以增加驱动电流。“每个fin都是一个驱动电流的量级,”Mayberry说。fin的高度取决于抛光步骤,因此它是不变的。但fin的宽度则相当不灵活。

Dixit表示,这不仅是由于光刻技术的限制,主要是因为一旦你将fin拉大,阈值电压便会开始滚降。若想扩大fin以获得更多的驱动电流,你很可能一不小心就改变阈值电压。顺道一提,这也意味着在最小几何图形上的任何线宽变异,就像是任何在fin形成期间的多晶硅深度变化,都可能在晶体管级转化为阈值变化。

为了获得更大电流,你得将更多fin平行放置。当然,只能藉由固定增量来改变驱动电流将对电路设计者带来新的局限,特别是在客制化模拟设计领域。但英特尔并不担心这一点。“我们已经建构了广泛用于开关和放大器应用的三栅极电路蓝本,我们相信,需要修改的电路设计不会太多,”Mayberry说。但其他人就没那么乐观了。“针对更大电流,你必须平行放置这些fin,”IMEC业务开发执行副总裁Ludo Deferm说。“但这需要晶体管之间的互连,而且,在高频应用中,互连阻抗将成为影响电路性能的因素。”

另一种完全耗尽方法

完全耗尽型SOI(FDSOI)的支持者认为,他们完全可以提供finFET的V-I特征。或许,更关键的重点在于阈值电压控制。由于FDSOI的沟道是未掺杂的,因此不会有因沟道掺杂而引阈值变异的问题──这是在平面和fin元件中因掺杂原子进入沟道所引发的主要问题。此外,在制程中提供多个阈值电压也是一大问题。平面和fet会因为掺杂程度变化而改变阈值电压。不过,Leti实验室主管Olivier Faynot指出,FDSOI可透过超薄埋入氧化层对沟道底部施加偏置电压,来动态地控制阈值电压。

但FDSOI仍然面临挑战。首先,FDSOI晶圆比传统晶圆更加昂贵。不过,稍早前晶圆供应商Soitec引用分析公司IC Knowledge的报告,指出由于可在FDSOI晶圆上大幅简化提供多阈值电压的处理程序,因此在22/20nm节点时,FDSOI的晶圆成本不会比平面或FinFET制程来得高。

其次是风险性。Soitec公司是唯一的FDSOI晶圆供货来源,要建构这种晶圆,需要该公司的氧化沉积、晶圆切割和原子级精密度的抛光步骤。第三是这个业界的惯性。许多资深的决策者并不会考虑SOI。不过,这个产业仍有许多公司不断推动该技术的发展。包括透过Globalfoundries持续与该技术接轨的AMD、IBM以及ST等,都致力于在22nm节点实现FDSOI技术。事实上,Globalfoundries过去并未积极对其客户推动其SOI技术,但很可能将FDSOI作为对抗来自英特尔和台积电的王牌。

不过,该领域最近也加入新的角逐者。新创业者SuVolta最近公布一项技术,使用沉积制程在传统块状平面MOSFET沟道下建构埋入式接面。将这个接面反向偏置即可建构出一个沟道下的耗尽区,能有效地模仿FDSOI的埋入氧化层,薄化沟道的活动区域,直到栅极几乎耗尽。

SuVolta的技术相当有趣,但尚未广为人知。不过,该公司的技术可能会成为一些较小型晶圆厂的选择。以富士通为例,这家公司并未挹注资金在FinFET的技术竞赛中,而且也不打算为FDSOI晶圆支付额外的初始成本。

因此,目前在下一代晶体管的竞争中,可看到台积电正致力于提供20nm平面制程。不过,台积电可能很快进行调整,在推出16nm制程前针对行动应用提供FinFET选项。英特尔仍持续专注在其FinFET上。IBM和Globalfoundries以及ST可能会在22nm使用FDSOI。富士通可能持续与SuVolta共同发展其技术。而其他业者的下一步,则将取决于其客户需求。如果说28nm有带来什么启示,那就是新制程不一定都会运作得很顺畅。

-

下一代高速芯片晶体管解制造问题解决了!2025-06-20 814

-

下一代的CMOS逻辑将迈入1nm时代?2023-11-24 930

-

三星披露下一代HBM3E内存性能2023-10-23 1805

-

下一代 NXP 低 VCEsat 晶体管:分立半导体的改进技术-AN110452023-03-03 459

-

22nm芯片是什么年代的技术?2022-06-29 7744

-

何种技术领跑22nm时代?资料下载2021-04-17 832

-

3D晶体管有什么作用?2020-04-07 4677

-

功率和成本减半 Achronix交付先进22nm Speedster22i 系列FPGAs2013-03-04 4072

-

22nm 3D三栅极晶体管技术详解2012-08-15 8770

-

高清图详解英特尔最新22nm 3D晶体管2012-08-03 1609

-

高清图详解英特尔最新22nm_3D晶体管2012-08-02 2671

-

英特尔22nm 3D晶体管工艺,Achronix公布全新Speedster22i系列FPGA细节2012-04-25 1644

-

22nm后的晶体管技术领域 平面型FD-SOI元件与基于立体2010-06-23 958

-

下一代晶体管露脸2009-08-31 956

全部0条评论

快来发表一下你的评论吧 !