DDR5测试技术更新漫谈

电子说

描述

内容来源:是德科技

一、前 言

DDR SDRAM,是一一种双数据速率(DDR)同步动态随机存取存储器(SDRAM)。作为现代数字系统里最重要的核心部件之一,应用十分广泛。从消费类电子到商业工业类设备,从终端产品到数据中心,用于CPU进行数据处理运算的缓存。近20多年来,经历了从SDRAM发展到DDR RAM,又从DDR发展到目前的DDR5,每一代 DDR 技术在带宽、性能和功耗等各个方面都实现了显著的进步,极大地推动了计算性能的提升。

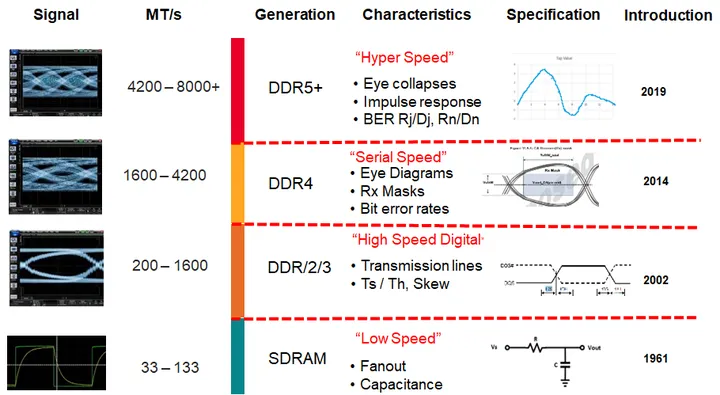

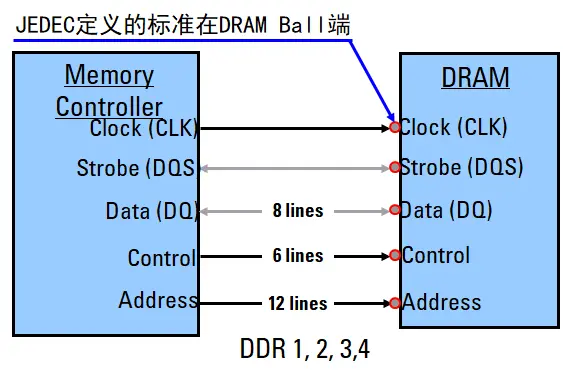

二、DDR标准发展和DDR5简介图1展示的是RAM(Random Access Memory)20多年来的发展历程和信号特点。在SRAM时代,由于较低的信号速率,我们更多关心的是信号的扇出以及走线所带来的容性负载。在DDR1/2/3时代,信号速率的不断提升,传统的使用集总参数方式来进行电路分析已越发显得不足,我们更关心的是信号的建立保持时间,以及信号线之间的延迟skew。来到DDR4时代,有限带宽的PCB、连接器等传输通道,把原始信号里的高频分量削弱或者完全去掉,使得信号在时域波形上的表现为边沿变缓、出现振铃或者过冲。我们要像分析传统串行数据那样去更加关心数据的眼图,接收端模板和误码率。随着AI、机器学习以及5G的发展,以往的DDR4技术,开始显得力不从心。如今DDR5的第5代高速I/O数据传输开始大规模走向市场化。

图1 DDR标准发展和信号特点演进

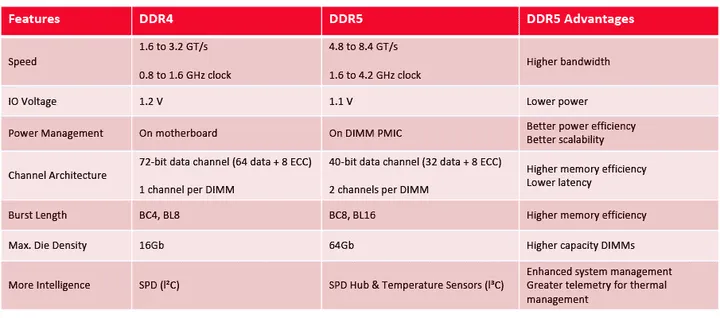

2.1 DDR5的新特性如下表所示,DDR5相比DDR4而言,带来了一系列关键的性能提升,同时也带来了新的设计挑战。

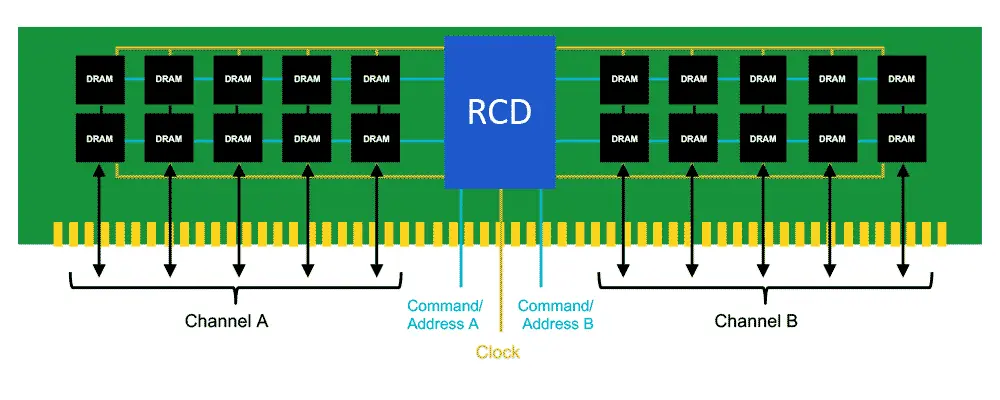

表1 DDR4和DDR5比较(源自Rambus)2.1.1 速率的提升近年来,内存与CPU性能发展之间的剪刀差越来越大,对内存带宽的需求日益迫切。DDR4在1.6GHz的时钟频率下最高可达 3.2 GT/s的传输速率,最初的 DDR5则将带宽提高了 50%,达到 4.8 GT/s传输速率。DDR5 内存的数据传输速率最终将会达到 8.4 GT/s。2.1.2 电压的降低降低工作电压(VDD),有助于抵消高速运行带来的功耗增加。在 DDR5 DRAM 中,寄存时钟驱动器 (RCD) 电压从 1.2 V 降至 1.1 V。命令/地址 (CA) 信号从 SSTL 变为 PODL,其优点是当引脚处于高电平状态时不会消耗静态功率。2.1.3 DIMM 新电源架构使用 DDR5 DIMM 时,电源管理将从主板转移到 DIMM 本身。DDR5 DIMM 将在 DIMM 上安装一个 12 V 电源管理集成电路(PMIC),使系统电源负载的颗粒度更细。PMIC 分配1.1 V VDD 电源,通过更好地在 DIMM 上控制电源,有助于改善信号完整性和噪音。2.1.4 DIMM通道架构DDR4 DIMM 具有 72 位总线,由 64 个数据位和 8 个 ECC 位组成。在 DDR5 中,每个 DIMM 都有两个通道。每个通道宽 40 位,32 个数据位和 8 个 ECC 位。虽然数据宽度相同(共 64 位),但两个较小的独立通道提高了内存访问效率。因此,使用 DDR5 不仅能提高速度,还能通过更高的效率放大更高的传输速率。

2.1.5 更长的突发长度DDR4 的突发长度为4或者8。对于 DDR5,突发长度将扩展到8和16,以增加突发有效载荷。突发长度为16(BL16),允许单个突发访问 64 字节的数据,这是典型的 CPU 高速缓存行大小。它只需使用两个独立通道中的一个通道即可实现这一功能。这极大地提高了并发性,并且通过两个通道提高了内存效率。2.1.6 更大容量的 DRAMDDR4 在单芯片封装(SDP)中的最大容量为16 Gb DRAM。而DDR5的单芯片封装最大容量可达64 Gb,组建的DIMM 容量则翻了两番,达到惊人的 256 GB。

2.2 DDR5 设计面临的挑战2.2.1 采用分离式全速率时钟,对应6400M T/s频率的时钟速率高达3.2GHz(未来会支持到8400M T/s)。

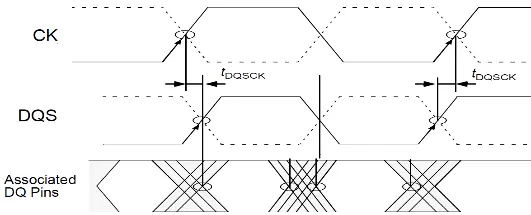

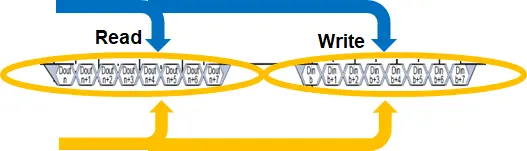

DDR5 DQS控制DQ读写时序时钟控制命令信号,选通信号控制数据。对时钟信号抖动的要求更加严格,对各种命令信号与数据和地址信号的时序要求也更高。2.2.2 双向复用的数据总线,读写数据分时复用链路。由于有限的链路通道和布板空间等资源读写操作继续采用共享总线,因此需要分时操作。从验证测试角度来看也需要分别对读和写信号进行分离以检查其是否满足规范。

DDR5读写共享总线2.2.3 突发DQS和DQ信号在更高速率的背景下在有限带宽的链路传输时带来更多ISI效应问题。在DQS读写前导位,突发的第一个bit等等均有不同的效应和表现。此外考虑到存储电路在设计上不同于串行电路存在较多的阻抗不匹配,因此反射问题或干扰带来的ISI也会更严重。

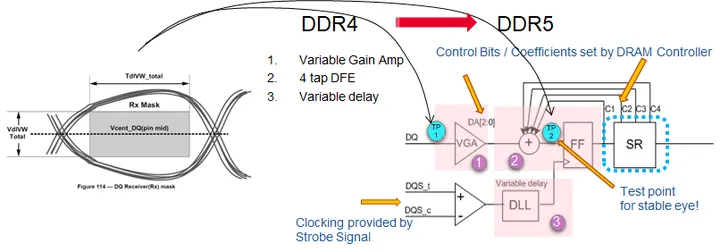

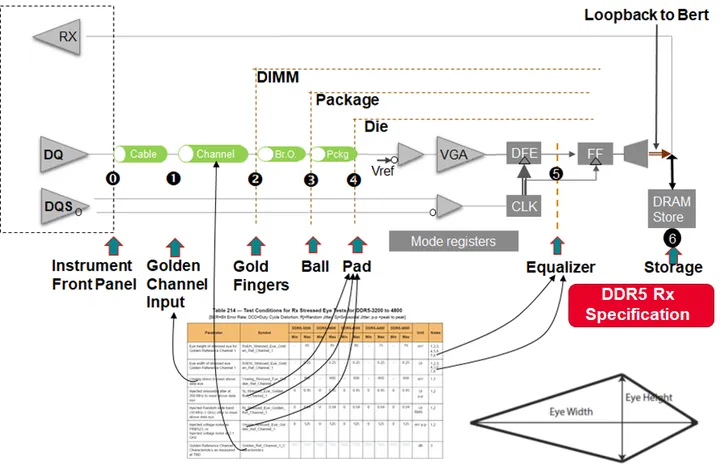

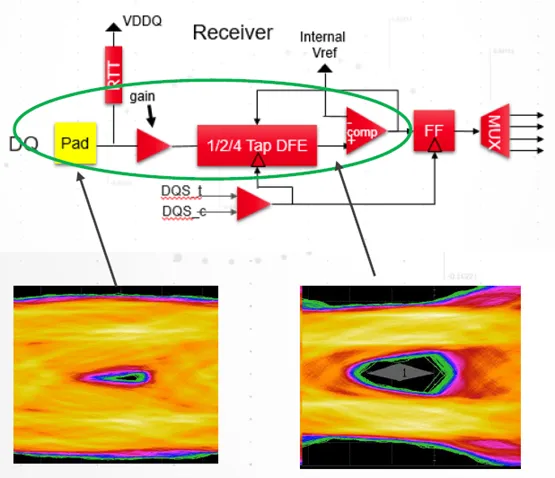

DDR5在接收端采用更多的类似高速串行总线的信号处理因此在接收侧速率大于3600MT/s时采用类似高速串行电路和标准总线中已经成熟的DFE均衡技术,可变增益放大(VGA)则通过MR寄存器配置,以补偿在更高速率传输时链路上的损耗。DDR4标准采用的CTLE作为常用的线性均衡放大,虽然简单易实现但是其放大噪声的副产品也更为常见,考虑到DDR5总线里的反射噪声比没有采用。另外考虑到并行总线的串扰和反射等各信号抖动的定义和分析也会随之变化。从测试角度来看,示波器是无法得到TP2点即均衡后的信号的,而仅能得到TP1点的信号,然后通过集成在示波器上的分析软件里的均衡算法对信号进行均衡处理以得到张开的眼图。眼图分析的参考时钟则来自基于时钟信号的DQS信号。另外眼图测试也从以往仅对DQ进行扩展到包括CMD/ADDR总线。

三、DDR5的测试新方法

3.1 发送端TX测试挑战3.1.1 读写分离

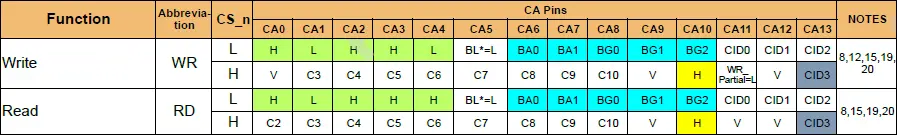

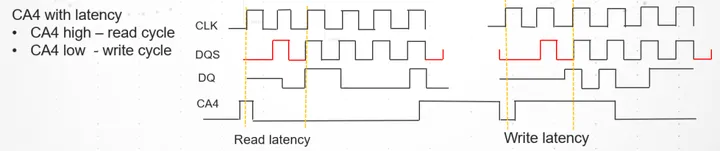

由于规范规定DDR5,不再像传统的DDR一样,读写在pin脚处有严格的相位差别。所以使用DQS-DQ 相位差和前置信号模式的传统方法可能不再适用,需要采用新方法进行读写数据分离。根据真值表可以看出,CA4在读写操作过程中有不同的逻辑电平,所以可以根据CA4的状态来结合读写延迟来进行读写分离。

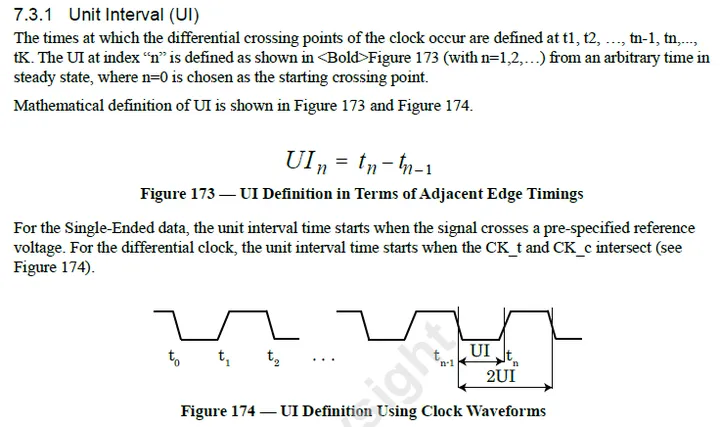

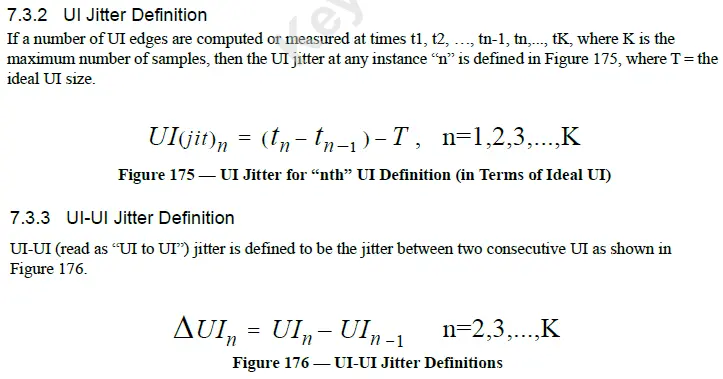

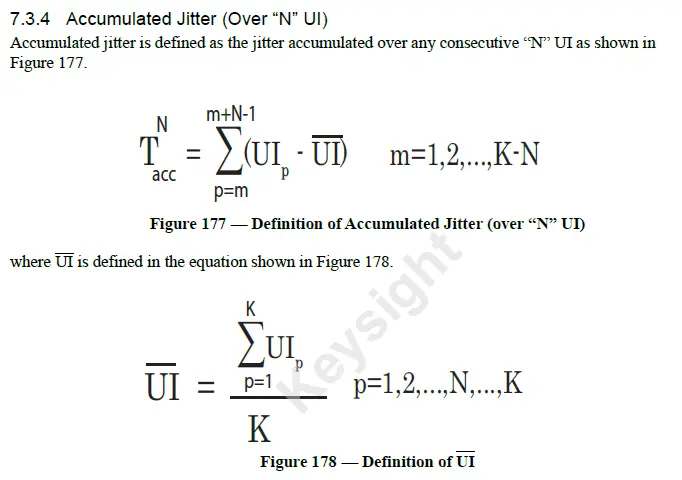

3.1.2新增的测试参数由于速率的提高,可能需要新的测试参数来鉴定关键信号。抖动成为关键信号的重要组成部分。规范定义了全新的UI抖动定义。

以及针对该UI的测量算法。

UI的测量项将覆盖CLK(input)、DQS(tx)和DQ(tx) 信号,且要求非常严格。

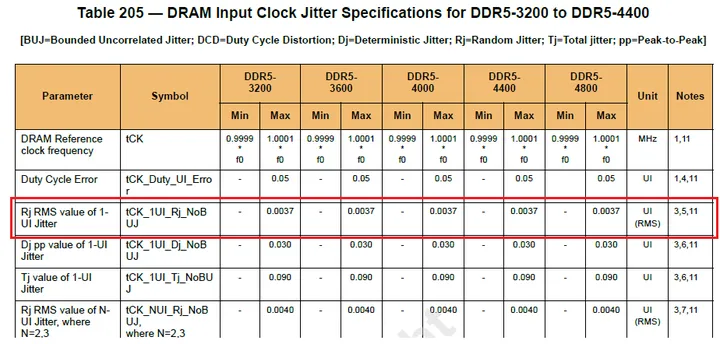

根据下表的计算,按照DDR5 4800的速率为例,要求测量出来的Rj最大值为0.0037UI,也就是769.6fs。

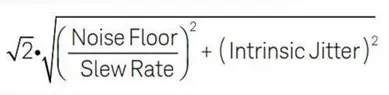

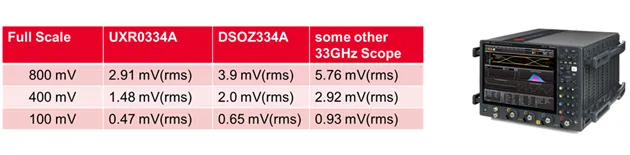

如此高要求的测量结果,也对仪表本身的性能提出了非常高的要求。仪表的抖动测量本底计算公式如下,可以看出示波器的本底噪声以及本底抖动,对抖动测量起了非常大的影响。

是德科技UXR旗舰级实时示波器,具有25fs的极低本底抖动,165μV(rms)(16G带宽下) 的本底噪声。可以提供可靠的DDR5的相关抖动测试。

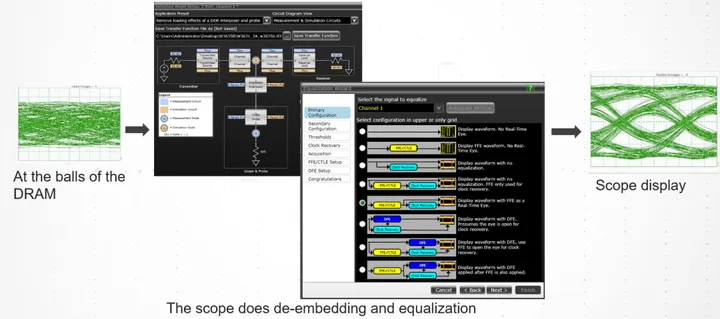

3.1.3 测试方法DDR的TX测量手法,一直是我们所关心的内容。在DDR4以前,规范规定的测试点,均在DRAM的ball处。DDR5里,除了眼图测试以外,其他测试点没有做额外更新。

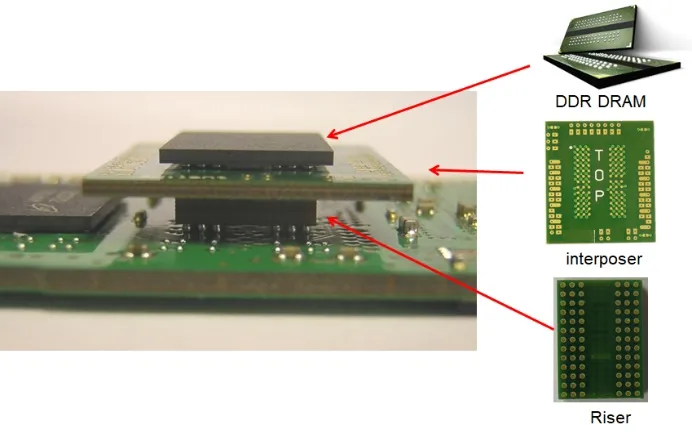

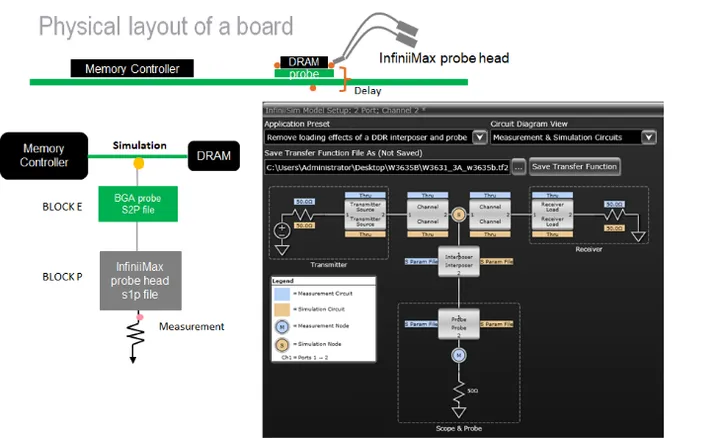

我们推荐使用interposer的方式来进行测量,如下图所示。

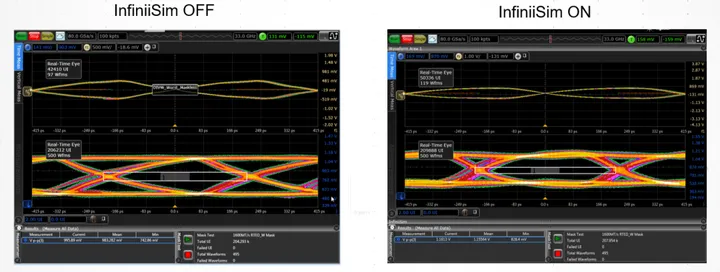

测量完成后,通过S参数的数学计算,实现从实测点到理论测试点的波形转换。

而针对于DDR5的眼图测试,如果打开了DFE功能,示波器可以在去嵌的基础上,进一步完成均衡的操作,最后得到需要的波形。

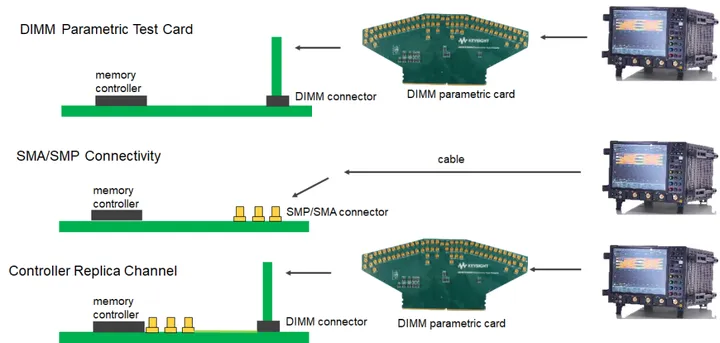

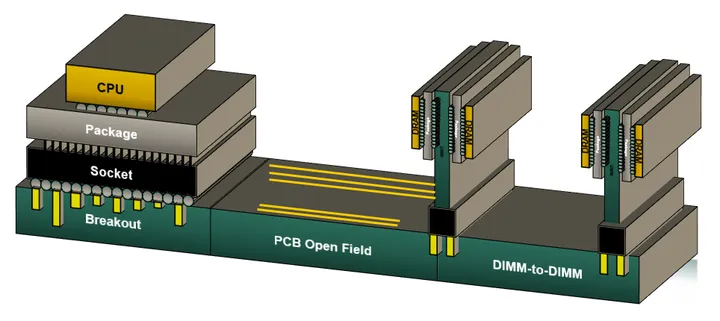

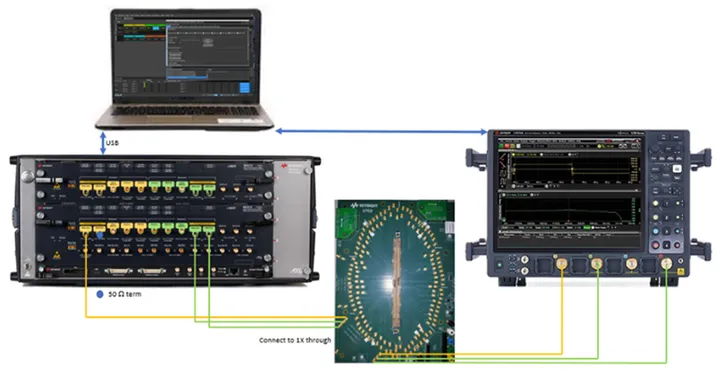

当然,是德科技已经提供自动化的测试App,方便的给用户提供可视化的一键测试方案。3.1.4 控制器测试新场景由于信号速率的不断提升,控制器、链路、芯片,纷纷加入了测试大军。下图展示了针对于控制器、PCB互联链路的TX测试场景,通过示波器,配合夹具的使用,来实现发送端的信号质量测试。

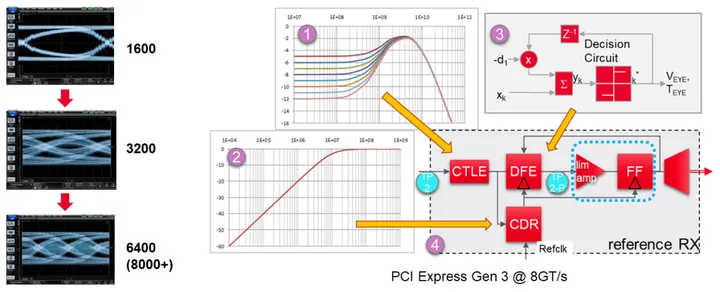

3.2 接收端RX测试挑战3.2.1 接收端新技术以往的高速串行链路设计中,我们知道随着速率的不断提升,链路的损耗,以及ISI,对高频分量的影响越来越大,所以在PCIE Gen3的时候,引入了接收端均衡的概念,用于弥补高频分量的损失。

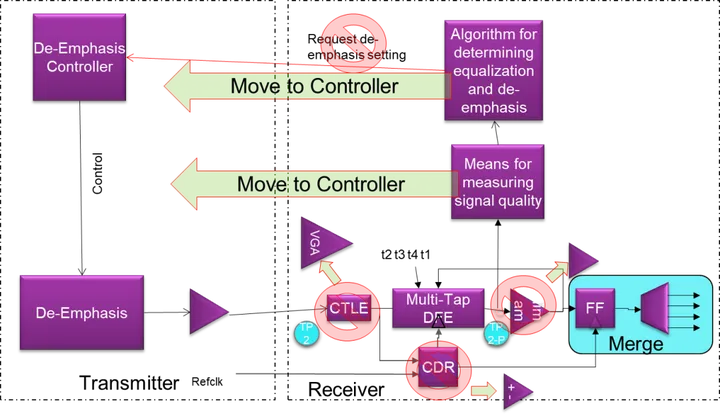

具体来看,有下面几点。①是接收端的信号会先经过CTLE(连续时间线性均衡)均衡,图上展示的是具有7个DC gain的CTLE曲线。然后信号会一分为二,一部分给到CDR②,CDR中的核心PLL的OJTF函数是一个类似左边的高通滤波器。信号的另一部分信号会给到③具有一个tap的DFE(判决反馈均衡)。我们特别注意一下图里标识的2个测试点,一个是TP2,一个是TP2`。通常TP2是使用示波器真实捕获到的信号,而TP2`则是使用标准的参考接收机模型,来去复原芯片真实看到的波形。那这种均衡技术对DDR5是否有参考借鉴的意义呢?首先看一下DDR5相对于传统serdes技术有什么特殊的地方。a)全速率时钟接收端没有PLLb)单端信号数量众多,不仅要考虑损耗带来的影响,更多的还需要考虑串扰带来的影响c)分布式多颗粒应用场景,每片颗粒独立的训练和均衡了解了DDR5和传统Serdes的几个特别之处外,参考在PCIE上使用的均衡技术,进行了部分调整后如下。

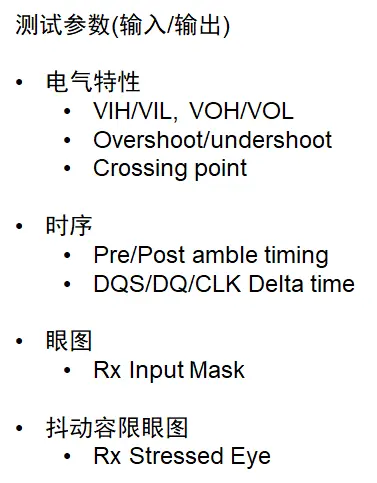

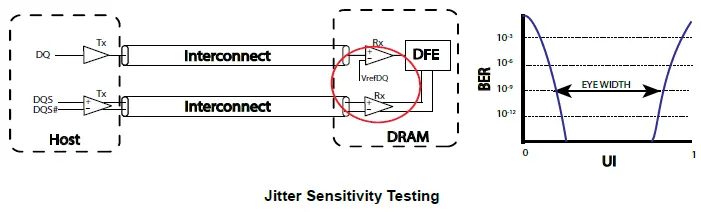

首先是CDR,由于系统里有了显示时钟,可以使用不具有频率跟踪能力的DLL模块,来代替原先复杂的CDR模块。第二个是CTLE,虽然CTLE实现简单,但是考虑到单端的DDR5总线里的反射和串扰等,对信噪比恶化严重,所以使用了VGA可变增益放大器来代替CTLE。第三个是借鉴了成熟的DFE均衡技术。最后一个,沿用了DDR以往的write leveling和read leveling机制。把原先在接收端实现的去加重功能放在了控制器端来实现。3.2.2 接收端测试的新挑战传统的Serdes接收端测试(以PCIe为例),目的是确定DUT能否在芯片封装的ball处(或者CEM规范的金手指处)可靠接收带有指定受损的信号,达到要求的误码率要求。针对DDR的单端并行总线系统,非相关抖动、电平干扰、ISI、串扰、反射,对于系统的可靠运行至关重要。DDR5的接收端测试,不仅包括了压力眼测试,也就是在给定的压力眼信号下,达到特定的误码率要求,还包括了幅度电压方面和水平抖动方面的灵敏度测试。

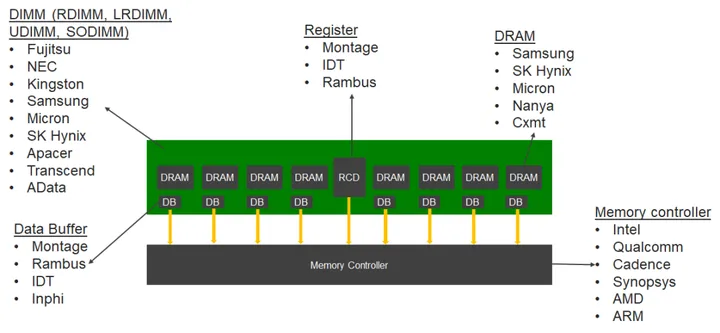

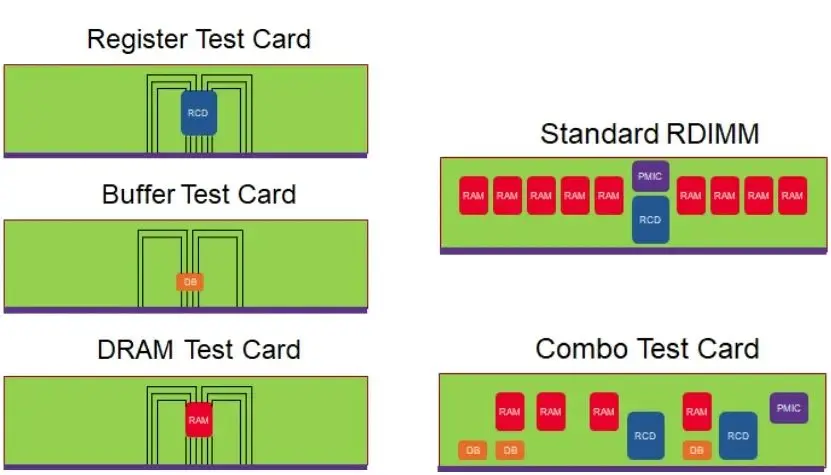

而被测DUT,可以是控制器、DRAM、缓冲器/寄存器、DIMM 等。

3.2.3 接收端测试的新方法规范定义了接收端测试里的所有测试点要求,以及波形在均衡器之后的指标要求。测试前,需要按照规范的要求进行校准。

校准之前,考虑到DDR总线的特殊性。ODT 会用于优化发送端到接收端的信号质量,由于其允许不同的阻抗设置,接收端测试过程中,建议使用 48 欧姆进行校准,以尽量减少与标准测试设备之间的不匹配。在此假设下,通过电平和抖动的 BERT 设置来调整信号的形状,实现压力信号的产生。

是德科技提供以M8000系列误码仪为基础的DDR5接收端测试方案,支持控制器、DRAM、缓冲器/寄存器、DIMM的测试。

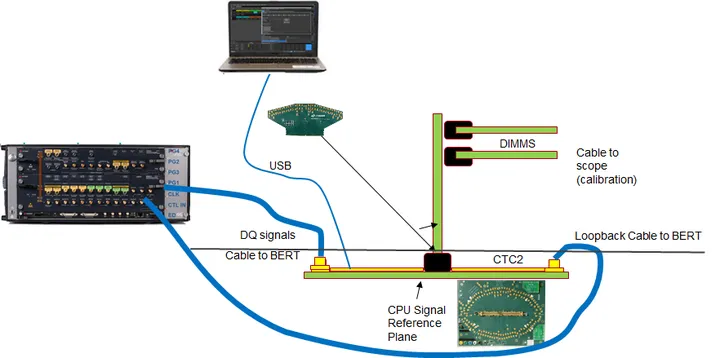

3.2.4 接收端测试的校准下图是DDR在系统产品中实际应用的拓扑结构。依次从DDR控制器,经过PCB路径,来到DIMM上的DRAM颗粒。

做校准的时候,也是参考上图的拓扑来完成整个路径的模拟。针对DIMM或者颗粒而言,信号由BERT发出,经过CTC2 Board和replicate card,最终由示波器接收,组成完整的端到端链路。

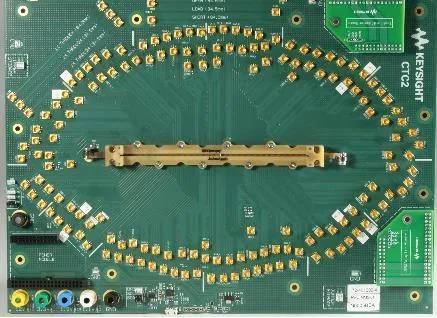

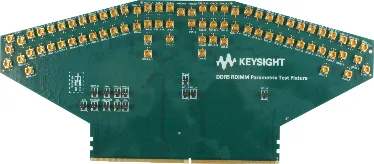

这里要特别说明的是,针对不同的产品测试,有对应的夹具来进行配合。主要的夹具有如下几种。分别是下图中的C2C test card,System Motherboard Test Fixture,Device Validation Fixture。其中,CTC2 test card提供DIMM插座,同时将DIMM上所有信号包括CA/CMD、DQS,DQ通过SMP连接器的形式引出。用于DIMM、RCD测试夹具、Data Buffer测试夹具、DRAM测试夹具等的校准和测试。

CTC2 test cardSystem Motherboard Test Fixture也同样把CA/CMD、DQS,DQ的信号通过SMP的方式引出,用于控制器的发送端测试,以及控制器的接收端测试校准和测试,同时还支持系统主板的通道特性验证。

System Motherboard Test FixtureDevice Validation Fixture包括了RCD的测试夹具,Data Buffer的测试夹具,DRAM的测试夹具,以及Combo测试夹具等。主要用于单个器件产品的校准与测试,以及多器件的校准与测试。测试时插在CTC2的test card上。

Device Validation Fixture下图展示的是基于CTC2 test card进行的校准操作。连接方式如图所示。

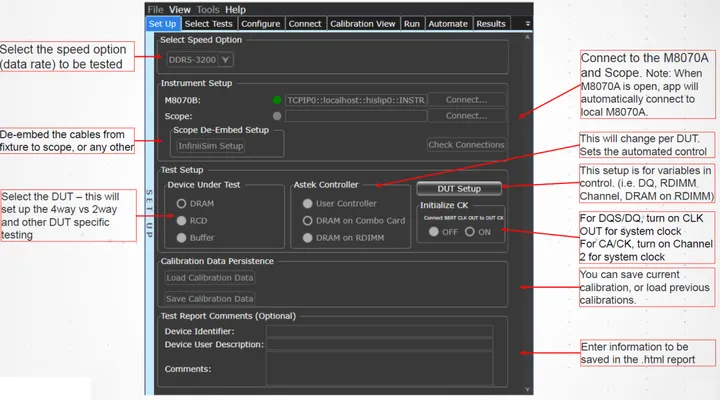

使用M80885RCA自动化软件,根据向导,完成测试环境参数的setup,并对DUT进行初始化。

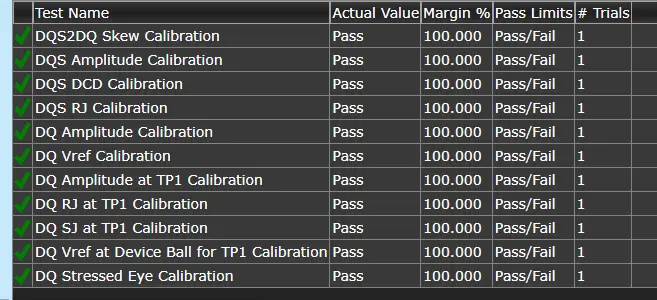

一步一步,实现DQS&DQ和CK&CA的各参数自动化校准。完成自动化校准后,可以查看每个校准项目的测试结果,如下图所示。

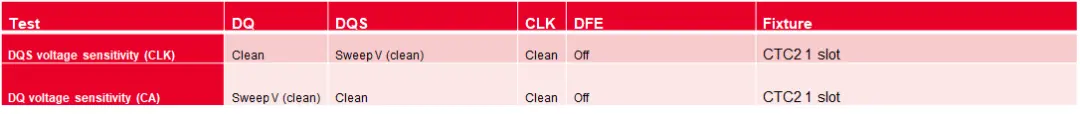

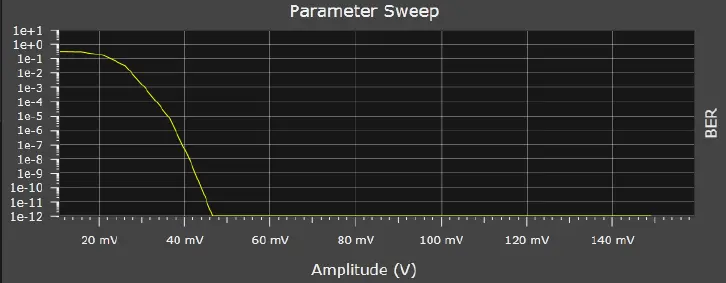

3.2.5 接收端测试接收端测试包括两大部分测试内容,Sensitivity测试和Stressed Eye测试。其中Sensitivity测试又包含Voltage Sensitivity和Jitter Sensitivity。DQS和DQ的Voltage Sensitivity测试中,测试DQS的时候保持DQ的信号不变,测试DQ的时候保持DQS的信号不变。不断调整另外一个参数的变量,遍历整个参数的范围后,统计误码率。

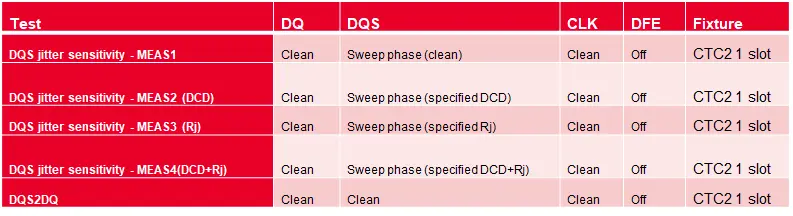

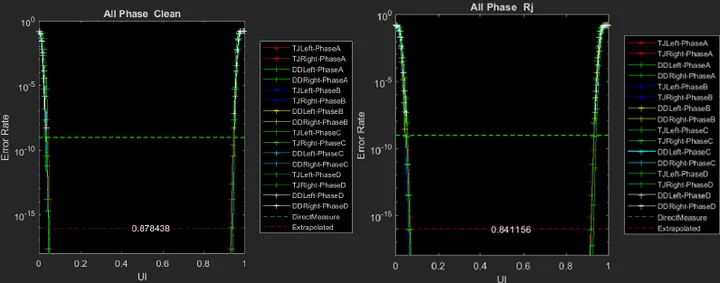

DQS的Jitter Sensitivity测试中,首先输出clean的clk和dq。在此基础上,遍历DQS和DQ的相位,计算出本底jitter的Sensitivity测试。然后依次改变DCD和Rj以及DCD和Rj的组合,遍历DQS和DQ的相位,完成各种场景下的jitter Sensitivity测试。

Stressed Eye测试中,使用校准过程中的压力信号(如下图),来进行环回误码率测试。

测试完成后,M80885一致性软件会给出上图右侧的测试结果与测试报告。

四、总 结

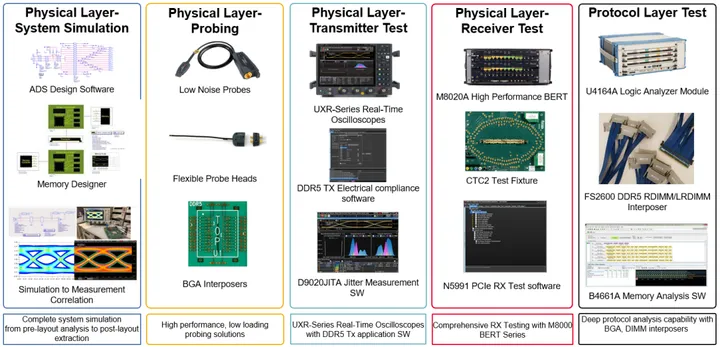

是德科技可以给大家带来完整的端到端解决方案。包括设计前期的仿真,涵盖了memory designer的建模和ADS的前后仿真。发送端测试中,我们提供业内旗舰级性能指标的UXR实时示波器和高性能的RC模型探头,有效降低测试负载。接收端测试中,我们提供all-in-box的M8000系列误码仪,支持控制器、DRAM、Data Buffer、RCD、DIMM的接收端校准与测试。协议分析仪方面,U4164A系列,支持完整的DDR、LPDDR的协议解码测试。

文章来源:是德科技

审核编辑 黄宇

-

Introspect DDR5/LPDDR5总线协议分析仪2024-08-06 4849

-

DDR5尚未真正普及的原因是什么?2021-06-18 3374

-

DDR3/4都还没玩够,DDR5已经来啦2021-08-12 5355

-

DDR5这么快,为啥还能那么稳?2023-06-28 4405

-

Cadence公司发布了关于即将发布的DDR5市场版本以及技术的进展2020-06-08 6401

-

DDR5内存将在明年实现量产2020-12-09 3375

-

专门为内存颗粒测试设计的DDR4/DDR5 Interposr测试板2022-10-10 9437

-

ddr5的主板可以用ddr4内存吗 几代CPU才能上DDR52023-08-09 38199

-

XMP DDR5 8000内存性能测试详解2023-09-15 3356

-

DDR5 SDRAM规范2023-12-25 1253

-

DDR5内存接口芯片组如何利用DDR5 for DIMM的优势?2024-03-17 5643

-

DDR5内存的工作原理详解 DDR5和DDR4的主要区别2024-11-22 9396

-

DDR5内存与DDR4内存性能差异2024-11-29 6607

-

DDR5测试技术更新漫谈2025-04-21 2739

-

DDR5 设计指南(一):DDR5 VS LPDDR52025-10-27 11447

全部0条评论

快来发表一下你的评论吧 !