浅析CMOS电路的静态功耗和动态功耗

描述

1. 简介

CMOS电路功耗主要由动态功耗和静态功耗组成,动态功耗又分为开关功耗、短路功耗两部分

2. 静态功耗

静态功耗也称为待机功耗,包含有电路中晶体管的漏电流所导致的功耗

3. 动态功耗

3.1 开关功耗

动态功耗包括:开关功耗或称为反转功耗、短路功耗或者称为内部功耗;

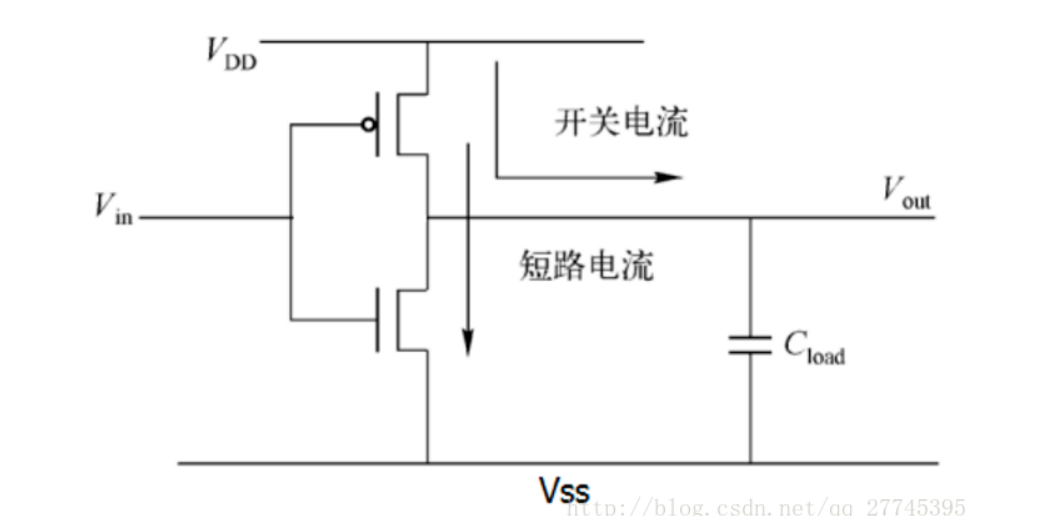

开关功耗:电路在开关过程中对输出节点的负载电容充放电所消耗的功耗。比如对于下面的CMOS非门中:

当Vin=0时,PMOS管导通,NMOS管截止;VDD对负载电容Cl进行充电;

当Vin=1时,PMOS管截止,NMOS管导通;VDD对负载电容Cl进行放电;

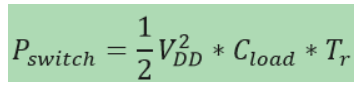

这样开关的变化,电源的充放电,形成了开关功耗,开关功耗的计算公式如下, 并且通过这个式子我们可以只要有时钟,或者信号跳变,就存在开关功耗,也就是动态功耗

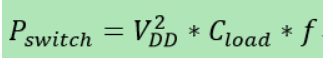

在上式中,VDD为供电电压,Cload为后级电路等效的电容负载大小,Tr为输入信号的翻转率,也有另外一种写法,f为时钟频率,一个周期信号翻转两次,所以这里没有 1/2;

它与电路的工作频率成正比,与负载电容成正比,与电压的平方成正比。

3.2 短路功耗

由于输入电压波形并不是理想的阶跃输入信号,有一定的上升时间和下降时间,在输入波形上升下降的过程中,在某个电压输入范围内,NMOS和PMOS管都导通,这时就会出现电源到地的直流导通电流,这就是开关过程中的短路功耗。

短路功耗产生的条件一样是需要信号产生跳变。

3. 静态功耗

在CMOS电路中,静态功耗主要是漏电流引起的功耗

对于常规cmos电路,在稳态时不存在直流导通电流,理想情况下静态功耗为0,但是由于泄露电流的存在,使得cmos电路的静态功耗并不为0。一般情况下,漏电流主要是指栅极泄漏电流和亚阈值电流, CMOS泄露电流主要包括:

PN结反向电流I1(PN-junction Reverse Current)

源极和漏极之间的亚阈值漏电流I2(Sub-threshold Current)

栅极漏电流,包括栅极和漏极之间的感应漏电流I3(Gate Induced Drain Leakage)

栅极和衬底之间的隧道漏电流I4(Gate Tunneling)

栅极泄漏功耗:在栅极上加信号后(即栅压),从栅到衬底之间存在电容,因此在栅衬之间就会存在有电流,由此就会存在功耗。

亚阈值电流:使栅极电压低于导通阈值,仍会产生从FET漏极到源极的泄漏电流。此电流称为亚阈值泄漏电流。要降低亚阈值电流,可以使用高阈值的器件,还可以通过衬底偏置进行增加阈值电压,这些属于低功耗设计。

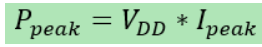

静态功耗的计算公式如下,Ipeak为泄漏电流:

4. 低功耗设计

4.1 RTL级

1.并行结构:并行结构一定程度可以减低某一区域的频率,从而可能降低功耗。

2.流水结构:“路径长度缩短为原始路径长度的1 /M。这样,一个时钟周期内充/放电电容变为C/M。如果在加入流水线之后,时钟速度不变,则在一个周期内,只需要对C/M进行充/放电,而不是原来对C进行充/放电。因此,在相同的速度要求下,可以采用较低的电源电压来驱动系统。”

3.优化编码:通过数据编码来降低开关活动,例如用格雷码取代二进制。

4.操作数隔离:“操作数隔离的原理就是:如果在某一段时间内,数据通路的输出是无用的,则将它的输入置成个固定值,这样,数据通路部分没有翻转,功耗就会降低。”

4.2 门级电路

1.门控时钟技术:芯片工作时,很大一部分功耗是由于时钟网络的翻转消耗的,控技术基本原理就是通过关闭芯片上暂时用不到的功能和它的时钟,从而实现节省电流消耗的目的,门控时钟对翻转功耗和内部功耗的抑制作用最强,是低功耗设计中的一种最有效的方法。

2.多电压供电

3.多阈值电压

根据多阈值电压单元的特点,为了满足时序的要求,关键路径中使用低阈值电压的单元(low Vt cells),以减少单元门的延迟,改善路径的时序。而为了减少静态功耗,在非关键路径中使用高阈值电压的单元(high Vt cells),以降低静态功耗。因此,使用多阈值电压的工艺库,我们可以设计出低静态功耗和高性能的设计。

4.动态电压调节

5.动态频率调节

审核编辑:刘清

-

低功耗设计之Power Switch Cell2024-01-16 7639

-

动态电路和静态电路的区别2023-09-17 6681

-

cmos门电路静态功耗怎么算,cmos静态功耗影响因素2023-07-21 5157

-

低功耗技术(一)动态功耗与静态功耗2023-06-05 5374

-

CMOS数字电路静态时动态功耗大的原因2022-10-31 6176

-

浅析CMOS集成电路的动态功耗2022-06-09 9028

-

低功耗设计相关资料推荐2021-11-11 1612

-

SRAM中的功耗来源2020-05-18 3022

-

FPGA系统设计的静态功耗和动态功耗分析与进行仿真建模2020-01-16 10103

-

基于FPGA静态和动态功耗解决方案介绍2019-05-16 9472

-

动态时钟配置下的SoC低功耗管理详解2018-02-12 3804

-

静态和动态功耗的定义2010-05-31 14400

-

深亚微米集成电路静态功耗的优化2009-09-15 600

全部0条评论

快来发表一下你的评论吧 !