Efinity软件安装教程与Efinity入门使用教程 大牛手把手教程

描述

1.软件安装教程

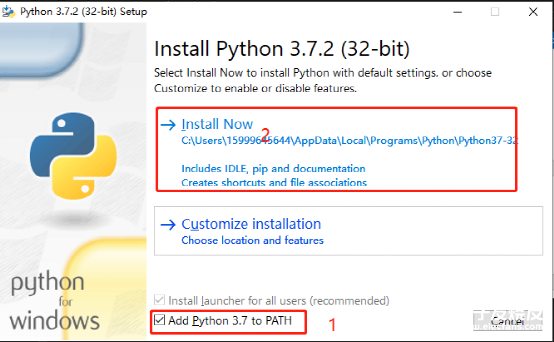

step1:安装Python,注意勾选“Add Python 3.7 to PATH” (2022版本及以后直接跳过该步骤)

注意:从2021.1就不需要单独安装python了,软件安装时会自己安装python3.8,也不需要下载。

step2:安装efinity。该步骤比较简单,一路选择Next,或者勾选同意。

stpe3:安装补丁。如果所选择的版本有补丁则安装补丁,如果没有则不必。

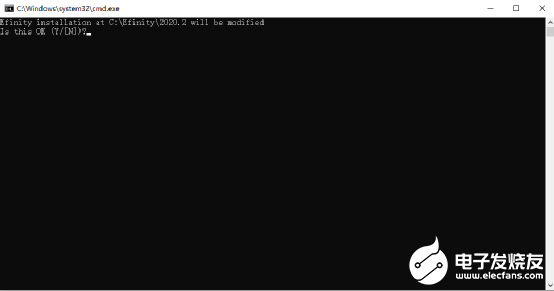

如果需要安装补丁,则打开补丁文件夹,运行里面的run.bat文件。

输入y,按任意键退出。

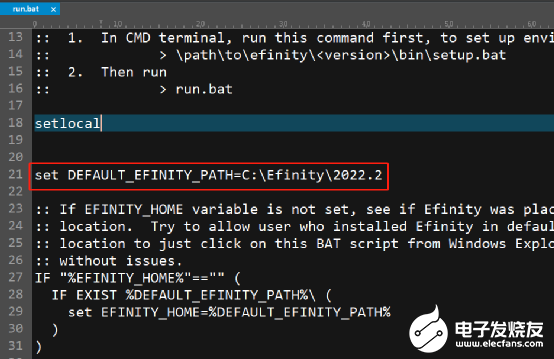

如果安装失败,可能是软件没有关闭或者软件没有安装在默认路径下。打开run.bat文件,里面的路径默认是

set DEFAULT_EFINITY_PATH=C:Efinity2022.2。

修改成自己的Efinity软件安装路径即可。

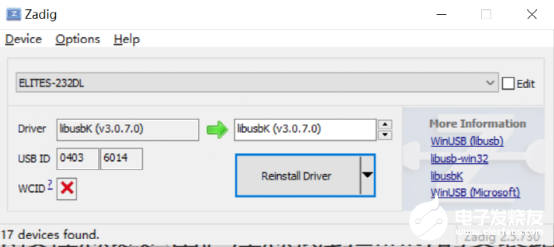

stpe4:安装下载器驱动。注意该步骤要插入下载器才可以检测到相应的下载器信息。

(1)打开zadig,

(2)选择Options中list all devices,

(3)勾掉Options中Ignore Hubs or Composite parents

(4)选择相应驱动;

(5)Driver中选择libusbk替换现有驱动;

另外也可以通过YLS_DL驱动直接安装。这种方式更简单,也是推荐的方式。请参考下载器安装。

注意:zadig的版本使用2.8或者以后的版本,旧的2.5版本会存在更换下载器的USB口需要重新安装驱动的情况。

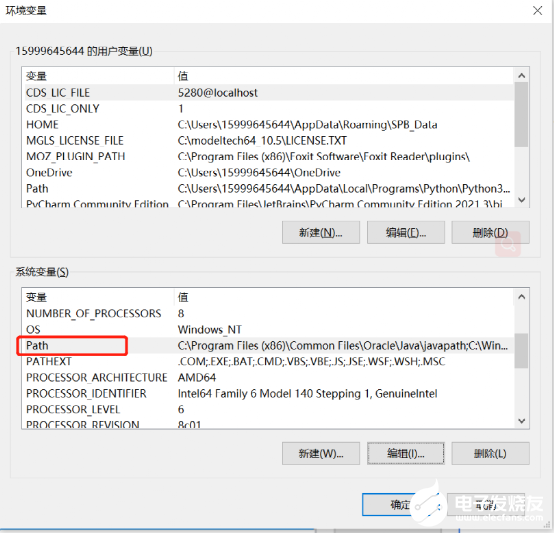

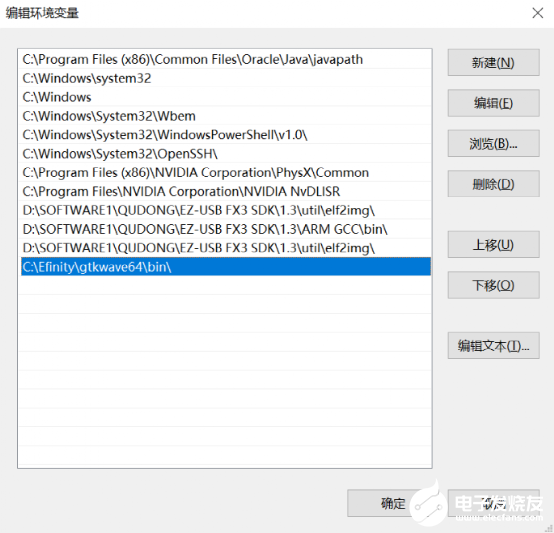

step5:安装gtkwave

gtkwave的作用是用于在线调试。把gtkwave解压到efinty安装路径下,然后添加环境变量,在变量path中添加gtkwave所在路径,如“C:Efinitygtkwave64bin”保存即可以。

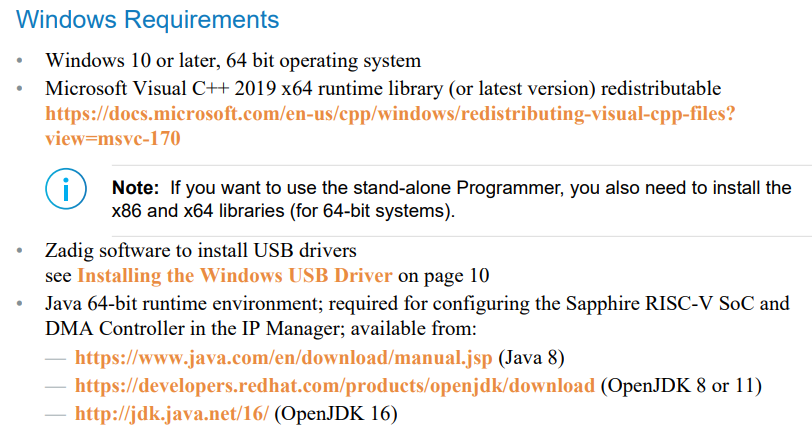

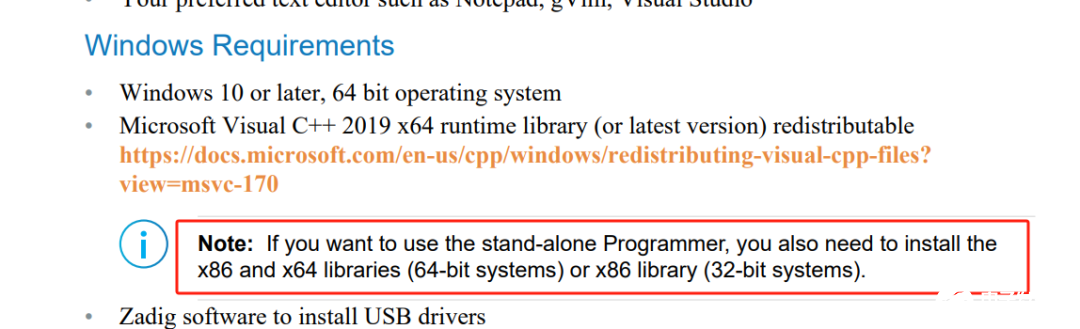

注意:在安装完成Efinity之后,有些电脑在使用软件时可能存在各种问题。请务必按照Efinity Software InstallationUser Guide中的指导安装一些库文件。只要按照下面的要求去安装可以解决大部分问题。

=================================

2、常见问题总结

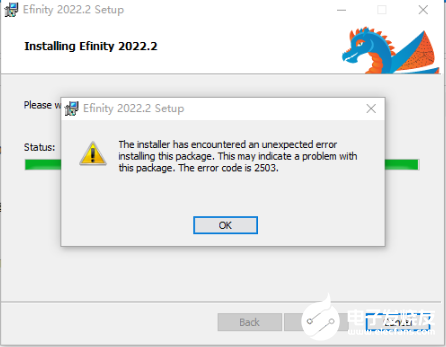

(1)The installer has encountered an unexpected error installing this package . This may indicate a problem with this package. The error code is 2503

Python安装过程报错The error code is 2503的解决方案_谷哥的小弟的博客-CSDN博客

网上有一篇 Python安装过程报错The error code is 2503的解决方案 ,原文链接如下:

原文链接:https://blog.csdn.net/lfdfhl/article/details/105639792

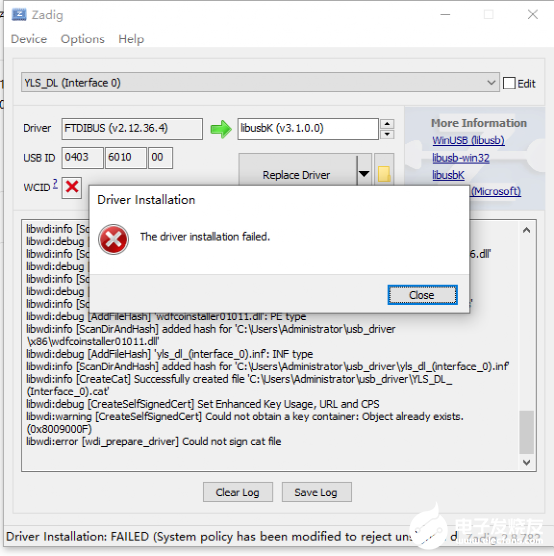

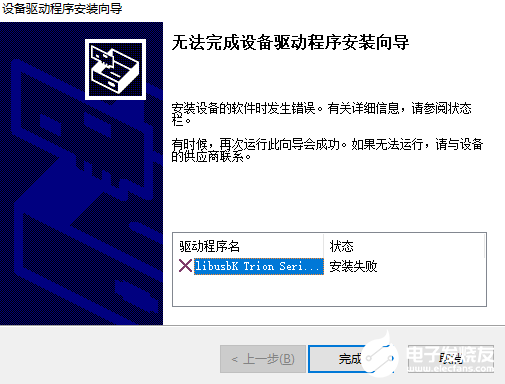

(2)zadig安装失败

Zadig提示:system policy has been modified to reject unsigned drivers

以管理员身份运行zadig

说明:可能与别的驱动有冲突。

也可能是系统问题。

(3)软件打开时指示IPC 没有连接

安装VC_redist.x64。相应的安装文件可以找FAE或者按照Efinity Software Installation User Guide中提供的链接自行下载。

(4)Efinity软件打不开

可能是安装了自己的字体。

说明(1)完整软件安装过程;

(2)补充软件安装可能存在的问题。

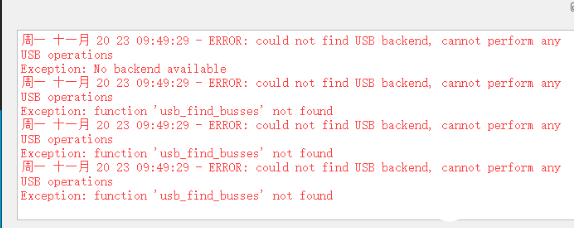

(5)Efinity单独安装programmer报错

报错如下:

Error: could not find USB backend,cannot perfom any USB operations。

最近老是碰到客户单独安装programmer会报错的现象。经过AE提示发现,在efinity-installation.pdf安装文档中也有说明:单独安装programmer时是要安装x86和x64的Microsoft Visual C++。

Efinity入门使用教程

1、 软件预设置 2、新建工程 3、添加源文件 4、添加管脚约束 5、添加GPIO 6、PLL设置 7、添加debug 8、下载 9、仿真 软件预设置。

| 选项 | 说明 |

| User editor | 一般软件自带的编辑器功能有限,而外部编辑器功能要强大很多。所以建议大家使用外部编辑器。在User editor中输入编辑器的路径。 |

| Use user editor as default editor for all files。 | 如果希望每次点击文件时是通过外部编辑器打开的,可以勾选Use user editor as default editor for all files。反之,如果希望使用自带编辑器打开则不用勾选。 |

| Top level project path | 指定新建工程目录。 |

| Enable flow data integrity check | |

| Open last project on startup | 如果勾选此选择,会打开上次关闭的工程 |

| open file using default system application | |

| Use last window layout setting | 使用上次软件关闭时的窗口布局。 |

| Auto-correct Tcl command | 在tcl命令窗口中输入命令时可以自动修改存在的错误。 |

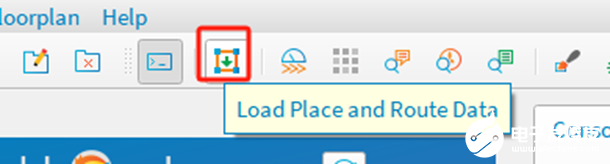

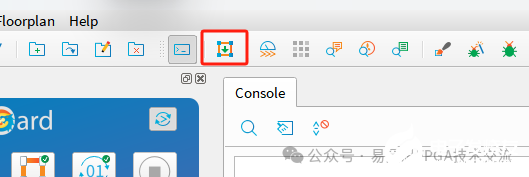

| Auto-load Place and Route data | 打开软件是自动加载布局布线的数据。建议关闭。 |

| Migrate interface design with device change | 修改器件时,interface desiger中的配置也要修改。 |

| Enable IP upgrades prompt on project load | 用新版本打开老的软件建的工程时,打开该选项会提示IP需要更新,如果不想更新IP可以关闭这个选项。 |

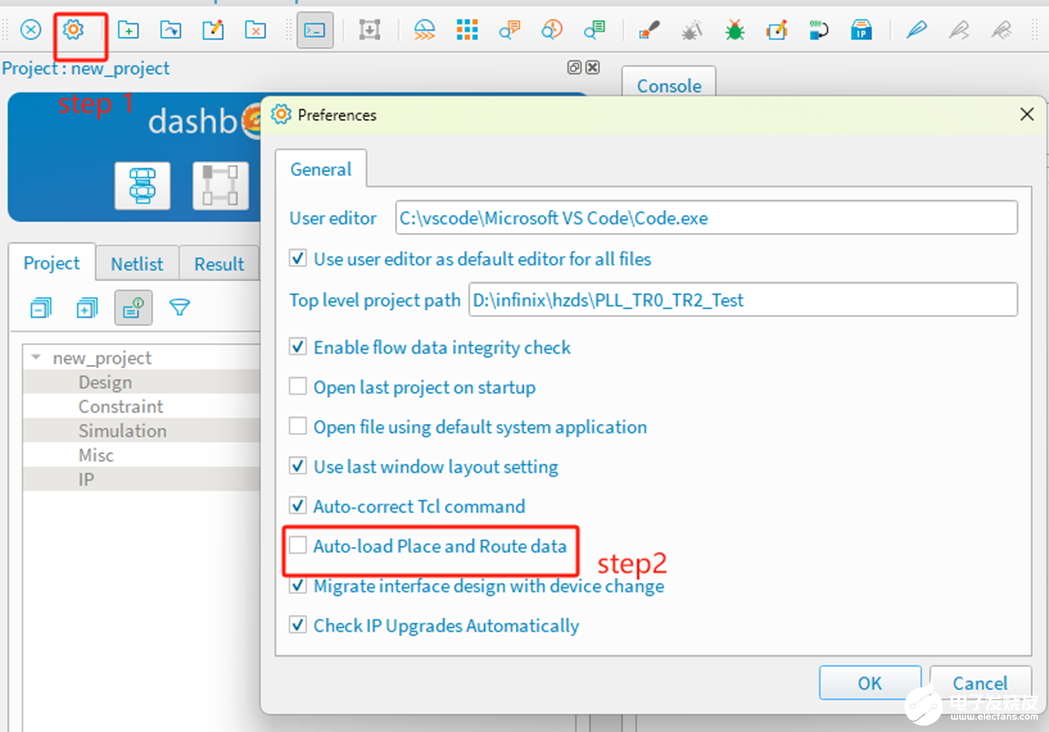

点击preference,把Auto-load Place and route data前面的对勾去掉。其目的是为了防止软件打开工程时加载时间太长。 如果需要加载数据可以点击Load Place and Route Data

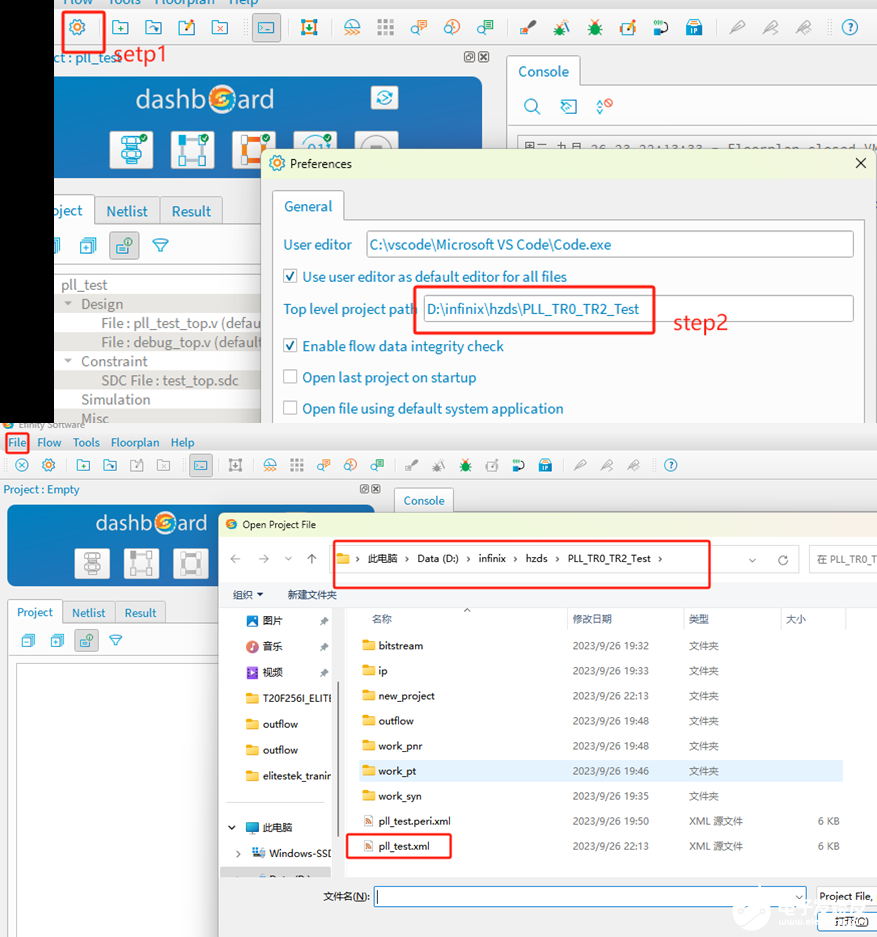

新建工程

Step1:点击设置

Step2:在Top level project path中输入路径

Step3:点击File -> Open Project,路径会指向step2中设置的路径

注意:易灵思的工程名为.xml,而不是.peri.xml,.peri.xml用于存放interface designer中的参数设置。

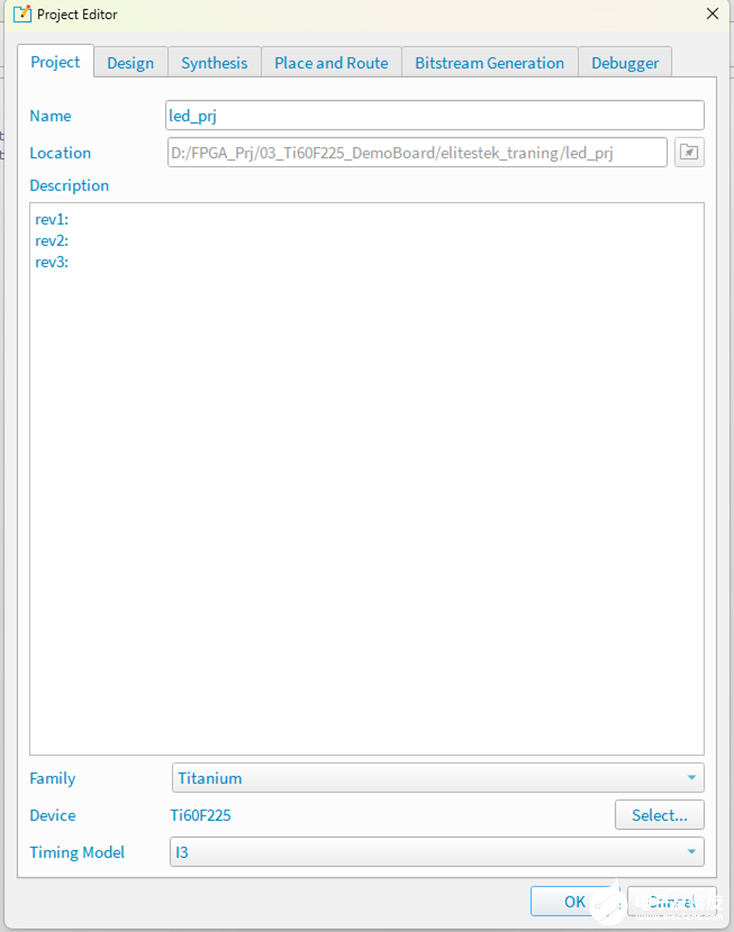

Stp1:File --> Create Project Stp2:在Project Editor中选择路径并输入工程名 Stp3:选择器件(家族)及速率等级

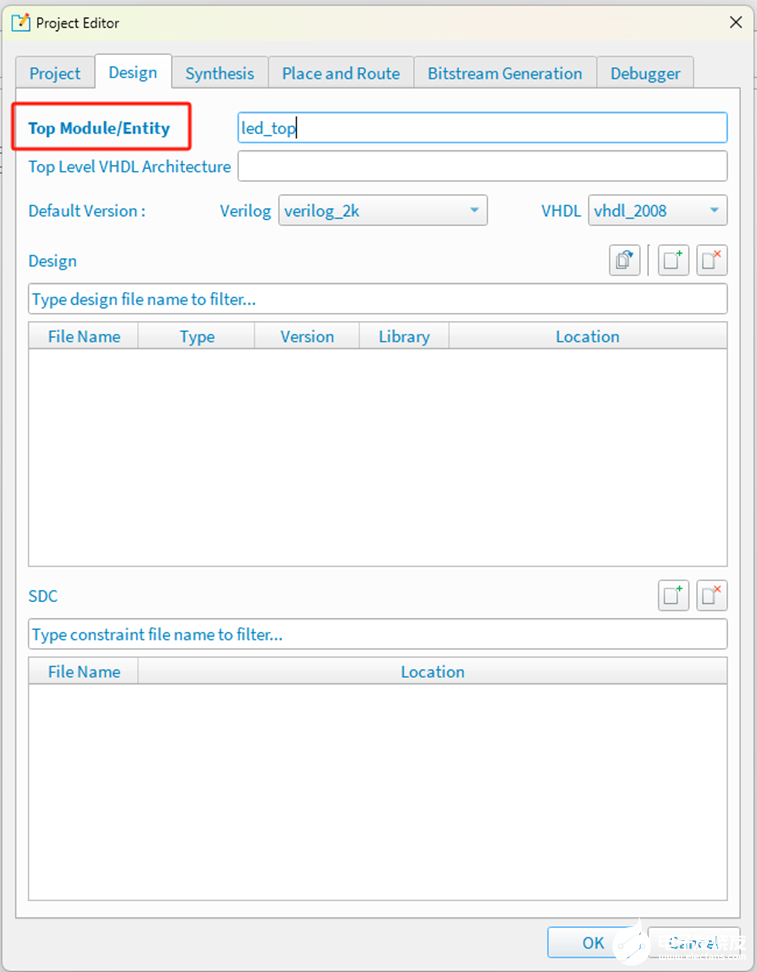

输入top module/Entity 注意:如果没有输入top module名,软件会自己选择top module,编辑结果不正确。

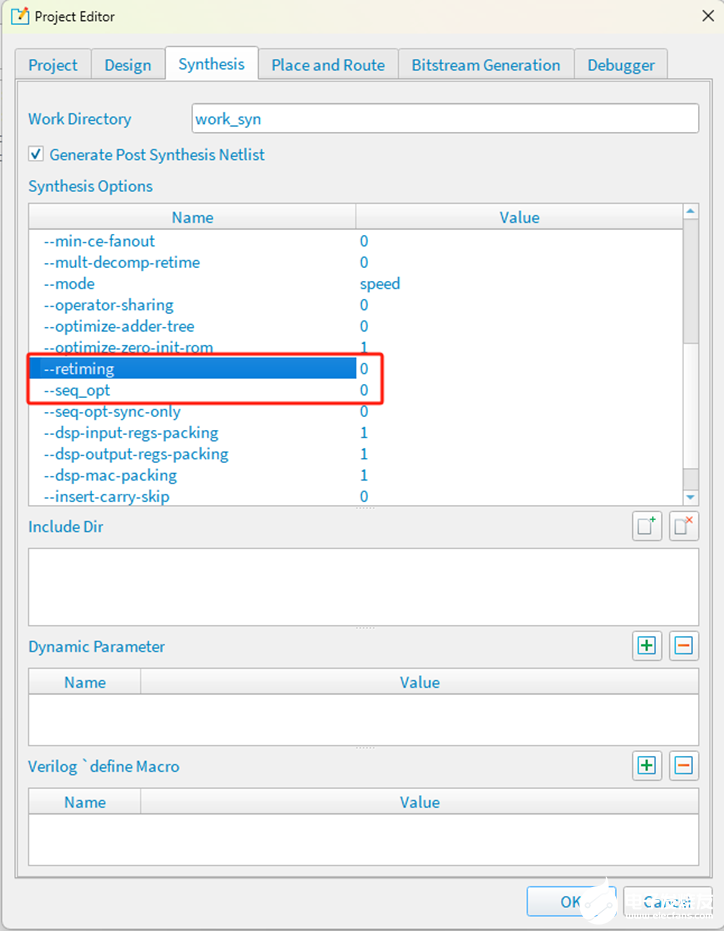

把retiming和seq_opt设置为0

点击ok,新建工程完成。

添加源文件

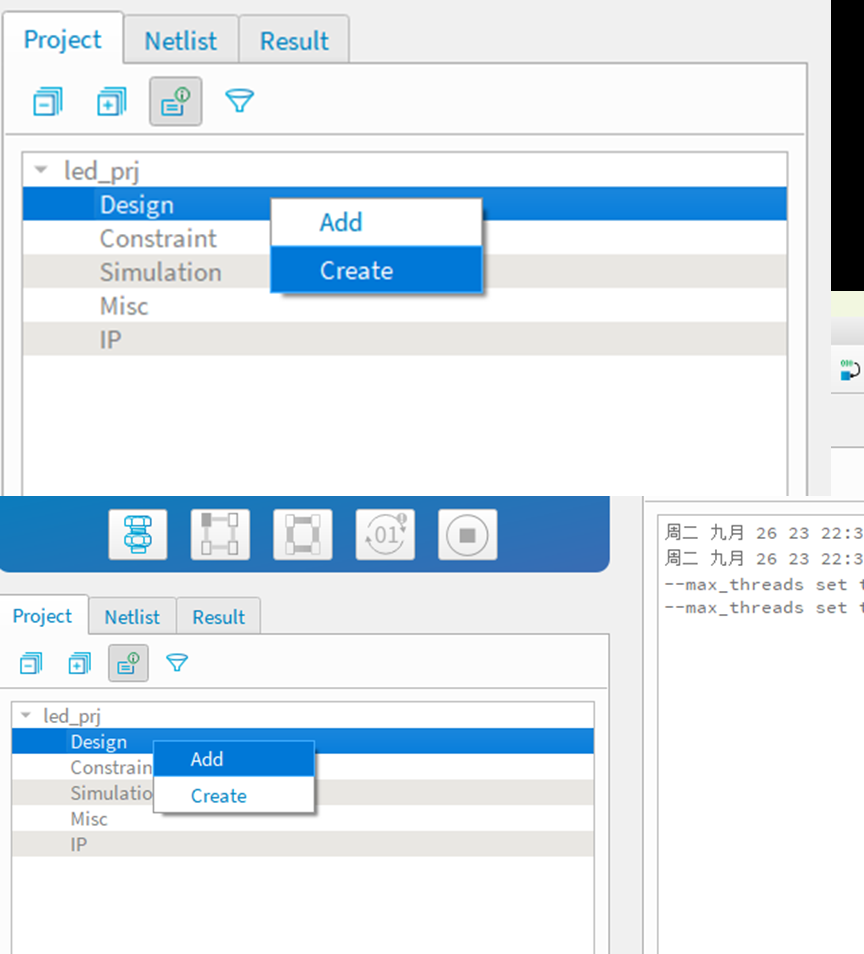

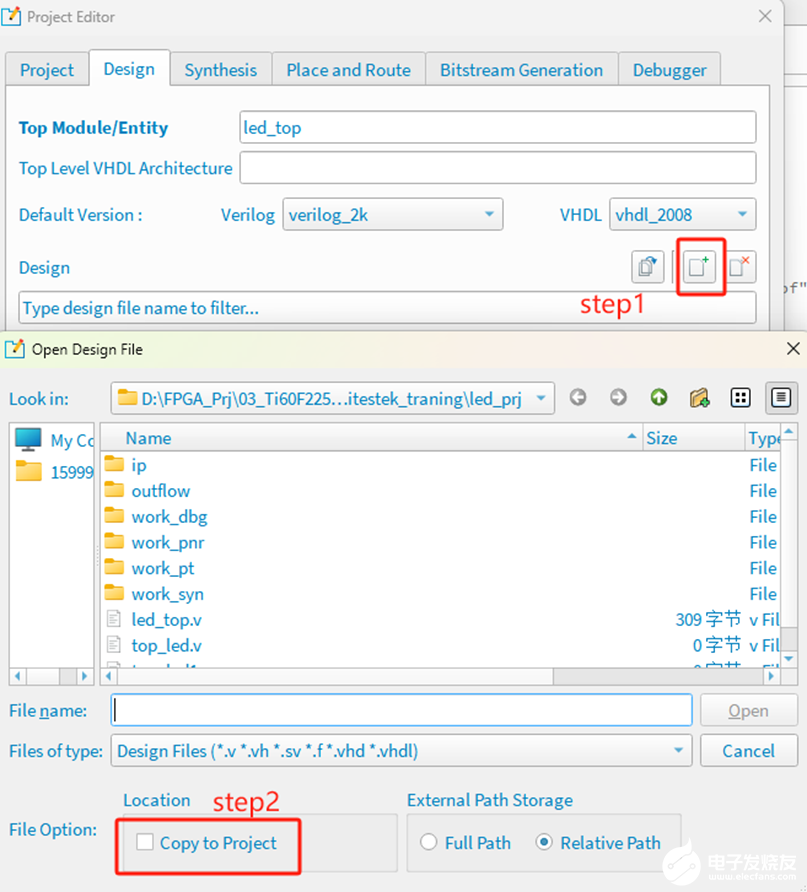

方法1:选择Design右击,点击Create 方法2:自己建立文件,添加文件到工程: Stp1:选择Design右击,点击Add

方法1:选择Design右击,点击Add 方法2:Project Editoràadd file Efinity还可以添加整个文件夹的文件,如图选copy to project

管脚约束

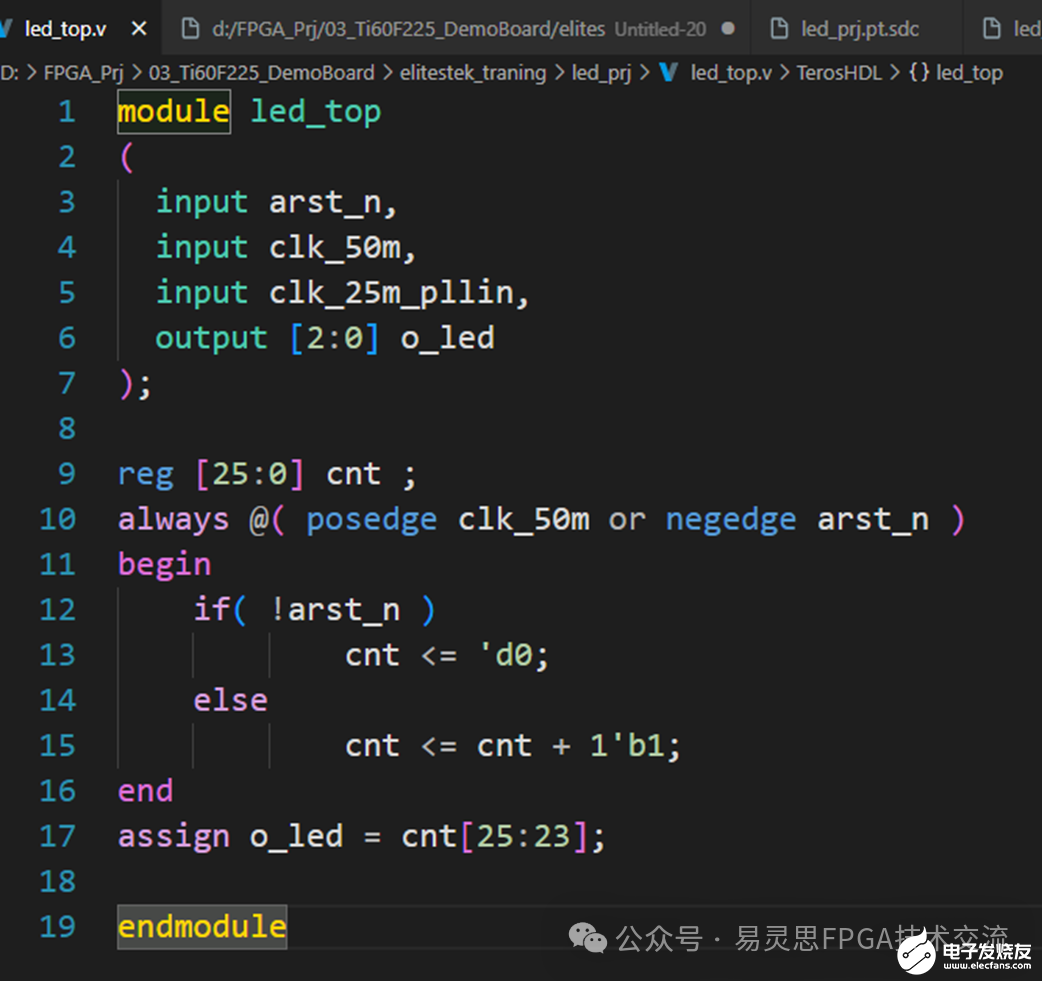

这里我们以一个LED点灯为例,代码如下:

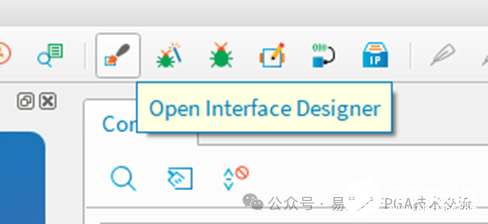

Efinty是通过interface designer工具来设置IO等和外设相关的接口及电气属性的。Interface designer操作界面的打开通过下面的Open Interface Desinger来实现。

Core 与interface的关系

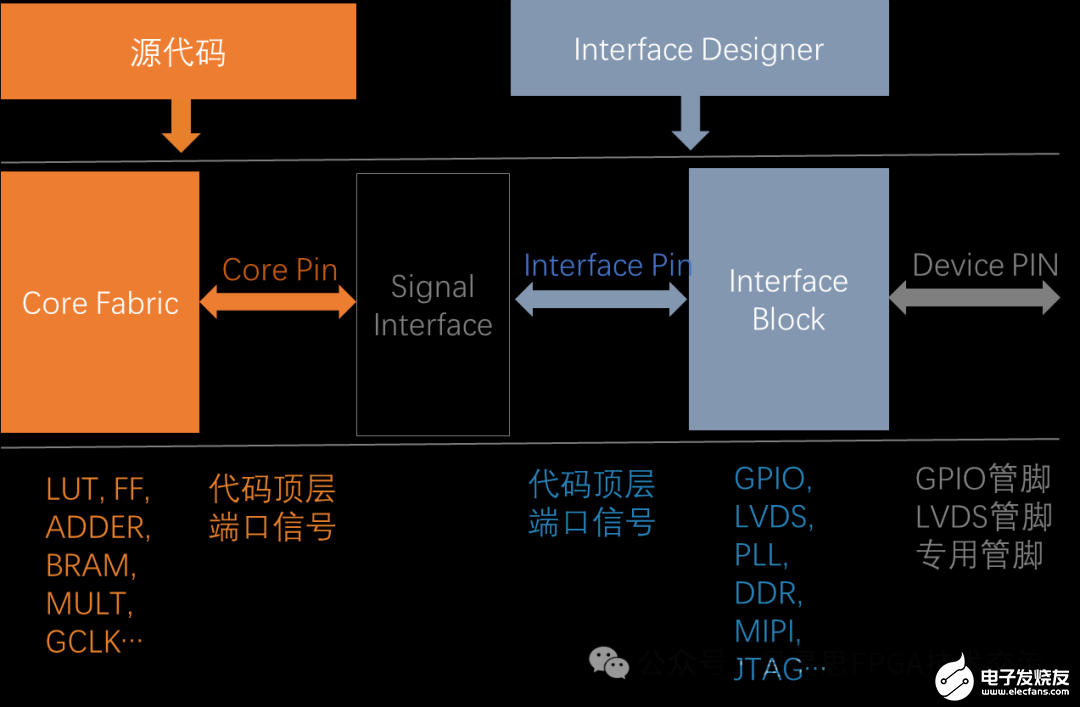

Eifinty采用的把逻辑资源和硬核资源分开的架构,代码部分只针对逻辑资源,也就是我们这里提到的Core,而IO及其他硬核部分的配置在interface Designer工具中。下图是interface与Core的关系,它们之间通过被称作Siganl Interface的连线资源实现互联。

因为习惯问题,使用者在最初一定会存在一些问题,但是习惯之后它也是有不少优势存在的。比如说,在前期的硬件设计中,只需要在Interface Designer中添加已添加的IO及其他需要的硬件接口,并通过一键检测就可以很清楚的知道与外设的连接是否合理,不需要考虑内部因为没有完整的程序而可能被优化的风险。另外有些interface的选项在修改之后可以不需要先编译而直接生成数据流。

interface与core的关系

interface界面

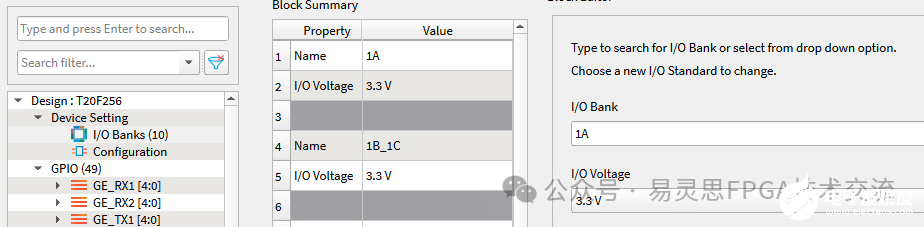

Bank电压的设置

告诉软件FPGA目前的bank电压,硬件电路的bank电压要和interface中的一致,如果电压设置不一致可能存在长时间运行致使芯片失效。设置位置在Device Setting -->I/O Banks

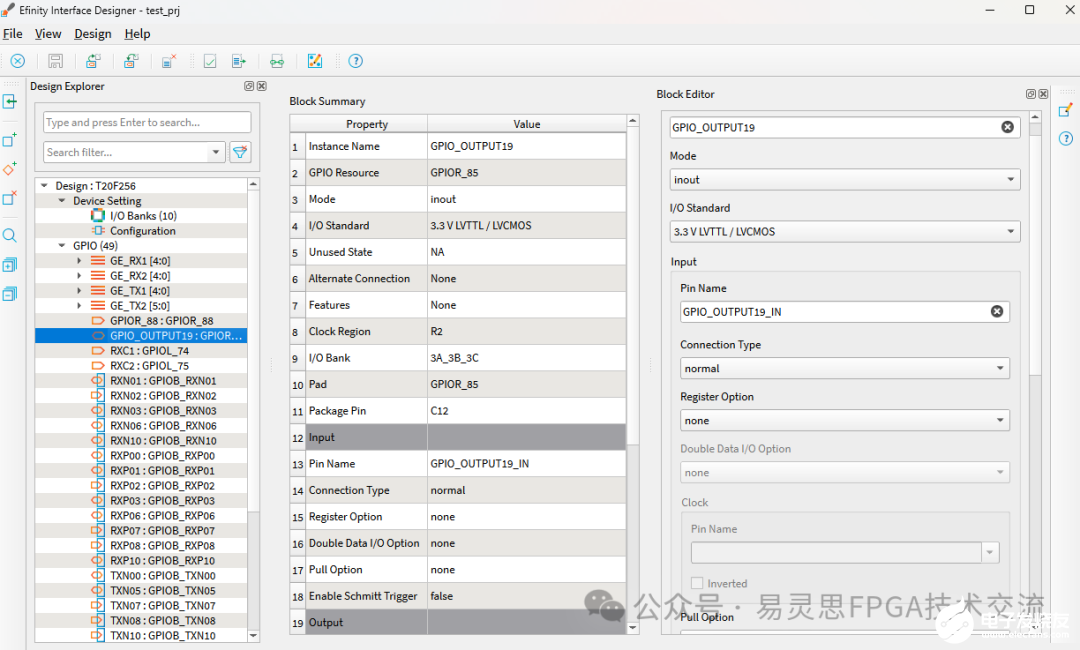

添加GPIO

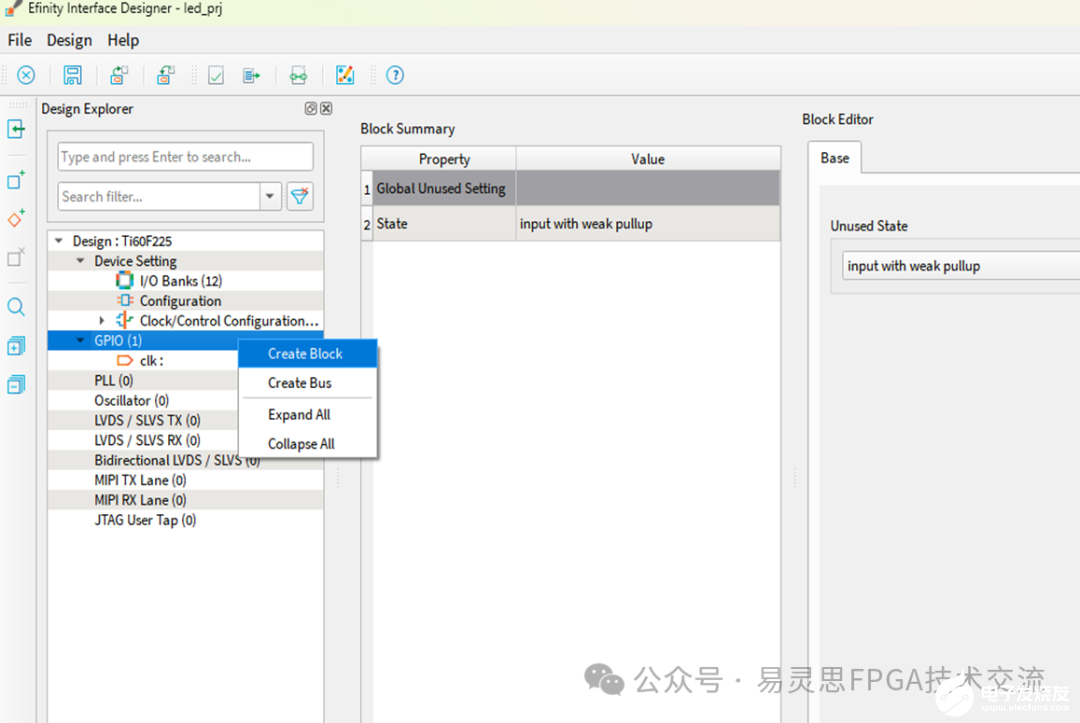

Step1:右键选择GPIO

Step2:根据选择的是单线还是多线来选择Create Block还是Create Bus

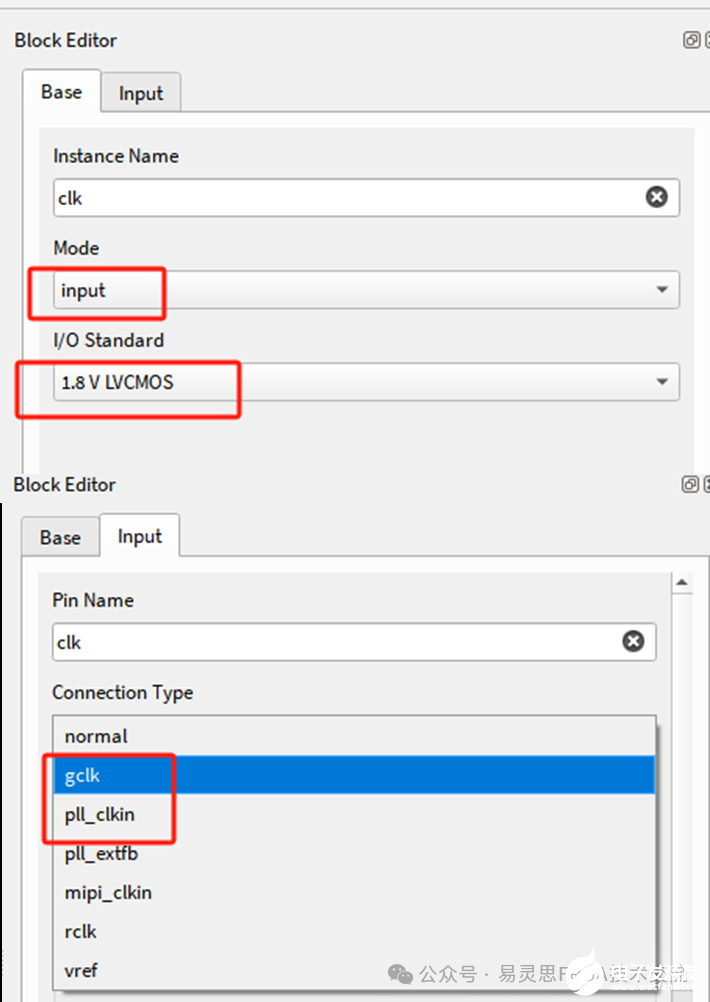

Step3:编辑IO属性,IO属性如下:

| 选项 | 选择 | 说明 |

| Mode |

Input, output, inout, clkout |

Input:把FPGA管脚设置为输入; Output:把FPGA管脚设置为输出; Inout:把FPGA管脚设置为双向管脚; Clkout:把FPGA管脚设置为时钟输出 |

| Connection Type | Normal,gclk,pll_clkin,VREF |

gclk走全局时钟网线,可以驱动PLL也可以直接驱动内部逻辑 用于普通的GPIO; PLL_CLKIN表示这个IO是用于驱动PLL的; 用于存储器的参考管脚 |

| Register Option | None,register | 是否添加IO寄存器,推荐添加。 |

| I/O Standard | 3.3v,1.8v,1.2V,1.5v | 设置IO的电平 |

| Double Data I/O Option | None,normal,resync | 是否设置IO为双延采样 |

| Clock | 当打开IO寄存器时需要添加指定寄存器的时钟 | |

| Drive Strength | 1,2,3,4 | 设置输出IO的驱动能力 |

| Enable Slew Rate | Yes,no | 是否命名能slew rate |

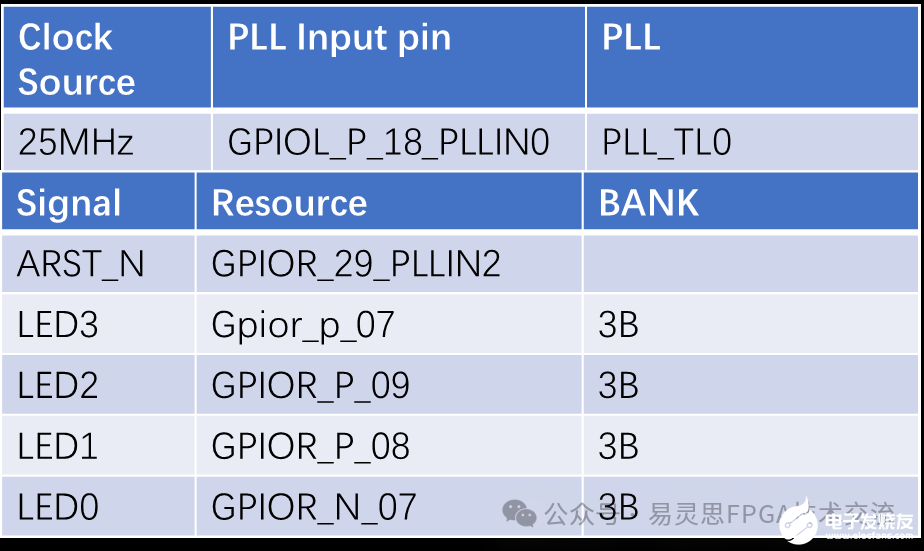

右键添加GPIO 针对上面的工程我们的参数设置如下: (1)Mode 设置为input (2) I/O Standard根据所在的Bank来选择电压 Instacne Name: clk Connection Type : pll_clkin

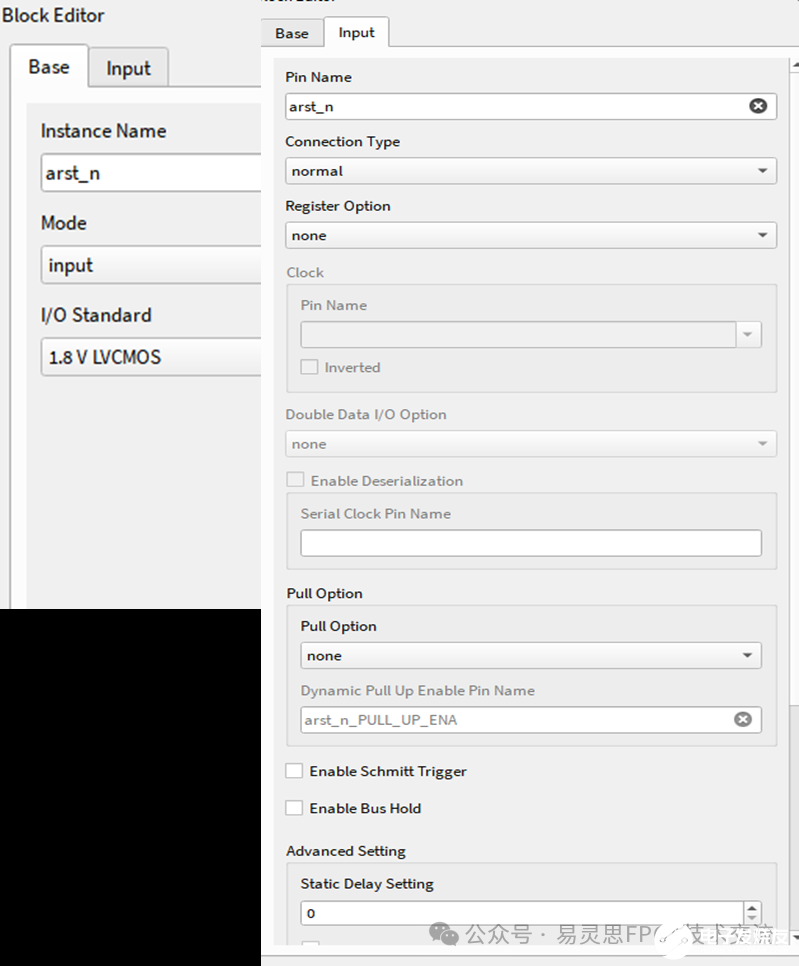

以arst_n为例 : Mode : input I/O standard :根据所在bank及bank电压设置 Connection Type: normal Register Option: none

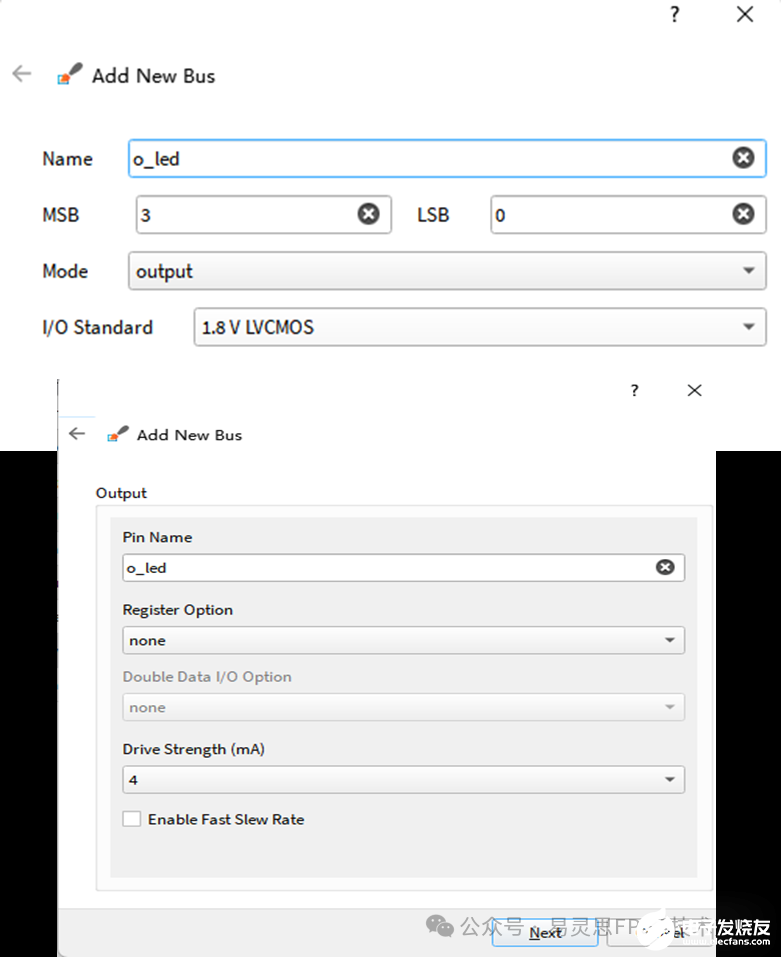

以4位输出的led为例: (1)Name :o_led (3)位宽从3到0 Mode: output

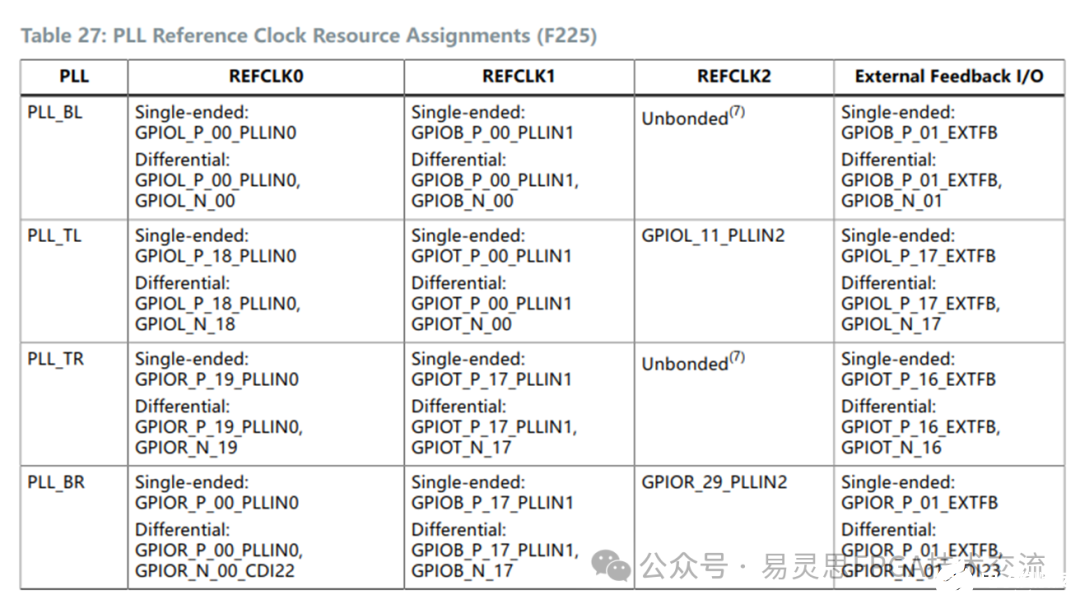

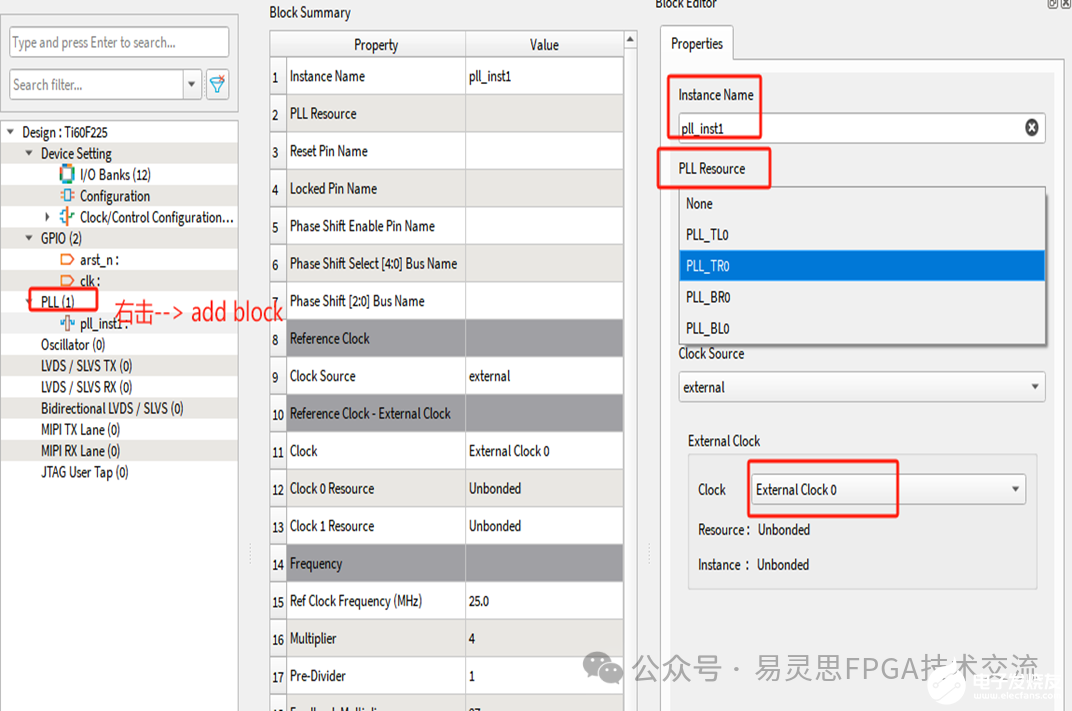

PLL设置 PLL是FPGA内部常用的配置项。Ti60F225有4个PLL,如下图所示,分别为PLL_BL,PLL_TL,PLL_TR和PLL_BR。

| Instance Name | 用户定义 | |

| PLL Resourec | ||

| Output Clock Inversion | on,off | 翻转时钟输出 |

| Connection Type |

gclk, rclk |

时钟类型 |

| Clock Source |

External, Dynamic,Core |

External指时钟通过IO驱动;Dynamic:支持多路时钟选择;Core:时钟通参考通过core供给 |

|

Automated clock Calculation |

打开时钟计算和设置窗口 |

针对上面的工程,我们的参数设置如下: 右击PLL ->add Block Instance Name:根据需要输入 PLL Resource:PL_TR0 Clock Source: external,core,dynamic External Clock :External Clock

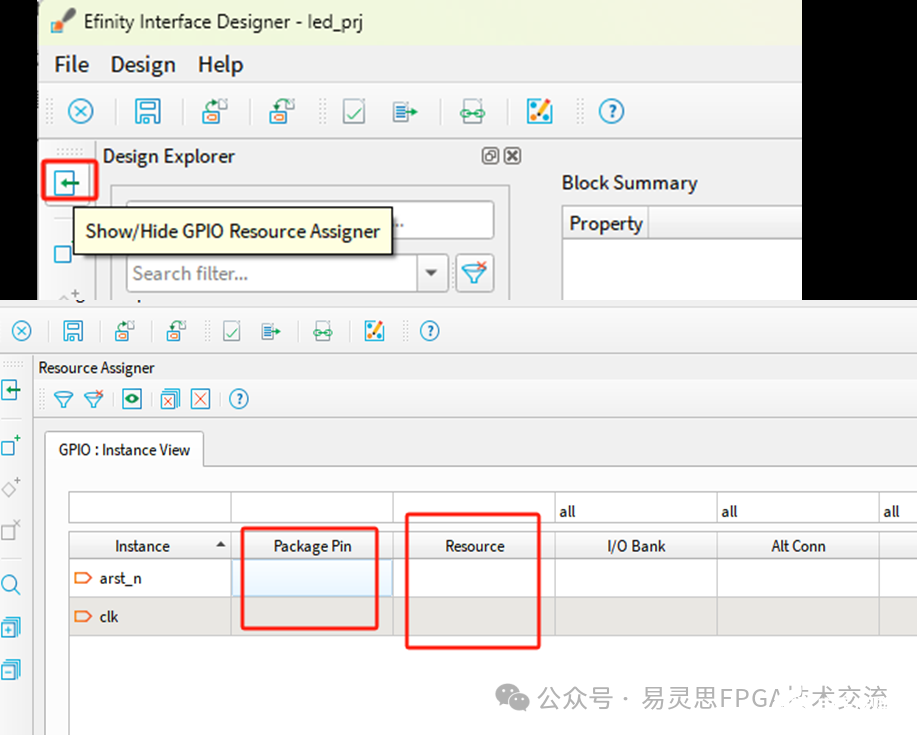

IO分配

点击Show/Hide GPIO Resource Assigner,在Package Pin或者Resoure位置输入管脚。

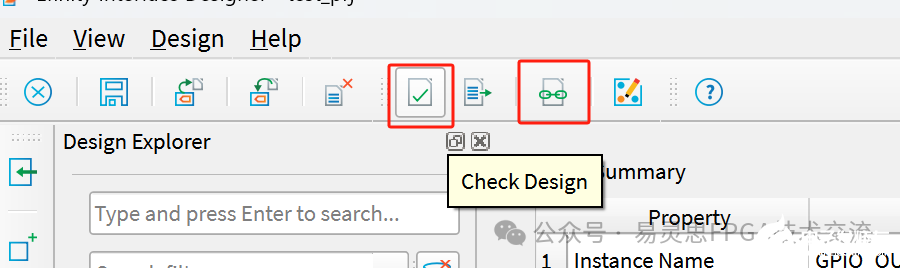

检测Interface设计是否存在问题。

保存设置,点击Check Design,检查interface是否存在问题。

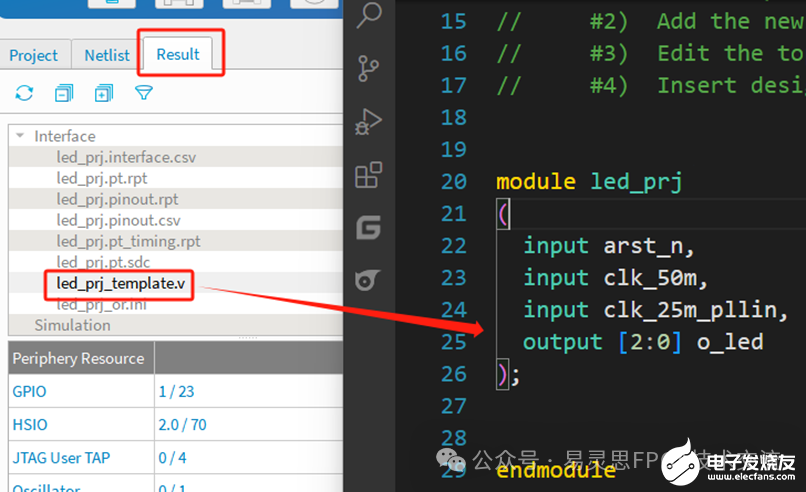

再点Generate Efinity Constraint Files,我们就可以在Result --> interface下面看到生成一些文件。通过xxx_template.v复制例化接口

添加约束

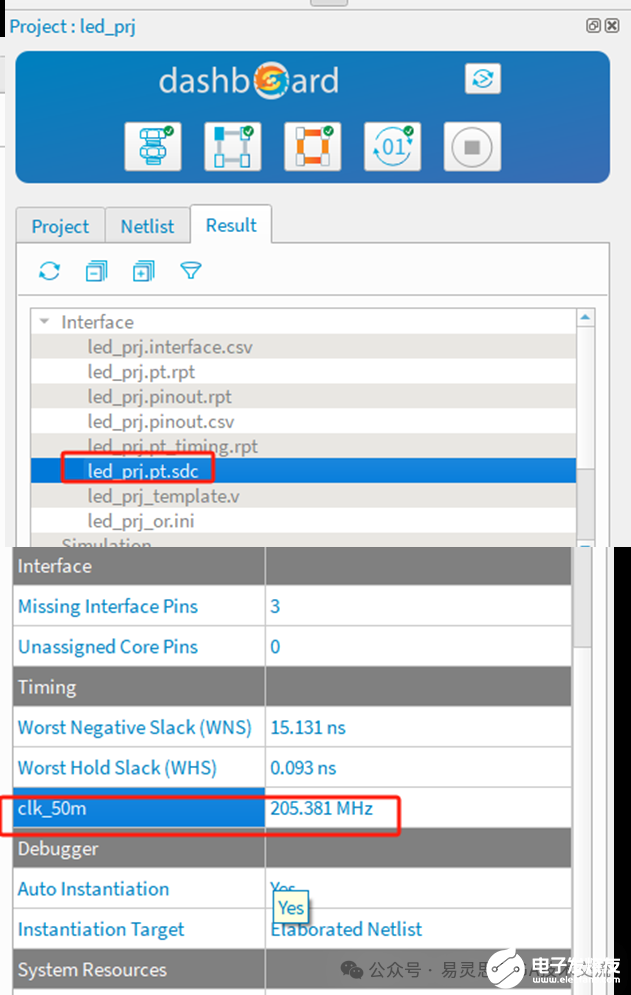

添加约束的目的是为了告诉FPGA你的设计指标及运行情况。在上面的生成约束之后,在Result àxx.sdc中提供约束参考(请注意该文件不能直接添加到工程中,需要热复制到别的指定目录),对于gclk时钟需要手动添加约束的时钟周期,对于PLL生成的时钟已经约束完整。

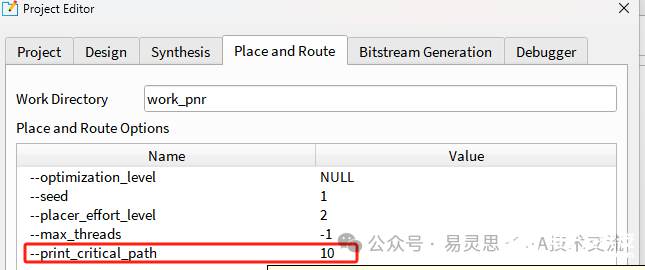

编译完成之后可以查看时序报告,也可以通过routing àxx.timing.rpt来查看路径详细延时信息,如果想查看更可以通过指令来打印或者通过print_critical_path来控制打印的路径数量 。

编译

点击dashboard中Toggle Automated Flow来设置是单步还是全程编译(暗色是单步),下面是综合,布局,布线,生成数据流,stop的相应按键。软件左下角会的编译进行提示编译进程。

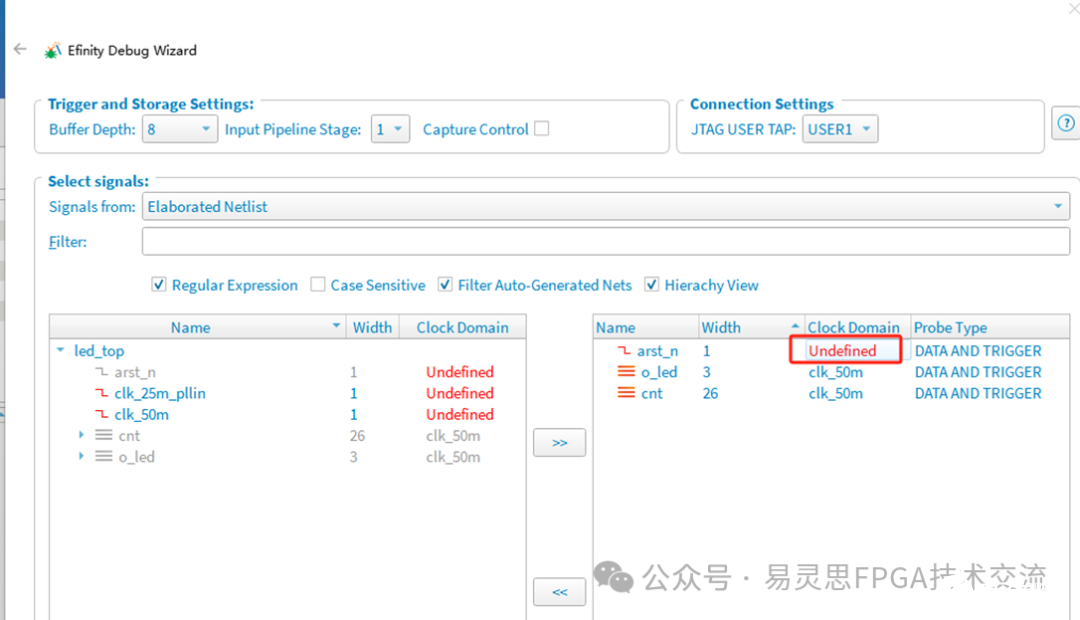

添加debug

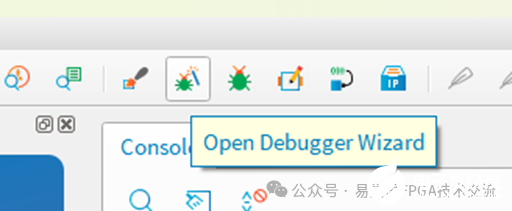

点击Open Debugger Wizard

(1)设置Buffer Depth

(2)Input Pipeline Stage

(3)Capture control

(4)JTAG USER TAP

(5)修改时钟域

(6)Probe Type

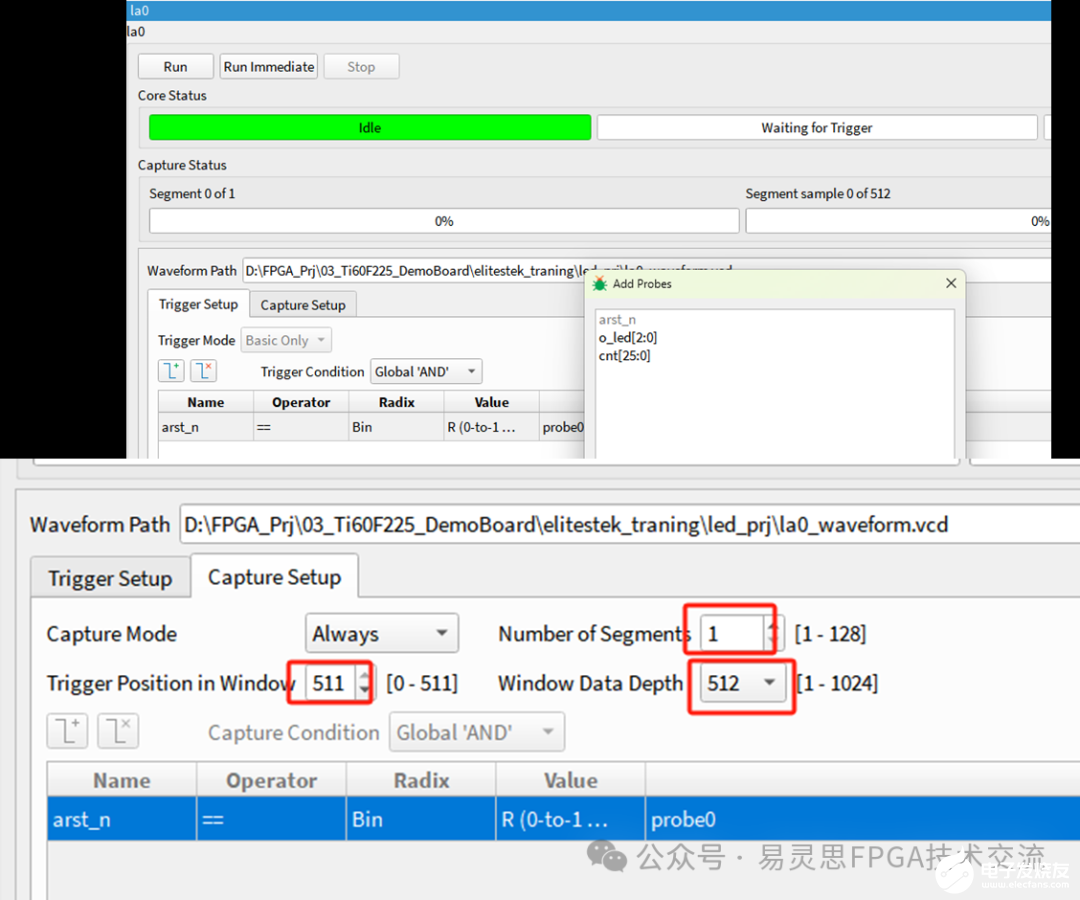

触发条件的设置

捕获设置:

•触发位置

•分段数量

•窗口尝试

下载程序 配置方式.易灵思的FPGA支持以下几种配置方式。

| 主动模式(SPI Active)— AS模式 | 通过SPI专用插座在线烧写FLASH,FLASH离线烧写好了再焊接,FPGA自己主动通过从非易失性的SPI FLASH读取bit流进行加载,支持X1 X2 X4,x8(不同的FPGA支持的位宽有区别) |

| 被动模式(SPI Passive)— PS模式 | 上位机或者MCU通过SPI接口向FPGA发送bit流文件,对FPGA进行加载 •支持X1 X2 X8 X16 X32 |

| JTAG模式 | 上位机通过JTAG口将bit流文件发送到FPGA,对FPGA进行加载 |

| SPI Active using JTAG bridge — Bridge模式 | 通过FPGA的JTAG口烧写和FPGA连接的SPI FLASH |

另外需要注意JTAG配置使用bit文件,Flash配置使用hex文件,配置过程中需要注意读取正常的ID,烧写flash可以勾去VerIfy After Programming节省时间

仿真

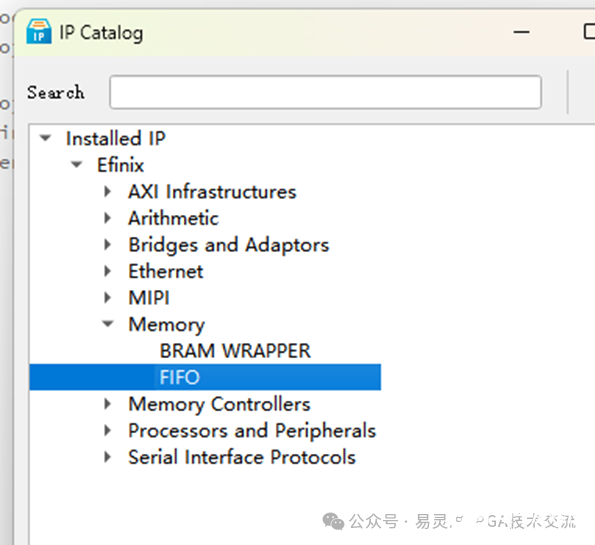

易灵思为所有IP提供了仿真模型

以FIFO为例 ,在工具栏中选择IP Catalog

Open IP Callog ->Memory ->FIFO->以默认参数生成IP 找到IP生成路径下的Testbench文件夹。把modelsim路径转向该文件夹(注意路径方向“/”) 运行do sim.do

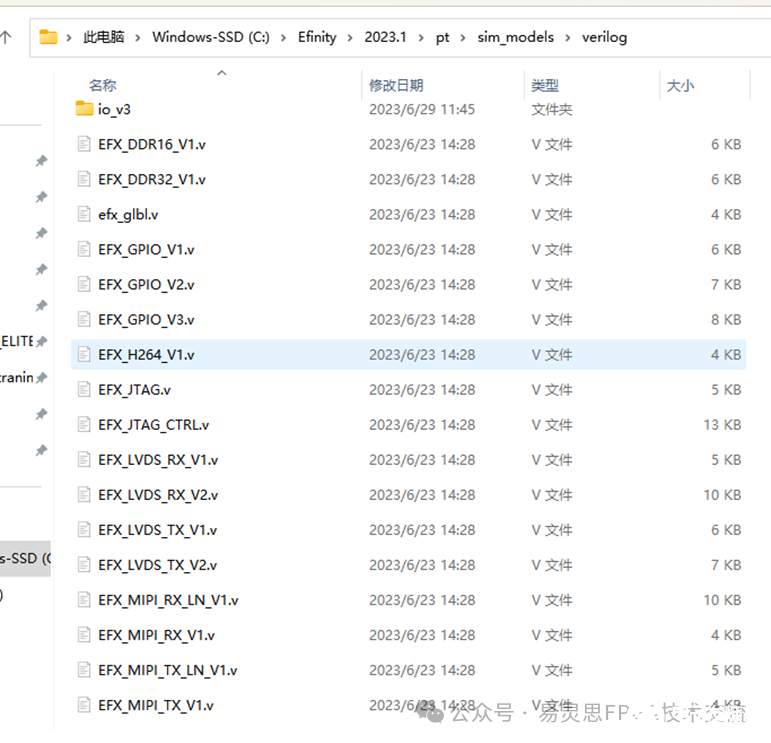

另外 关于interfce Designer接口的仿真模型在路径C:Efinity2023.1ptsim_modelsVerilog下。

- 相关推荐

- 热点推荐

- python

-

手把手教你学单片机之AVR入门视频教程2011-03-02 21777

-

力天手把手教你学ARM入门版代码2012-08-12 21372

-

原创手把手教你学习FPGA视频教程,不看后悔哟2013-08-14 34091

-

手把手教你如何去安装Keil C51软件?2021-07-01 1878

-

UG5.0安装视频教程(手把手教你如何安装)2009-02-06 1401

-

手把手教您笔记本的系统安装2010-01-20 2241

-

手把手教你安装Quartus II2016-09-18 1661

-

DSP开发软件及工具介绍--力天手把手教你学DSP之入门篇2017-10-20 2807

-

手把手教你如何开始DSP编程2018-04-09 1454

-

手把手教你如何安装机械硬盘和分区2019-03-05 145925

-

手把手教你学LabVIEW视觉设计2019-03-06 3572

-

手把手教你开关电源PCB排板2021-09-18 1911

-

手把手教你学FPGA仿真2023-10-19 1055

-

Efinity软件安装-v32024-03-29 1240

-

Efinity软件安装-v52024-11-01 2150

全部0条评论

快来发表一下你的评论吧 !