英诺达荣获“2024中国IC设计成就奖之年度创新EDA公司”奖项

描述

2024年国际集成电路展览会暨研讨会(IIC)在上海圆满落幕,本届展会和研讨会吸引了众多国内外Fabless、EDA/IP厂商参加。英诺达凭借在EDA领域的突出创新成果,荣获由AspenCore颁发的“2024中国IC设计成就奖之年度创新EDA公司”奖项。

静态验证EDA工具助力大规模芯片设计的创新突破

英诺达副总经理熊文受邀出席本届IC领袖峰会,并发表了题为《静态验证EDA工具助力大规模芯片设计的创新突破》的主题演讲,分享了英诺达在静态验证领域的最新技术成果,深入探讨了静态验证技术如何助力大规模芯片设计实现“设计左移”。

“设计左移”避免Debug成本指数级增长

过去几十年,SoC芯片的设计规模越来越庞大,为了实现更多的功能,芯片的复杂性也急剧增加。通常,一片SoC可能包含数十亿个逻辑门以及数百万个连接、若干个IP和存储器,以及多个电源域和时钟域。这给验证工作带来了不小的挑战,这些复杂连接的正确性对于SoC芯片的功能至关重要,若出现问题,会导致SoC芯片功能异常,甚至无法工作。

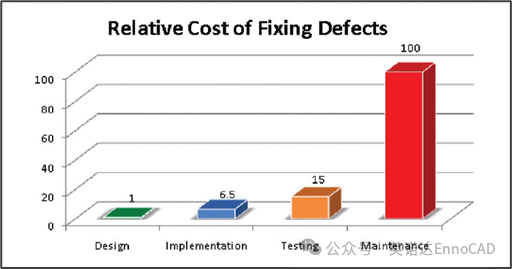

英诺达的副总经理熊文在演讲中指出,像SoC这种大规模芯片在Sign-off阶段发现、修复bug的成本很高,会需要多轮debug和验证的迭代,甚至影响到产品上市的时间。IBM统计在实现阶段修复一个漏洞或错误的成本是设计阶段的6.5倍,而到了测试阶段,这一成本更是激增至15倍。

不同设计阶段修复缺陷的成本呈指数级增长(Source: IBM)

所以“设计左移”就是指将设计流程后期执行的任务提前到更早的阶段进行,从而可以在早期发现并纠正关键bug,加快产品迭代的速度,这种策略不仅可以节省时间和资源,还可以提高产品质量和芯片的良率。而随着软件的重要性越来越高,另外一种形式的“设计左移”就是尽早让软件在硬件上运行进行调试。

为了应对“设计左移”的需求和趋势,设计厂商联同EDA厂商一起,不断在设计流程和方法学上进行创新和优化。静态验证是目前业界普遍使用的方法,在设计中通过配合动态仿真验证和形式化验证,可以提高验证的覆盖率,帮助设计师在设计开发的早期更快地发现和诊断设计缺陷,从而缩短设计验证所需的时间,简化SoC设计的整体开发周期,降低芯片开发的成本。

静态验证在低功耗设计中的应用

英诺达深耕数字中端EDA工具领域,以低功耗系列工具为突破口,纵深布局静态验证技术,横向拓展相关产品线,致力于为芯片设计提供全面的静态验证解决方案,目前已经发布了EnFortius凝锋低功耗系列和EnAltius昂屹静态检查系列EDA工具。

以低功耗设计为例,静态验证是如何在该领域中应用的呢?功耗一直以来是芯片设计的重要考量因素,也是导致流片失败的主要原因之一。面对日益严峻的功耗挑战,设计团队需要先进方法学和工具的支持,在设计全流程中进行低功耗设计。

低功耗设计面临着多重挑战:

电路复杂度提高:为了降低功耗,芯片设计往往使用多电压域,这使得电源管理和设计更加复杂。

UPF标准版本太多:电源管理需要使用UPF标准进行描述,但大多主流工具难以支持该标准的所有版本。

早期电源分析困难:在没有物理器件的情况下,设计早期难以进行准确的电源估算和分析。

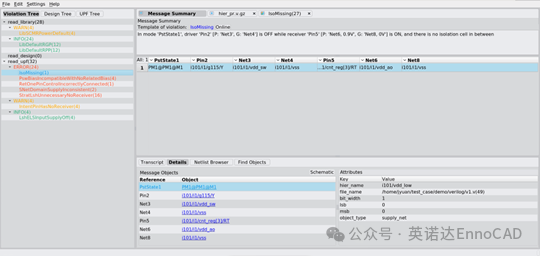

英诺达EnFortius低功耗设计静态验证工具(LPC)基于先进的功耗设计方法学,帮助IC设计师从RTL到GDS全流程进行低功耗设计管理,确保UPF和功耗设计意图的正确性和一致性。这款工具不仅可以快速准确地查错,还可以帮助用户快速定位问题根源。

GUI界面简化了查错过程

在功耗分析方面,为了帮助设计团队更早掌握功耗水平,及早对功耗进行优化,英诺达EnFortiusRTL级功耗分析工具(RPA)采用自主研发的综合引擎和物理线网模型,大幅提高功耗估算的准确性,帮助设计团队从RTL阶段开始捕捉功耗趋势,甄别功耗热点。

熊文在演讲中表示:“静态验证作为一种有效的低功耗设计方法,可以从系统设计、RTL设计到物理实现的全阶段进行功耗分析和优化。通过静态验证方法,设计团队能够尽早发现和修复功耗相关问题,避免流片后功耗超标的风险。实践证明,越早进行功耗分析和优化,效果越好。因此,设计团队应积极采用静态验证等先进方法,在设计早期就开始进行功耗管理,以确保芯片设计成功。”

审核编辑:刘清

-

国民技术荣获2025中国IC设计成就奖之年度MCU2025-04-01 1381

-

Cadence荣获2025中国IC设计成就奖之年度卓越表现EDA公司2025-03-31 864

-

芯和半导体获2025年度中国IC设计成就奖之年度创新EDA公司奖2025-03-28 880

-

川土微荣获“2024中国IC设计成就奖之年度杰出市场表现奖-汽车电子”2024-04-02 1499

-

芯行纪荣获“2024中国IC设计成就奖之年度创新EDA公司”奖项2024-04-01 1781

-

年度技术突破EDA公司!思尔芯凭先进解决方案荣获2024中国IC设计成就奖2024-03-30 1137

-

喜讯!雅特力荣获2023中国IC设计成就奖之年度技术突破IC设计公司2023-04-07 1401

-

芯和半导体获2023年度中国IC设计成就奖之年度创新EDA公司奖2023-03-31 1121

-

方寸微电子荣获“2022年中国IC设计成就奖”2022-08-19 879

-

概伦电子荣获2022中国IC设计成就奖之年度产业杰出贡献EDA公司2022-08-18 1040

全部0条评论

快来发表一下你的评论吧 !