DSP应用设计关键之接口设计(一)

处理器/DSP

描述

一、基于DSP的USB接口设计

1 引言

通过DSP 处理的数据往往要传输给PC 机进行存储和再处理,那么就必须解决DSP 与 PC 机之间的高速通信问题。本设计方案以德州仪器(TI)的C5000 系列DSP 芯片TMS320VC5416为微处理器,利用Cypress公司提供的USB2.0接口芯片CY7C68001 实现了USB2.0 从机接口设计,从而使PC机与DSP 通过USB2.0 接口实现高速双向地传输数据。

2 TMS320VC5416 与CY7C68001 EZUSBSX2硬件接口设计

系统方案采用PC机作为上位机,负责USB总线上检测到设备接入并进行枚举、识别的过程,并且可以通过在PC机上运行应用程序来控制数据的传输。USB芯片作为USB设备端,连接DSP与上位机的数据交换。DSP用于实现USB协议,通过DSP编程实现DSP数据通过USB接口与PC机通信,且USB芯片的描述符写入及各种命令状态的处理均通过DSP编程实现。

TMS320VC5416 是TI 的一款16bit 定点高性能DSP,由于VC5416的功耗低、性能高,其分开的指令和数据空间使该芯片具有高度的并行操作能力,在单周期内允许指令和数据同时存取,再加上高度优化的指令集,使得该芯片具有很高的运算速度,同时该芯片本身具有丰富的片内存储器资源以及多种片上外设,因此在工程界得到了广泛的应用。

Cypress 公司的CY7C68001 EZ-USB SX2 是一款高性能、使用方便的USB2.0 接口芯片,满足USB2.0 协议,可工作在高速(480Mbps)或全速(12Mbps)模式下,提供一个控制端点用于处理USB设备的请求以及四个可配置端点用于传输控制和数据信号,这四个端点共享一个4KB的FIFO空间,具备标准的8位或16位外部主机接口,可无缝连接多种标准微处理器,比方说DSP、ASIC和FPGA等,并可根据需求设置为同步或异步接口,片内集成锁相环(PLL),该芯片广泛应用于DSL调制解调器、MP3、读卡器、数码照机、扫描仪、打印机等设备。

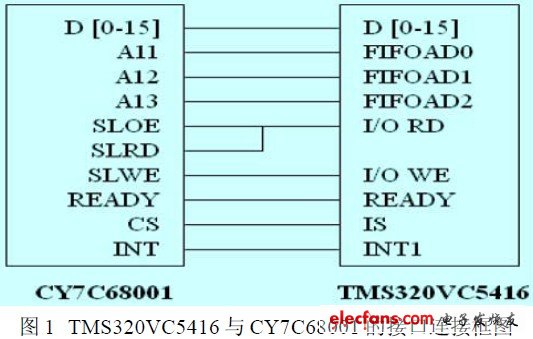

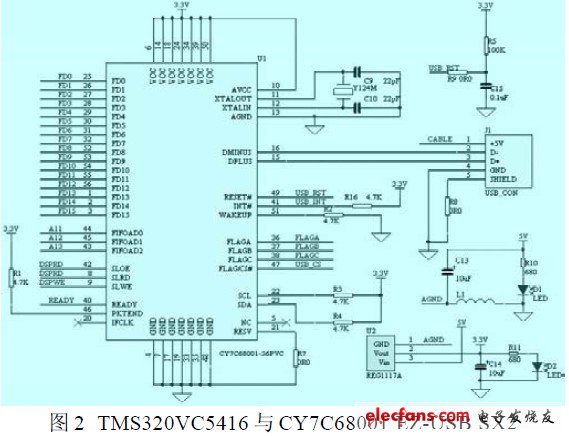

系统的硬件接口设计如图1、图2所示,两者通过数据、地址总线以及读、写信号线等进行通信,CY7C68001的片选信号连接至TMS320VC5416 的I/O空间片选信号上,CY7C68001 的FIFO扩展在VC5416 的I/O 空间上。

电源部分采用一片1117 将5V 转为3.3V供给CY7C68001EZ-USB SX2,模拟地与数字地之间采用磁珠连接,复位部分采用RC电路设计,且芯片资料上介绍有典型值100KΩ和0.1μF。

3 接口操作原理

CY7C68001 有两个外部接口:

(1) 命令接口:用来访问CY7C68001 寄存器、Endpoint 0缓冲器,以及描述表。

(2) FIFO数据接口:用来访问4个1K字节的FIFO中的数据。

这两个外部接口均可以通过同步或异步的方式进行访问。

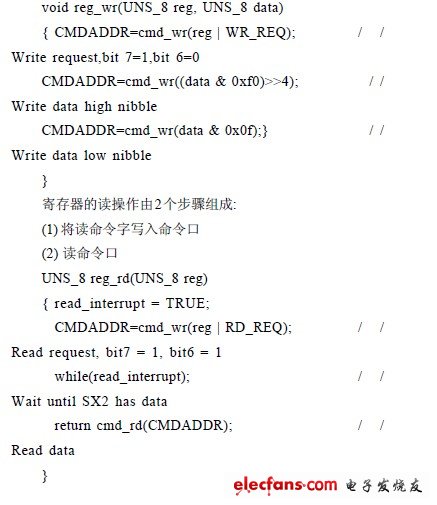

本设计采用异步的方式进行访问。根据图3 的地址分配,利用TMS320VC5416 的三根高位地址线(A11、A12、A13)连接CY7C68001 的FIFOAD0/1/2,用以选择FIFO2、FIFO4、FIFO6、FIFO8以及命令接口,其地址表如图3所示。CY7C68001的地址线FIFOADR[2:0]为100B 时,选中CY7C68001 的命令口(Command)。通过CY7C68001的命令口,可以访问37个寄存器、Endpoint 0缓冲器(64个字节FIFO)和描述表(500个字节FIFO)等,对这些寄存器进行读写方式采用二次寻址方式,即首先通过命令口将要寻址的寄存器的子地址和操作类型(读或写)写入,然后再通过命令口将数据读出或写入相应的寄存器。

写入命令口的内容称为命令字,命令字包含要寻址的寄存器的子地址,或要写入寄存器的数据的高4位或低4位。读命令口必须要跟在给命令口写读命令字之后,读出的为相应寄存器的8位数据。所以,寄存器的写操作由3 个步骤组成:

4 USB 接口的软件设计

USB接口的软件设计由两部分组成:一是在PC机Windows中运行USB 2.0 Utility 工具,是一个Windows 图形用户界面软件,提供CY7C68001 与Windows 操作系统的接口程序,使得CY7C68001的开发变得简单。二是在在DSP中运行嵌入式应用程序代码,提供硬件的驱动,用来管理CY7C68001进行不同方式的数据处理,从而实现USB2.0 传输协议。

4.1 USB 接口的软件设计流程

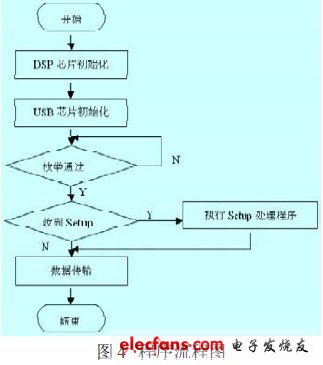

USB接口的软件设计,DSP端代码大致包括DSP芯片初始化(vc5416_init 函数)、USB芯片初始化(sx2_init 函数)、USB芯片配置程序( s x 2 _ s e t u p 函数) 以及USB 芯片数据读写程序(sx2_processdata 函数),程序流程如图4 所示。

DSP芯片初始化(vc5416_init函数)主要负责设置VC5416的工作频率,配置SWCR以及SWWSR寄存器,另外本应用系统采用一个GPIO引脚作为68001的复位信号,所以还需要对其进行相关设置。

USB芯片初始化(sx2_init函数)主要负责清除Buffer缓冲区以及使能VC5416 的外部中断INT1,待初始化结束后发出READY中断,此时DSP将描述符写入68001,进行枚举过程,待枚举通过后发出ENUMOK中断,枚举方式可以采用外部EEPROM通过I2C总线上电后从外部导入描述符,也可采用通过运行DSP程序从DSP导入到68001,本应用系统采用第二种枚举方式。

USB芯片配置程序(sx2_setup函数)是在命令通道(0节点)收到无法自动处理的上位机请求,68001向VC5416发出SETUP中断后执行的程序,此时VC5416 通过对SETUP寄存器连续执行八次读操作流程即可得到8字节请求,系统可以响应该请求或STALL该请求。

USB 芯片数据读写程序(sx2_processdata 函数)即PC 机与USB从设备端遵照USB传输协议进行数据通信。

CY7C68001的地址FIFOAD[2:0]为100时,选中CY7C68001的命令接口。对于命令接口的读写要分两步进行,即在READY有效时,先通过命令接口写入要寻址寄存器的子地址和操作类型(读或写),之后,在READY再次有效时分两次读写命令接口,即可读写一个字节的数据。

4.2 中断服务程序设计要点

DSP使用一个外部中断引脚(INT1)与CY7C68001的INT脚相连,USB总线上产生一系列的活动,均会触发相应的中断,一旦中断产生,DSP 会从CY7C68001 的Command 口中读取相应的值,来判断产生的是何种中断。

CY7C68001 EZ-USB SX2 包括六个中断源:SETUP(收到来自于USB 上位机(PC)发送过来的Set-up 包时产生的中断)、EP0BUF(端点0 缓存可用时产生的中断)、FLAGS(OUT 端点FIFO的状态从空变为非空时产生的中断)、ENUMOK(SX2枚举完成后产生的中断)、BUSACTIVITY(SX2检测到总线活动时产生的中断)以及READY(SX2上电并且复位完毕后产生的中断),每一个中断源都可以通过置位或清除INTENABLE寄存器中相应位来使能或禁止。

CY7C68001芯片采用中断缓冲机制,每次只会有一个中断源,其他中断源只有在上一个中断被读走后才会发出新的中断请求。

因此,当一个中断产生时,INT引脚为低电平状态,同时中断状态位会置入命令接口,在进入中断程序后应先对中断源进行判断,首先判断是否是读寄存器所产生的中断,如果是则将数据准备好标志位置1然后返回,否则外部PC通过选通SLRD/SLOE信号从命令接口中读取中断状态位来判断产生的是何种中断,然后根据中断源进行相应操作,DSP读取中断状态位后自动清除中断标志位。

5 结束语

通过硬件平台的搭建和软件程序的实现,验证了该接口电路可以满足高速信号处理的数据传输要求,并具有速度快和可靠性高等优点。

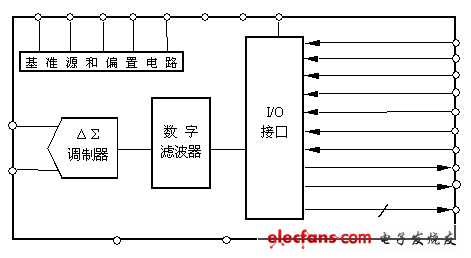

二、FIFO实现高速模数转换器与DSP的接口

在数字信号处理系统中,大多数高速模数转换器都不能直接与DSP相连接。FIFO恰好架起了DSP与ADC之间的一座桥梁,因为它能缓存大量的数据块。同时由于DSP访问外部存储器器件必须通过外部存储器接口External Memory Interface, EMIF, 而C6000系列DSP的EMIF具有很强的接口能力。它不仅具有很高的数据吞吐率(最高1200MB/s),而且可以与目前几乎所有类型的存储器直接接口。本文介绍了用FIFO 在DSPs和模拟前端(AFEs)之间进行数据缓存的实现方法。

1 AD9042高速模数转换器

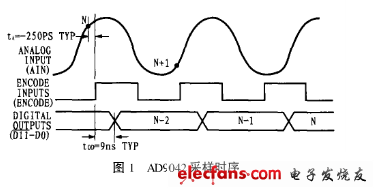

AD9042是一款低功率12bit的41MSPS模数转换器。它的快速、高分辨率特点使其非常适合于视频、多媒体、图像处理、高速数据采集和通信等很多应用领域。图1为AD9042的采样时序图。由该图可以看出:AD9042不能与TMS320C6205直接相连。

因为ADC总是在进行数据输出,因此输出无高阻状态,而如果模数转换器直接与DSP总线相连接,DSP就不能使用其它外围设备了,而且DSP必须在每个转换时钟周期读一次采样数据,这样,即使使用DMA通道传输也是不可能实现的,因为其它外围设备也要使用总线。

虽然采样锁存可以解决数据总是输出的问题,但是,如果模数转换器运行在41MSPS,那么,DSP每24ns就要读一次新采样。这将占去DSP中的大部分I/O带宽,此时如果DSP处于busy态,那么在24ns内就不能读取下一次采样,这样将使数据丢失。

一个比较好的解决办法是使用FIFO作为输入缓冲,由ADC把采样转换的值同步写进FIFO。每写入一块数据便向DSP发出一信号,以提醒DSP从FIFO中读取数据块。这样比单次读的效率要快很多。

2 CY7C4265-10AC同步FIFO

CY7C4265是高速低功耗CMOS时钟FIFO存储器。它是一款同步FIFO,意思是它的读写端口使用同步接口,每一个端口的时钟都是互相独立的,这些时钟可以同步,也可以异步。这使得FIFO的读写口能以不同的速度运行。传统的FIFO在进行数据传输时通常要求额外的控制逻辑,而新一代CY7C4265则可实现FIFO与DSP之间的无缝连接。3 FIFO与EMIF的连接

C6000系列DSP的EMIF具有很强的接口能力,它可以连接不同类型的存储器,如异步SRAM?SDRAM、SBSRAM等。

3 EMIF与FIFO的接口

CY7C4265 FIFOs提供有与DSP的无缝连接,这样的无缝连接要求FIFO作为一个输出缓冲器。而当FIFO作为输入缓冲器时,FIFO是EMIF的唯一异步设备。本设计恰好让FIFO作为输入缓冲器,且就此一个异步设备,因而避免了复杂的接口逻辑。

图2是EMIF与FIFO接口的具体硬件实现,FI-FO的半满标志HF作为DSP的输入信号。HF用于告诉DSP此时FIFO中的有效数据是可以读取的(而且容量是FIFO总大小的一半),以便DSP产生一个中断来读取FIFO中的数据块。

3.1 DSP读FIFO时序

在这个高速微弱信号数据采集卡的设计中,C6205的时钟频率为200MHz,且没有使用其它外部控制逻辑。图2中,EMIF异步接口提供的控制信号可以通过不同的组合(并非都需要)实现与不同类型器件的无缝接口。EMIF的CExCTL寄存器负责设置异步读/写操作的接口时序,以满足对不同速度异步器件的存取要求。

C6000异步接口时序具有很强的可编程性,每个读/写周期由三个阶段构成:建立时间(Setup)、触发时间(Strobe)、保持时间(Hold)。其中建立时间是从存储器访问周期开始(片选?地址有效)到读/写选通有效之前的时间;触发时间是读/写选通信号从有效到无效之间的时间;保持时间则是从读/写无效到访问周期结束之间时间。

DSP的ARE信号作为FIFO的读时钟,FIFO在ARE的上升沿在总线上输出数据,DSP和FIFO的独立时序参数值。

根据DSP的异步读时序,为了完成C6205的建立时间,第一个数据的读取必须满足下式:

Setup+Strobe ≥td?CK-AOEV?max+tOEmax+tSU?EDV-CK?min

根据上式,在最差情况下,建立和触发时间必须大于15ns(4ns+7ns+4ns)。当DSP的时钟频率为200MHz时,一个时钟周期应该是5ns。此时如果Setup和Strobe的值都取1,则Setup+strobe为10ns,故不能满足时序要求,因此Setup和Strobe这两个可编程参数若一个取1,另外一个必须大于等于2。而实际上,Setup和Strobe可以都取1,其原因是C6205不论是连续存取还是单次存取操作,在存取第一个数时,EMIF会自动将最小建立时间设置为2。

而对于以后数据的读取,OE总是有效。现在主要考虑的是FIFO的访问时间应满足下式:

Hold+Setup+Strobe ≥tAmax+tSU?EDV-CK?min

也就是说,一个完整的数据访问时间必须大于12ns(8ns+4ns),即Hold+Setup+Strobe ≥3;要完成C6205的保持时间,必须满足下面两个公式:

td?CK-AREV?min+tAmin ≥ th?CK-EDV?min

Hold ≥th?CK-EDV?min-td?CK-AREV?min-tOHZmin

当上边的式子满足条件时,-0.2+2>0.8。为了得到最小的Hold时间,此时Hold可以为0ns,也就是说,Hold可以被编程为0。

最后要满足的条件是时钟的高低时间。因为FIFO的时钟信号直接由ARE产生,因此ARE信号保持低电平的时间必须大于FIFO的时钟周期。即:

Strobe ≥tCLKL min

Hold+Setup ≥tCLKH min

Setup+Strobe+Hold ≥tCLK min

由以上七个式子可知,在200MHz的钟频率下,CExCTL寄存器中Setup/Strobe/Hold的值可以作如下设置:

Setup=1,Strobe=1,Hold=1;

此时,DSP读取FIFO中数据的速度为66.7MHz。

4 结论

FIFO在ADC高速模数转换器与DSP的通讯过程中起到了很好的数据缓冲作用,其标志位可被用来控制FIFO中数据的读取。如果选用内部时钟频率为133MHz的SN74V2×5-7系列FIFO,DSP读取数据的速度可以达到100MHz。

三、PCI总线接口与DSP的HPI接口

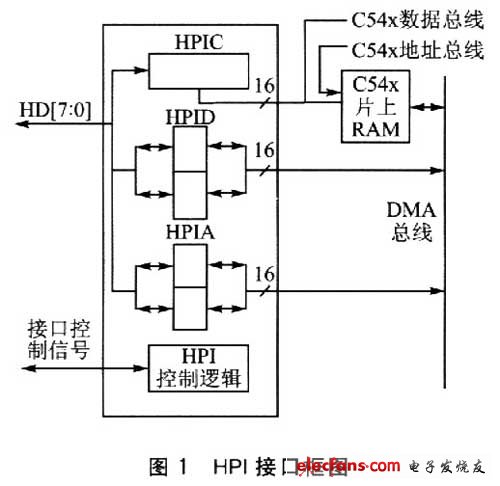

1 HPI接口功能及特点

主机接口HPI(Host Pott Interface)是C54x DSP系列定点芯片内部具有的一种并行接口部件,主要用于与其他总线或CPU之间进行通信,其接口框图如图l所示。主机是HPI口的主控者,HPI口作为一个外设与主机连接,使主机的访问操作很方便。主机通过以下单元与HPI口通信:专用地址和数据寄存器、HPI控制寄存器以及外部数据和接口控制信号。HPI有两种工作方式:共用寻址方式(SAM)和仅主机寻址方式(HOM)。在SAM方式下,丰机和C54x都能寻址HPI存储器;在HOM方式下,仅能让主机寻址HPI存储器,C54x则处于复位状态,或者处在所有内部和外部时钟都停止工作的IDLE2空闲状态(最低功耗状态)。

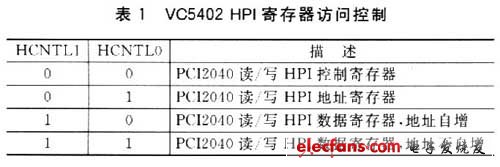

VC5402是TI公司推出的一款性价比极高的16位定点处理器。它是C54x系列中应用比较广泛的一种芯片,有着丰富的接口资源,是一种集数据处理和通信功能于一体的高速微处理器。VC5402 HPI口是一个增强的8位主机接口,它通过HPI控制寄存器HPIC、地址寄存器HPIA和数据锁存器HPID来实现与主机之间的通信。主机通过外部引脚HCNTLO和HCNTL1选中不同的寄存器,则当前发送8位数据就到该寄存器。控制寄存器HPIC既可以被主机直接访问,又可以被DSP片上CPU访问。在使用上,由于主机接口总是传输8位字节,而HPIC是一个16位寄存器,所以主机向HPIC写数据时,需要发送2个相同的8位数据。地址寄存器HPIA,只能被主机直接访问。主机将HPIA寄存器视为一个地址指针,借助于HPIA主机可以访问VC5402全部的片上存储器。另外HPIA具有自动增长的功能,在自动增寻址模式下,一次数据读会使HPIA在数据读操作后增加1,而一个数据写操作会使HPIA操作前预先增加l。这样如果使能了该功能,则只须设定一次HPIA即可实现连续数据块的写入和读出。数据寄存器HPLD,只能被主机访问。如果当前进行的是读操作,则HPID中存放的是要从HPI存储器中读出的数据;如果当前进行的是写操作,则存放的是将要写到HPI存储器的数据。

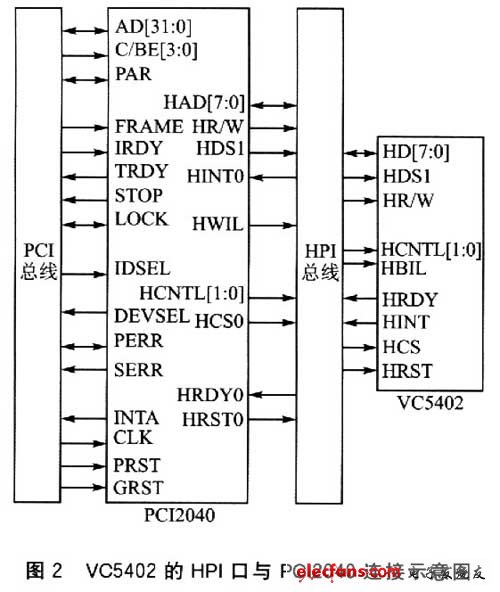

2 VC5402的HPI口与PCl2040的接口设计

2.1 PCI总线及其实现方法

PCI局部总线是32或64位数据总线,32位PCI总线在读写传送中支持132Mb/s的峰值传送速率,64位PCI传送支持264Mb/s峰值传送速率。对于64位66MHz的PCI总线,传送速率可达528Mb/s。PCI总线协议规范复杂而庞大,因此需要借助总线接口来实现。实现PCI总线协议一般有两种方法:一是用FPGA设计实现,但PCI协议比较复杂,因此难度较大;二是采用PCI总线控制芯片,如AMCC公司的S5933和PLX公司的PCI9052等通用的PCI接口芯片。TI公司专门推出了针对PCI总线和DSP接口的芯片PCI2040,它不但实现了PCI总线控制的功能,而且提供了和DSP芯片的无缝接口,因而大大降低了系统设计的复杂度,缩短了开发时间。

2.2 P012040与DSP接口设计

PCI2040足TI公司设计的专门用来实现C5000/C6000系列DSP和PCI总线进行接口的专用芯片,可以通过8位或16位HPI接口与C54x/C6xDSP实现无缝连接。PCI2040通过HPI接口与VC5402连接。PCI2040的HPI口为8/16位数据传输接口(8位还是16位,依据所挂接的DSP的类型)。主机作为传输的主设备,从机DSP不能发起传输。主设备PCI2040可以读/写DSP内存,DSP HPl口可以访问DSP所有的片上资源,PCI2040和VC5402之问的通信主要靠DSP的HPIA、HPIC、HPID三个寄存器完成。VC5402的HPI与PCI2040口的连接如图2所示。

PCI2040的数据总线HAD0~HAD7与VC5402 HPI口的数据总线HD0~HD7相连,用于主机和DSP传输数据。PCI2040芯片的HPI口的HCNTLl和HCNTL0引脚分别与DSP的HCNTLl和HCNTL0引脚相连,以实现其对HPI寄存器的访问。具体HPI寄存器的选择和访问模式的确定由DSP的HCNTLl和HCNTL0引脚的状态决定,表1给出了VC5402 HPI寄存器访问控制的情况。PCI2040带有独立的读/写选通信号HDS和HR/W,可以将PCI2040的HDS、HR/W引脚与VC5402的HDSl、HR/W引脚相连,实现主机对VC5402 HPI接口的读/写控制。当主机驱动HR/W为高时,读HPI;为低时,则写HPI。DSP HPI口的HPIEA、HDS2、HAS引脚通过10kΩ电阻拉高。

需要注意的是,VC5402的HPI接几是8位的,而DSP内部和PCI总线上的数据格式都是大于8位的,所以主机与DSP之间数据传输必须包含2个连续的字节。专用的HBIL引脚信号确定传输的是第一个字节还是第二个字节;HPI控制寄存器HPIC的BOB位决定第一个或第二个字节放置在16位字的高8位。

3 电路设计时应注意的问题

①VC5402电源采用3.3V和1.8V电源供电。其中:I/O采用3.3V;核电压采用1.8V供电;系统从PCI插槽取5V电压经

电压转换后,供DSP和其他芯片使用。

②VC5402的有些引脚必须接4.7kΩ的上拉电阻,没有用到的中断引脚也要接相同的上拉电阻。

③电源输入端跨接一个10~100μF的电解电容器,为每个集成屯路芯片配置一个0.01μF的陶瓷电容器。

结语

实践证明,利用PCI2040芯片实现C54x/C6x DSP的PCI总线可以大大减少相应的外围器件,增强系统的可靠性,同时降低系统开发的难度,缩短开发周期。

四、TMS320C32的存储器接口设计

1 TMS320C32的外部存储器接口的特点

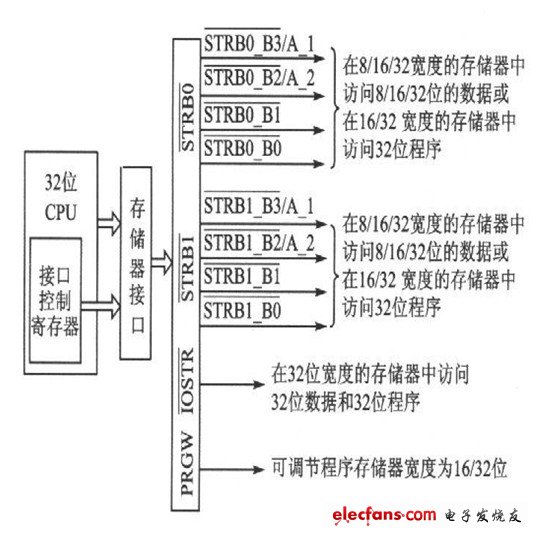

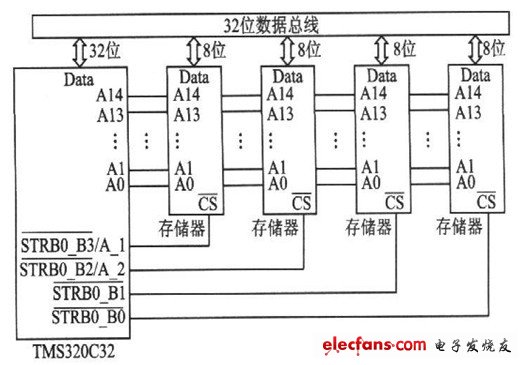

TMS320C32是一个32位微处理器,它可以通过24位地址总线、32位数据总线和选通信号对外部存储器进行访问。其外部存储器接口结构如下图l所示。

图1,TMS320C32的外部存储器接口图

在图1中,引脚(引脚,又叫管脚,英文叫Pin。就是从集成电路(芯片)内部电路引出与外围电路的接线,所有的引脚就构成了这块芯片的接口)PRGW是用来配置外部程序存储器的宽度的。当PRGW引脚为低电平时程序存储器宽度为16位;当PRGW引脚为高电平时程序存储器宽度为32位。STRBO和STRBl各为一组访问外部存储器的选通信号,各有4个信号引脚(STRBx_B3/A_1、STRBx_B2/A_2、STRBx_Bl和STRBx_B0)。从图l中我们可以看出,选通信号STRB0和STRBl能从8/16/32位存储器中访问8/16/32位数据,或从16/32位存储器中执行32位程序;IOSTRB是外设I/O的选通信号引脚,它只能从32位宽度的存储器中访问32位的数据和程序。

可以通过对STRBx和IOSTRB的设置,从8/16/32位的存储器中访问8/16/32位数据或程序。也就是说,可以从任何一个外部存储器中访问任何一种类型的数据。这就说明可以通过设置IOSTRB、STRB0和STRB1的选通信号来寻址整个外部存储器空间。例如,一个32位外部存储器可以被设定为只存放一个32位的双字,但是也可以被分为具有2个连续地址的16位字或者4个连续地址的8位字节。反之,一个32位双字可以放在一个32位外部存储器中,也可以放在2个16位或4个8位宽度的外部存储器中。

TMS320C32内部总共提供了64 MB的存储器映射空间。其中,STRB0所对应的存储映像区间是不连续的两段区问,一段是03FH~7FFFFFH(共31.999 MB),另一段是880000H~8FFFFFH(共2 MB);STRBl所对应的存储映像区间是900000H~FFFFFFH(共28 MB);IOSTRB所对应的存储映像区间是810000H~82FFFFH(共512KB)。当外部总线访问这些空间时,相应的选通信号就使能。

负责控制信号的输入和输出叫做使能,是一个动词,英文‘Enable’。使能通俗点说就是一个“允许”信号,进给使能也就是允许进给的信号,也就是说当进给使能信号有效的时候电机才能转动。一般的数控系统会将电机的进给使能信号跟急停开关和行程限位开关串联起来,当按下急停开关或者电机运转超出行程后,进给使能信号被断开,电机不能继续转动,从而保护机床在安全的行程内运行。

2 TMS320C32的3种存储器设计方案

2.1 8位存储器宽度

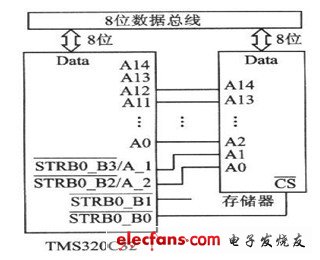

设计为8位的存储器,其硬件接线方案如图2所示。STRBx_B3/Al_1和STRBx_B2/A_2引脚作为地址引脚,STRBx_B0引脚作为片选引脚,而STRBx_B1则不用。

图2,8位存储器的硬件接线图

图3,16位存储器的硬件接线图

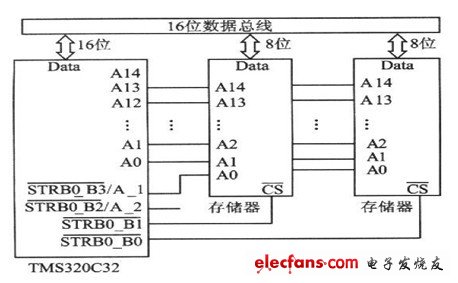

设计为16位的存储器,其硬件接线方案如图3所示。STRBx_B3/A_1引脚作为地址引脚,STRBx_B0和STRBx_B1引脚作为片选引脚,而STRBx_B2/A_2则不用。

2.3 32位存储器宽度

设计为32位的存储器,其硬件接线方案如下图4所示。STRBx所有的引脚都设置成片选引脚。

图4,32位存储器的硬件接线图

3 存储器映射外部总线控制寄存器

综上所述,TMS320C32可以从8/16/32位存储器中访问8/16/32位数据,或者从16/32位存储器中执行32位的程序。但是如果内外部数据的位数不一致时该如何处理呢?C32的外部总线控制寄存器可以根据相应控制位的值,自动对存储器接口的宽度进行相应的调整。下面则对总线控制寄存器作出一个详细的介绍。

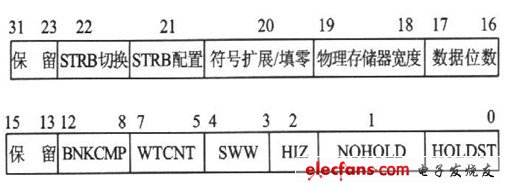

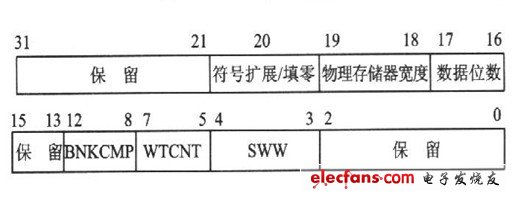

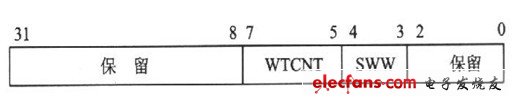

STRBo、STRBl以及IOSTRB控制寄存器在存储器映射空间的物理地址分别是808064H、808068H和808060H,并且都是32位的,各位的定义如图5、图6和图7所示。

图5,STRBo控制寄存器

图6,STRBl控制寄存器

图7,IOSTRB控制寄存器

从图5和图6中我们可以看到,STRBx控制寄存器的第18、19位是用来控制存储器的宽度的,而第16、17位是用来控制数据宽度的,具体定义如表1所列。

4 存储器接口实例

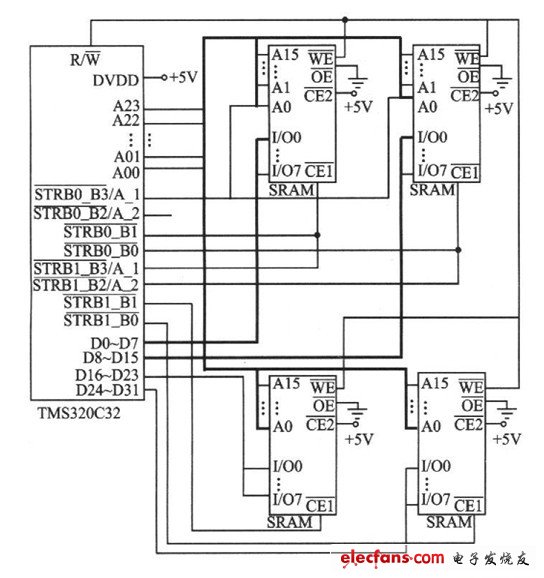

图8给出了一个实际TMS320C32存储嚣接口的电路图。16位存储器由2片128 K8位的SRAM构成,32位存储器由4片128 K8位的SRAM构成,STRB0的4组选通信号接16位外部存储器,STRBl的4组选通信号接32位外部存储器。为说明数据在存储器及处理器中的存放格式,本文设计了两种存储器接口电路:一是在16位存储器中存放32位数据;二是在32位存储器中存放32位数据。

图8,TMS320C32存储嚣接口的电路图

在16位存储器中存放32位数据时,STRB0_B3/A1作为地址引脚与外部存储器的AO相接,STRB0_B0和STRB0_B1作为片选信号,STRBx_B2/A_2不用。由于数据宽度大于存储器宽度,所以在外部存储器偶地址中存放32位数据的低16位,奇地址中存放32位数据的高16位,外部存储器的地址为OH~lFFFFH,对应的在C32存储映射中的地址为OH~0FFFFH。当一条指令向逻辑地址OH中装入一个32位数据时,存储器接口必须向外部16位存储器执行两个指令周期。这两个指令周期访问2个连续的外部存储器地址OH和1H,从而完成对32位数据的操作。

当在外部32位存储器中存放32位数据时,STRBl的4个引脚都设置为片选引脚。这时数据宽度与外部存储器宽度一致,由于是STRBl使能,所以128 K32位的外部存储空间与C32存储器映射的900000H~91FFFFH相对应。

当接口电路设计为16位时,其物理地址等于逻辑地址右移l位,即DSP的地址线A00接在SRAM的A1上;当接口电路设计为32位时,其物理地址等于逻辑地址,即DSP的地址线A00接在SRAM的A0上。

5 小结

由于C32可以非常灵活地调整其存储器接口宽度,使得存储器接口电路的设计更加的灵活,因此非常适用于电机或电力系统等实时系统的数据采集与处理。

全部0条评论

快来发表一下你的评论吧 !