深入探索Vivado非工程模式FPGA设计流程

可编程逻辑

描述

参考:UG892 UG835

Vivado集成开发工具为设计者提供了非工程模式下的FPGA设计流程。在Vivado非工程模式下,FPGA开发人员可以更加灵活地对设计过程的每个阶段进行控制,从而进一步提高FPGA的设计效率。

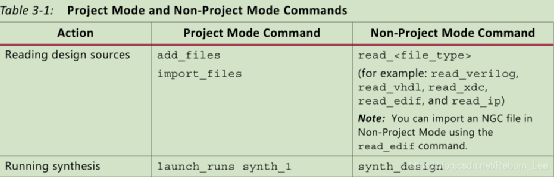

非工程模式下基本命令列表

| 命令 | 功能 |

| read_edif | 将EDIF或者NGC网表导入当前工程的设计源文件集合中 |

| read_verilog | 读入用于非工程模式会话的Verilog(.v)和SystemVerilog(.sv)源文件 |

| read_vhdl | 读入用于非工程模式会话的VHDL(.vhd或vhdl)源文件 |

| read_ip | 读入用于非工程模式会话的已经存在的IP(.xco或者.xci)工程文件。使用来自.xco IP工程的.ngc网表。对于.xci IP,使用RTL用于编译;或者如果存在网表,则使用网表 |

| read_xdc | 读入用于非工程模式会话的.sdc或者.xdc文件 |

| set_param set_property | 用于多个目的。例如,它可以定义设计配置和工具设置等 |

| link_design | 如果会话中使用网表文件,则对设计进行编译,用于综合目的 |

| synth_design | 启动Vivado综合,包含设计的顶层模块名字和目标器件参数 |

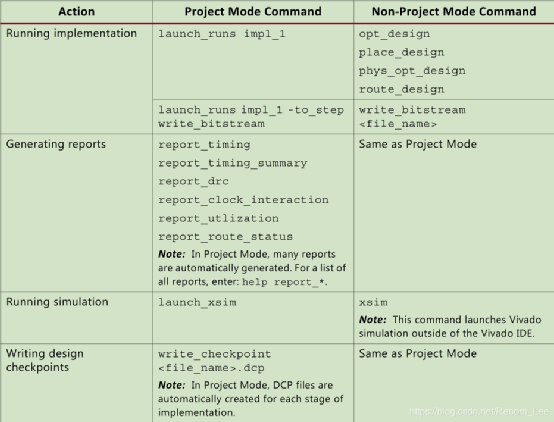

| opt_design | 执行高层次设计优化 |

| power_opt_design | 执行智能时钟门控,用于降低系统的整体功耗(可选) |

| place_design | 对设计进行布局 |

| phys_opt_design | 执行物理逻辑优化,以改善时序和布线能力(可选) |

| route_design | 对设计进行布线 |

| report* | 运行多个标准的报告,可以在设计过程的任何一个阶段运行它 |

| write_bitstream | 生成一个比特流文件,并且运行DRC |

| write_checkpoint read_checkpoint | 在设计流程的任何点保存设计。一个设计检査点由网表和约束构成,它们在设计流程的该点进行了优化,以及包含实现的结果 |

| start_gui stop_gui | 调用在存储器中当前设计的Vivado集成开发环境 |

典型TCL脚本

为了方便读者从整体上了解在Vivado非工程模式下的基本命令的功能,下面将给出用于Vivado设计套件示例的非工程模式TCL脚本,该脚本可以说明使用设计检查点、用于保存设计流程中各个阶段的数据库状态和手工生成各种报告的方法。

通过下面的命令运行该Tcl脚本文件:

vivado -mode tcl –source create_bft_batch.tcl

|

Following is an example of a Non-Project Mode script, which reads in various source files: # create_bft_batch.tcl # bft sample design # A Vivado script that demonstrates a very simple RTL-to-bitstream batch flow # # NOTE: typical usage would be "vivado -mode tcl -source create_bft_batch.tcl" # # STEP#0: define output directory area. # set outputDir ./Tutorial_Created_Data/bft_output file mkdir $outputDir # # STEP#1: setup design sources and constraints # read_vhdl -library bftLib [ glob ./Sources/hdl/bftLib/*.vhdl ] read_vhdl ./Sources/hdl/bft.vhdl read_verilog [ glob ./Sources/hdl/*.v ] read_xdc ./Sources/bft_full.xdc # # STEP#2: run synthesis, report utilization and timing estimates, write checkpoint design # synth_design -top bft -part xc7k70tfbg484-2 -flatten rebuilt write_checkpoint -force $outputDir/post_synth report_timing_summary -file $outputDir/post_synth_timing_summary.rpt report_power -file $outputDir/post_synth_power.rpt # # STEP#3: run placement and logic optimzation, report utilization and timing estimates, write checkpoint design # opt_design place_design phys_opt_design write_checkpoint -force $outputDir/post_place report_timing_summary -file $outputDir/post_place_timing_summary.rpt # # STEP#4: run router, report actual utilization and timing, write checkpoint design, run drc, write verilog and xdc out # route_design write_checkpoint -force $outputDir/post_route report_timing_summary -file $outputDir/post_route_timing_summary.rpt report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt report_clock_utilization -file $outputDir/clock_util.rpt report_utilization -file $outputDir/post_route_util.rpt report_power -file $outputDir/post_route_power.rpt report_drc -file $outputDir/post_imp_drc.rpt write_verilog -force $outputDir/bft_impl_netlist.v write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc # # STEP#5: generate a bitstream # write_bitstream -force $outputDir/bft.bit |

Vivado集成开发环境分析

3.1 启 动 Vivado集 成 开 发 环 境

当工作在非工程模式时,对于存储器中活动的设计来说,使用下面的命令打开/关闭Vivado集成开发环境。

(l)start_gui,打开Vivado集成开发环境,用于存储器中活动的设计。

(2)stop_gui,关闭Vivado集成开发环境,并且返回“Vivado Design Suite Tcl shell”界面。

在设计过程的每个阶段,设计者均可以打开Vivado集成开发环境,对存储器中保存的当前设计进行分析和操作。在非工程模式下,在Vivado集成开发环境中,一些工程的特性是不可用的,如Flow Navigator、Project Summary,以及源文件的访问、管理和运行。然而,通过Vivado集成开发环境的Tools菜单,可以使用分析及修改约束等很多特性。

需要知道的是,在Vivado集成开发环境中,对存储器中的设计所做的任何变化都会自动应用到下游工具中,这里没有保存的功能。如果设计者想要将约束的变化用于后续的运行,则在Vivado集成幵发的环境的主菜单下,执行菜单命令【File】—【Export】—【Export Constraints】,写到一个新的包含所有XDC文件的文件中。

3.2 打开设计检查点的方法

通过Vivado集成设计环境,设计者可以在保存的设计点上对设计进行分析。通过使用Tcl命令(synth_design、opt_design、power_opt_design、place_design、phys_opt_design和route_deSign),设计者可以在非工程模式下运行一个设计,并且可以在任何阶段保存一个设计。这样,就可以在Vivado集成设计环境中读取设计。设计者可以从一个布线后的设计开始,分析时序,仅通过布局来解决时序问题。然后保存刚才的工作,甚至设计中还没有进行的布线操作。Vivado集成设计环境显示打开设计点的名字。 设计者可以打开、分析和保存设计检查点,也可以将变化保存到新的设计点。

(1)在Vivado集成开发环境下,执行菜单命令【File】->【Save Checkpoint】,保存对当前设计检查点的修改。

(2)在Vivado集成开发环境下,执行菜单命令【File】—【Write Checkpoint】,将设计检查点的当前状态保存到一个新的设计检查点中。

关于具体的每个命令的使用下一节将细致分析。

审核编辑:黄飞

-

Vivado工程模式和非工程模式的比较2020-11-09 6029

-

在Vivado图形化界面IDE中运行和调试Tcl命令2022-06-17 3208

-

用 TCL 定制 Vivado 设计实现流程2023-06-28 6139

-

液晶电视工程模式2012-05-14 22598

-

Vivado设计之Tcl定制化的实现流程2017-11-18 4243

-

降低布线延迟的另一流程2018-11-07 6174

-

用Tcl定制Vivado设计流程详解2019-07-24 5617

-

浅析Vivado在非工程模式下的FPGA设计流程2021-06-19 3766

-

【FPGA Vivado】基于 FPGA Vivado 的流水灯样例设计2021-12-04 994

-

FPGA便捷开发-TCL商店(开源)2022-04-07 6659

-

关于Vivado non-project模式2022-10-17 4882

-

vivado创建工程流程2023-07-12 4072

-

vivado主界面及设计流程2023-09-17 5134

-

详解Vivado非工程模式的精细设计过程2024-04-03 3420

-

如何在AMD Vivado™ Design Tool中用工程模式使用DFX流程?2024-04-17 2547

全部0条评论

快来发表一下你的评论吧 !