一文解析NAND的闪存接口ONFI

存储技术

描述

从3月21号发布的文章《 NAND 存储简介》里我们知道, 从 SD 卡、手机、平板等消费级产品到数据中心企业级场景,NAND Flash 凭借其高性能、大容量、低功耗以及低成本等特性大受欢迎,是目前应用最为广泛的半导体非易失存储介质。接下来我们看一看 NAND 的闪存接口 ONFI。

定义

ONFI,全称为 Open NAND Flash Interface,即开放式 NAND 闪存接口,是一种协议,其定义了 NAND Flash 存储器和控制器之间的通信接口规范。该协议规定了一系列命令和数据传输格式,使得控制器能够与 NAND Flash 存储器进行有效通信,执行读取、写入、擦除等操作。

ONFI 由100多家制造、设计或使用 NAND 闪存的公司组成的行业工作组,其中包括主要成员如 Intel 和镁光。该工作组旨在简化将 NAND 闪存集成到消费电子产品、计算平台以及其他需要大容量固态存储的应用程序中的过程。为此,他们制定了标准化的组件级接口规范、连接器和模块外形规格。

规范

ONFI 规范涵盖了以下关键方面:

1 电气接口:定义了 NAND 闪存芯片与控制器之间的电压级别、信号时序和信号协议。

2 命令集:规定了控制器用于访问和控制NAND 闪存芯片的命令和命令序列,包括读取、写入、擦除等操作

3 数据传输模式:描述了接口支持的各种数据传输模式,如同步和异步数据传输、多平面操作和多通道访问等。

4 时序参数:指定了时序特性,包括设置和保持时间、最大时钟频率和其他时序约束,以确保可靠的数据传输。

趋势

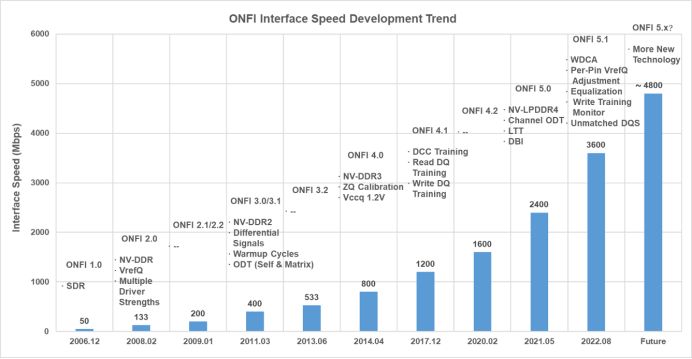

通过采用开放接口标准,ONFI 加强了来自不同供应商的 NAND 设备之间的兼容性和互操作性。这一举措增加了标准设备的供应基础,缩短了产品设计时间,并加速了产品上市时间。自2006年12月发布第一个 ONFI 协议以来,ONFI 组织已经发布了数十个版本,其中接口速率从最初的 50Mbps 不断发展,目前已达到 3600Mbps 。下图展示了 ONFI 协议接口演进的趋势。

技术与挑战

如今,ONFI 已经发展到了 ONFI 5.x,ONFI 5.x 推出了 NV-LPDDR4 技术,将接口速率从 ONFI 5.0 的 2400Mbps 提升至 ONFI 5.1 的 3600Mbps。为了克服高速接口带来的信号完整性挑战,除了加强写校准和 VrefQ 校准外,ONFI 5.x 还引入了非对称 DQS 设计和自适应均衡器设计。DFE(Decision Feedback Equalizer,判决反馈均衡器)技术利用上次信道输出的判断加权反馈到输入,有助于消除码后干扰。另外,尽管 NV-DDR3 和 NV-LPDDR4 支持的最大接口速率相同,但 NV-LPDDR4 采用 LTT 技术可显著降低读操作功耗。

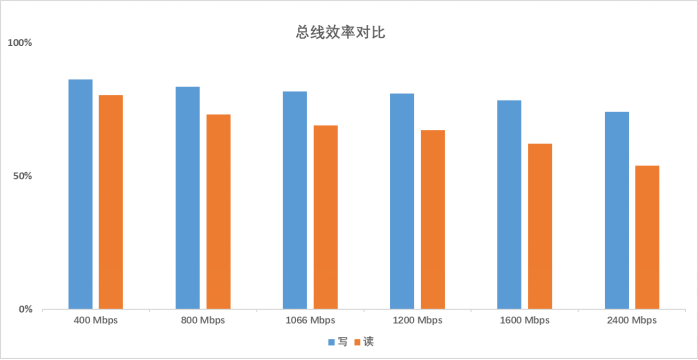

自 ONFI 1.0 到 ONFI 5.1,接口速率经历了快速发展,但命令、地址和数据传输形式基本保持不变。尽管总线速率提高,改善了数据传输时延,但命令和地址传输时延未见改善,导致系统总线利用效率不断下降。在下图中,我们以乐观的场景比较了写/读场景的总线效率,发现读和写的总线效率均逐渐下降,特别是读场景下降至约50%时,进一步增加了系统设计的挑战。

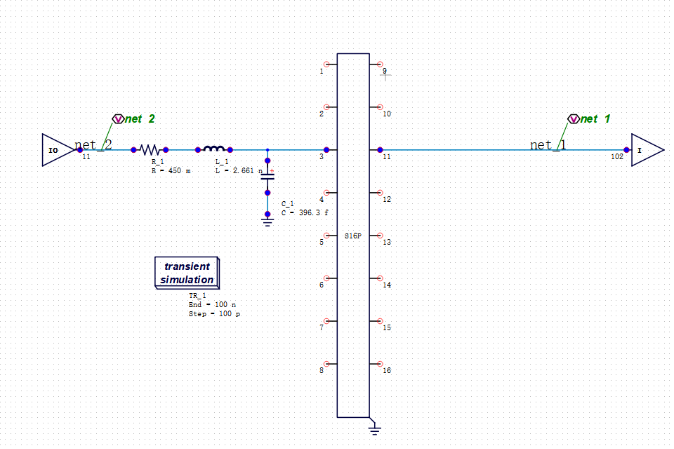

在巨霖 SIDesigner 仿真平台中,通过设置控制端和 NAND 端的 IBIS 文件和中间的 S 参数,即可以完成使用了 ONFI 协议的 NAND Flash 仿真。

审核编辑:黄飞

-

如何突破AI存储墙?深度解析ONFI 6.0高速接口与Chiplet解耦架构2026-01-29 460

-

国产高性能ONFI IP解决方案全解析2026-01-13 462

-

开放式NAND闪存接口规范onfi5.0协议2024-05-15 1564

-

开放NAND闪存接口ONFI介绍2023-06-21 14632

-

开放式NAND闪存接口规范说明书2022-12-13 564

-

开放式NAND闪存接口规范2022-09-09 666

-

Arasan推出NAND闪存全IP解决方案2021-08-05 2889

-

NAND闪存芯片有哪些类型2020-09-18 8782

-

解析NAND闪存和NOR闪存2020-07-30 16962

-

如何采用Virtex 4的SLC NAND闪存2020-06-17 1983

-

满足ONFI2.1标准要求的NANDFlash控制器的设计及仿真研究2020-04-18 4006

-

闪存的接口协议的介绍和不同协议之间有什么区别2020-04-02 3868

-

泰克推出业内第一个ONFI闪存标准测试解决方案2016-12-12 3125

-

NAND闪存深入解析2012-08-09 2677

全部0条评论

快来发表一下你的评论吧 !