Efinity Interface Designer报错案例-v2

Efinity Interface Designer报错案例-v2

描述

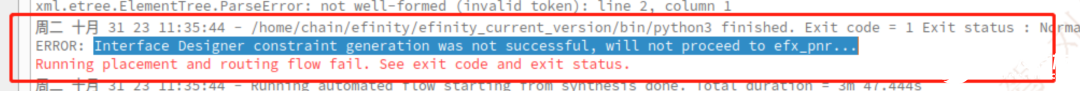

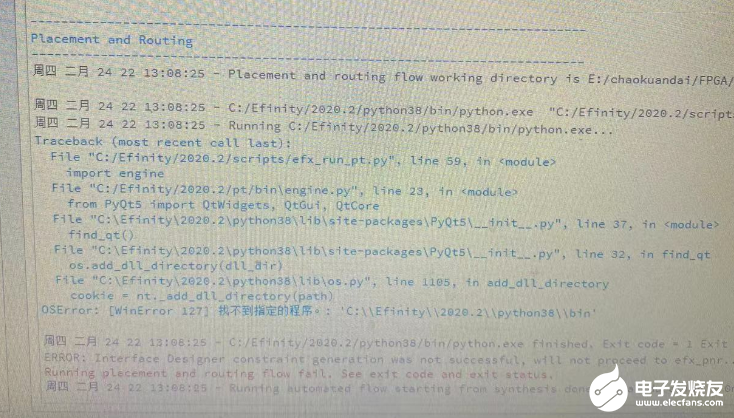

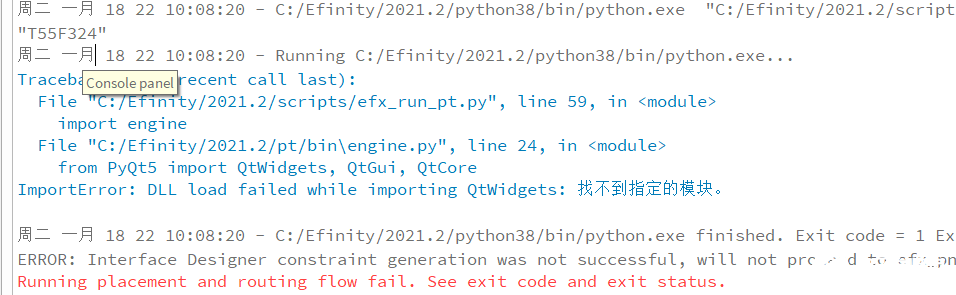

(1)ERROR:Interface Designer constraint generation was not successfull,will not proceed to efx_pnr...

原因:(1)有些客户使用Win7版本,目前Efinity对Win7的支持不好。建议升级成win10。

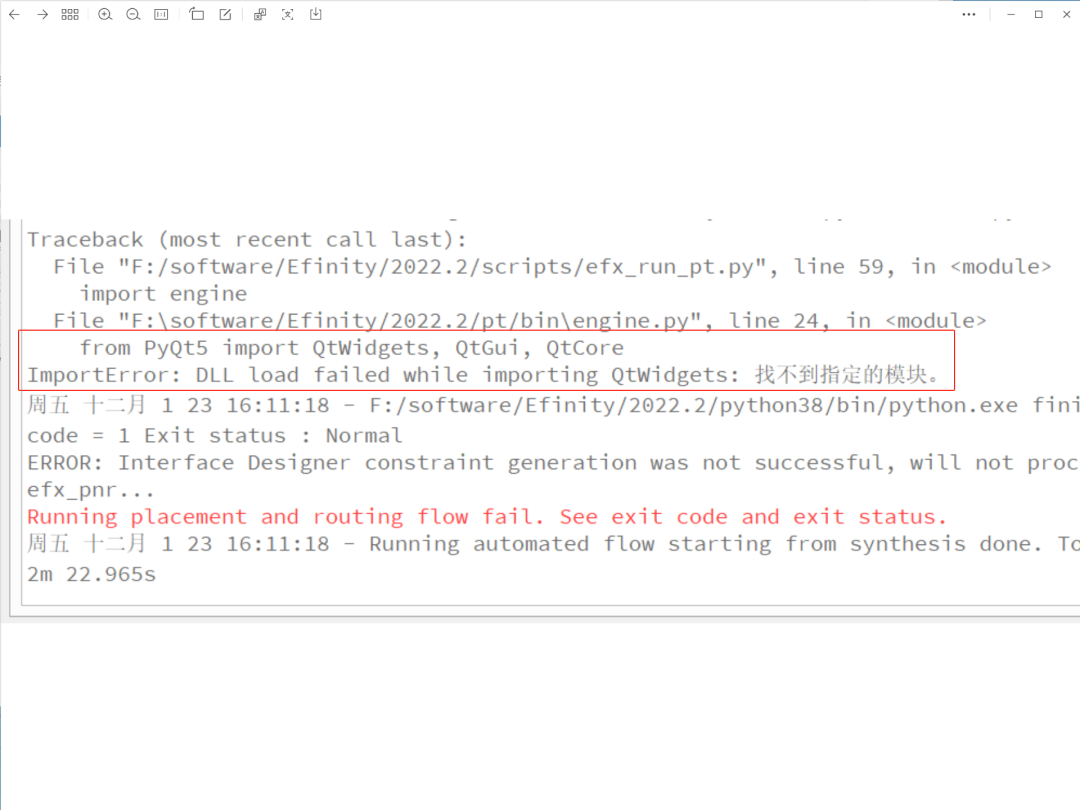

(2)杀毒软件删除了文件,实际interface生成约束是没有问题的,客户pnr的时候就报错,需要重新安装软件。

(3)电脑存在加密系统 。造成的现象是新建工程时interface可以打开,但是生成xxx.peri.xml文件之后再次打开就会报错。

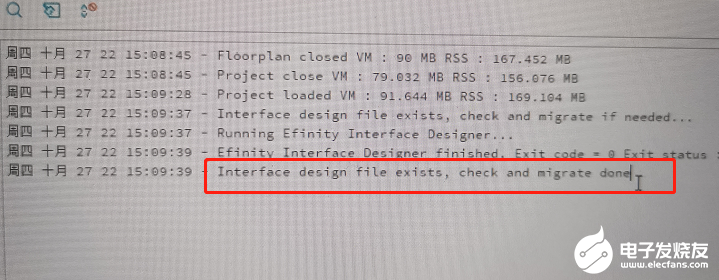

(2)Interface打不开。

现象:(1)打开interface的时候指示:Efinity Interface Designer finished. Exit code = 1 Exit status : NormalInterface design file exists, check and migrate done (2)新建工程第一次可以打开interface Designer(3)删除xxx.peri.xml之后,第一次也可以打开Interface Designer.原因:电脑存在加密

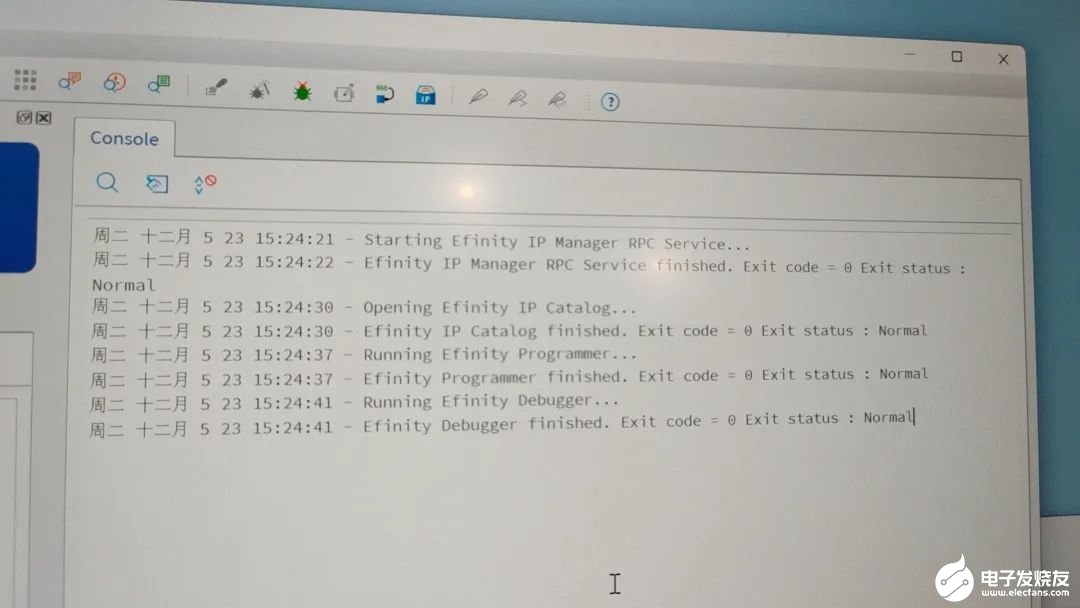

(3) interface打不开打开interface Designer时会报以下错误。Efinity IP Catalog finished.Exit code = 0 Exit status:Normal

(2)新建工程第一次可以打开interface Designer(3)删除xxx.peri.xml之后,第一次也可以打开Interface Designer.原因:电脑存在加密

(3) interface打不开打开interface Designer时会报以下错误。Efinity IP Catalog finished.Exit code = 0 Exit status:Normal

编译过程可能报以下错误:

ERROR: Interface Designer constraint generation was not successful, will not process pnr..

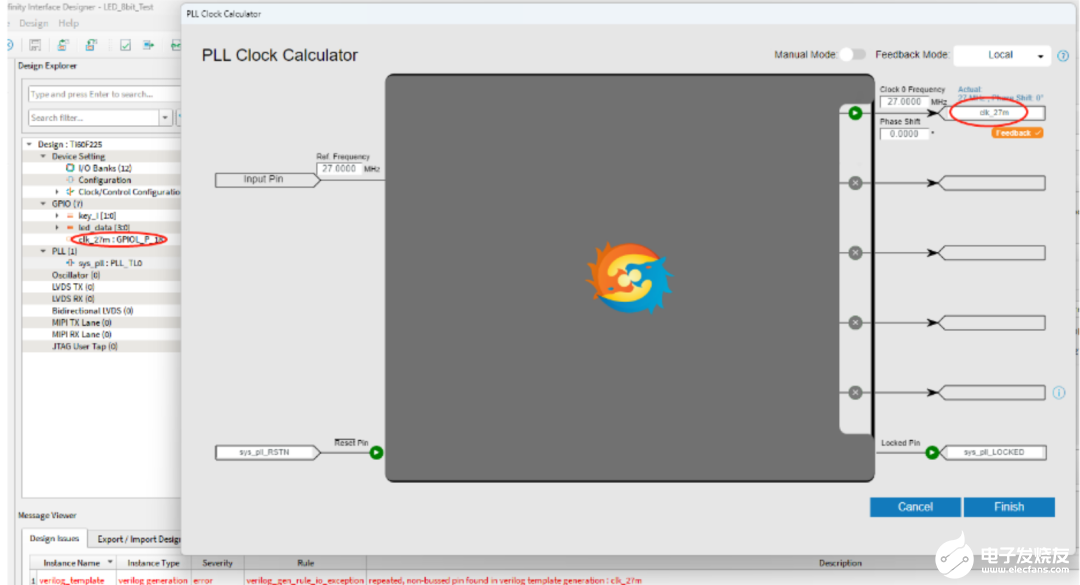

(4)repeated,non-bussed pin found in verilog template generation:clk_27m

说明:在GPIO处定义了一个clk_27m,在pll的输出上又定义了一个clk_27m,两个信号名冲突。

(5)ERROR: Interface Designer constraint generation was not successful, will not process pnr..

原因:1)一般是软件有360或者别的杀毒软件的相关文件删除了,需要找回文件或者重新安装软件。

2)客户使用Win7版本,目前Efinity对Win7的支持不好。建议升级成win10。

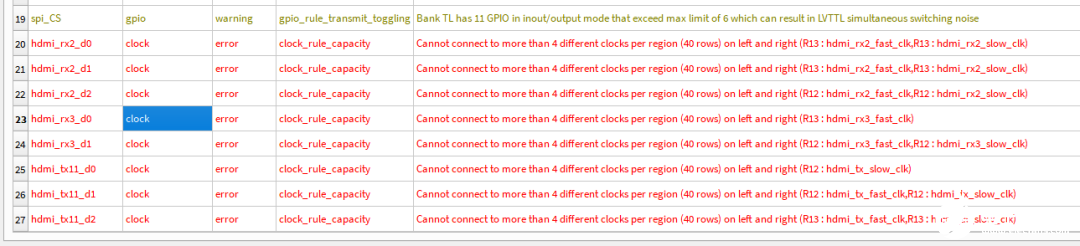

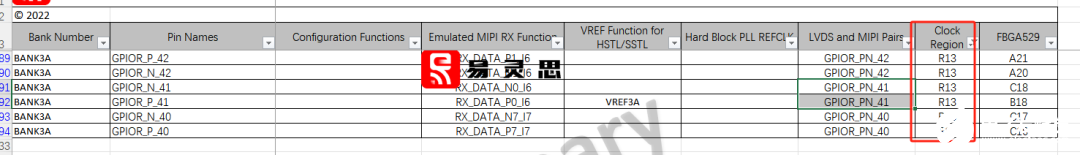

(6)cannot connect to more than 4 different clocks per region on left and right

原因是在pinout文件中对应的Clock Region中,不能超过4个时钟去驱动。

-

也就是GPIOR_PN_42,41,40三组差分对,不能由两组LVDS来驱动,因为每组LVDS时钟有lvds_fast_clk和lvds_slow_clk两个,两组就会有4个时钟在Region clock R13区域。

-

结论就是把LVDS差分对放在同一个Clock Region.

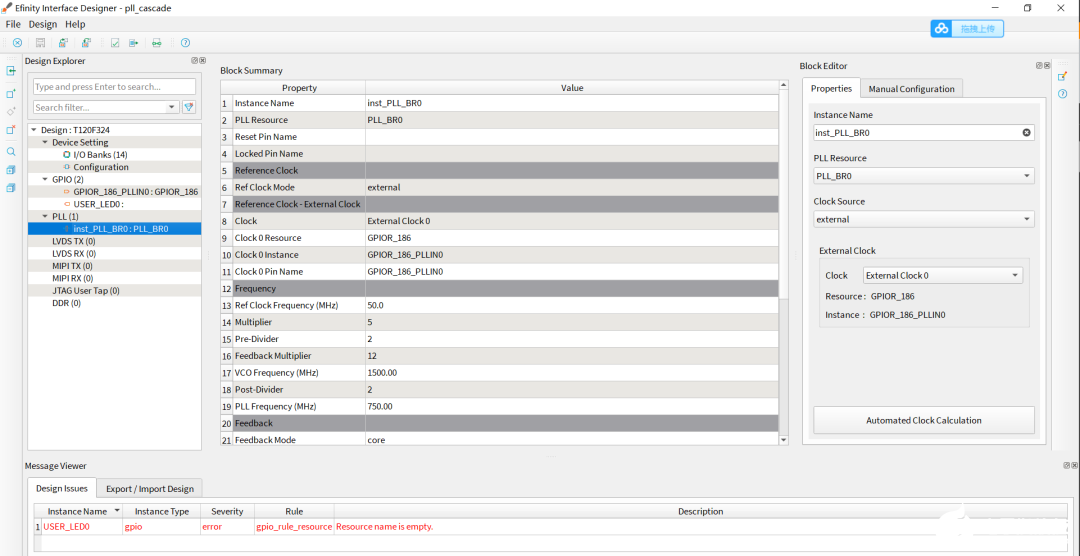

(7)Resource name is empty

解决方案:Resource是指管脚,这里是指没有分配管脚。

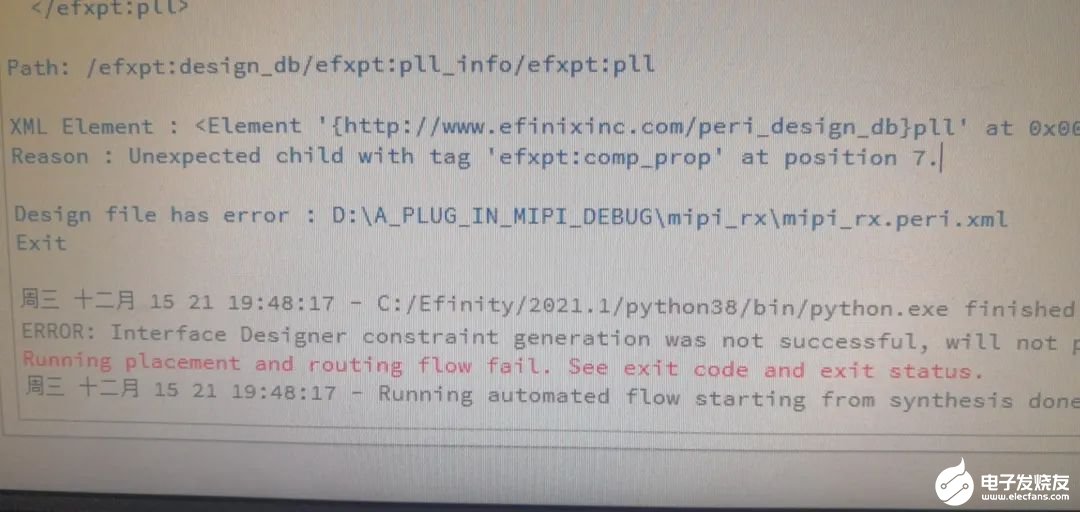

(8)用新版本软件打开老版本工程时interface Desinger打不开

发给客户的peri.xml,客户打不开有问题,叫他们文本打开peri看看,有些客户没有动peri文件,但是内容却改了

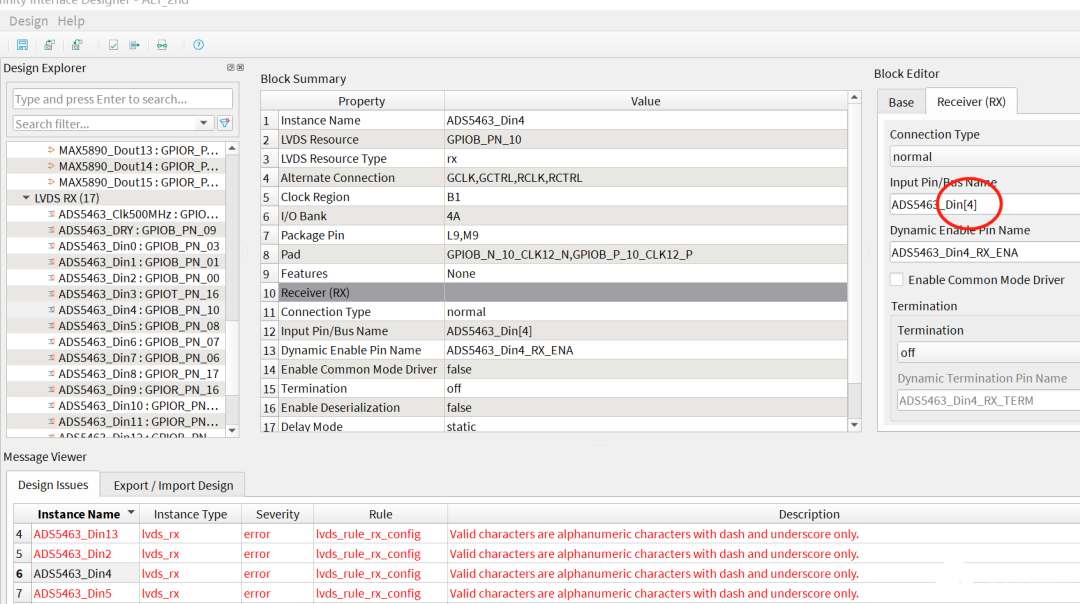

(9) Valid characters are alphanumeric haracters with dash and underscore only

原因:在LVDS添加Block时不能添加bus,所以在Input Pin/Bus Name中命名上不能像总线一样添加[*]

(10)interface Designer打不开定位思路。

原因:查一下下面几点:

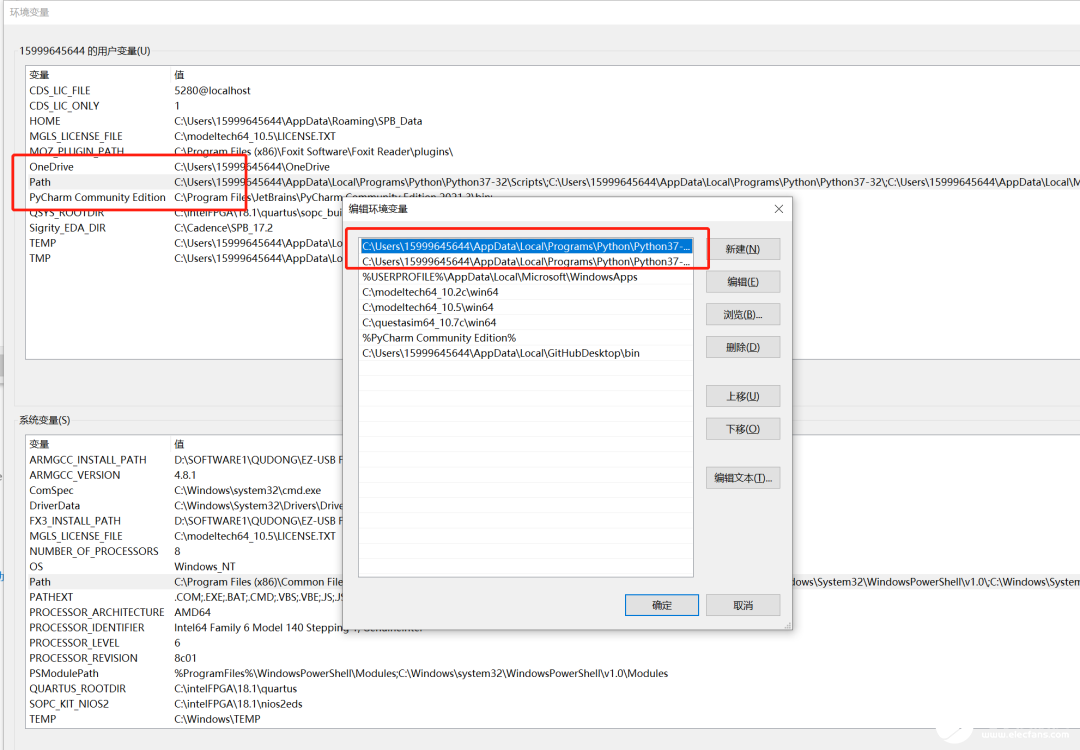

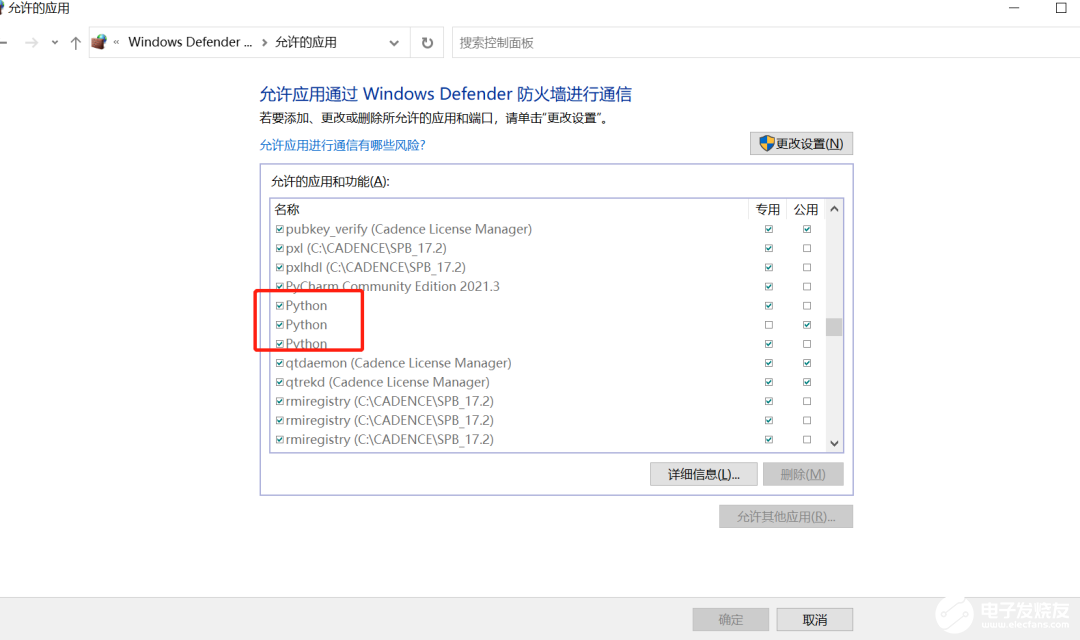

1. 系统环境路径设置

2. python是否在firewall 允许的程序列表里

3. microsoft visual c++2015有安装吗?

这个有一个安装包,在打不开的时候可以安装

4. java 8有安装吗?

(11)烧写文件无法生成Using source file "D:/customer_Prj/googol/phy_jtag_bridge/work_pnr/spi_flash_loader.lbf"Missing Interface Designer LPF constraint file, no programming file will be generated.Open Interface Designer to create a project.原因:如果在interface Desinger中没有添加接口是不会生成bit文件的。

(12)These HSIO GPlO must be placed at least 1 pair away from Mipl lane csi_rxc in order to avoid noise coupling from GPIO to MIPI Lane: GPIOR_ N_09,GPIOR_P 09

这个是一告警信息,意思是说差分信号要和单端信号之间隔开一组差分对。比如上面的警告,说的是GPIOR_PN_09这个差分对和要单端信号之间隔开一组差分对,也就是GPIOR_PN_08或者GPIOR_PN_10要空着不能接信号。当然如果放一些很低速的信号也是可以的比如复位信号,上电之后一般不再翻转,或者UART这样速率比较低的信号。

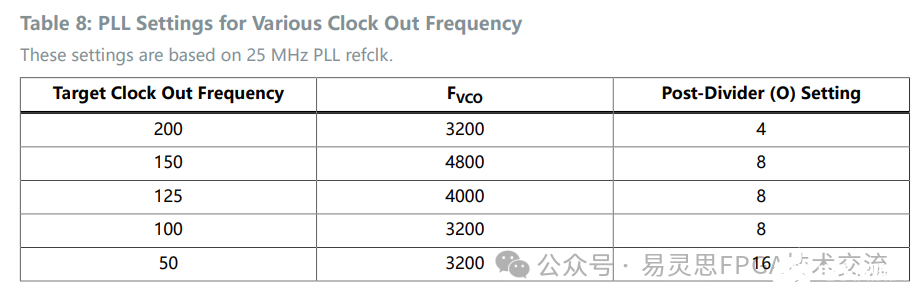

(13)The recommended phase shit step for the Calibration Clock is 45 degrees, Curent: 15.0000 degrees.

在使用hyperram时,对fpll的频率是有要求的。请具体参考以下格式对PLL的VCO频率和POST-divider参数进行设置。更详细的说明可以参考hyperram的datasheet或者本公众号关于hyperram的介绍。

- 相关推荐

- 热点推荐

- Interface

-

Efinity入门使用-v22024-11-06 2334

-

Efinity软件安装-v52024-11-01 2189

-

Efinity debuger常见问题总结-v22024-07-11 3465

-

Efinity Interface Designer报错案例-v12023-12-12 2659

-

Efinity版本更新可能遇到的问题及解决办法2023-02-14 1784

-

V2 控制器的操作原理2022-11-14 756

-

RTT studio添加串口V2报错怎么办2022-09-23 3945

-

RTT studio添加串口V2编译会报错是为什么?2022-05-05 2474

-

STM32与ST-LINK/V2报错怎么解决2022-02-18 1004

-

Kinect v2(Microsoft Kinect for Windows v2 )配置移动电源解决方案2022-01-05 986

-

STM32与ST-LINK/V2报错的解决方法(2)2021-12-23 1615

-

ST-LINK/V2 ST-LINK/V2ST-LINK / V2在调试器/编程器STM8和STM322020-05-21 1972

-

ST-Link/V2与HALT模式不兼容2018-10-30 2716

全部0条评论

快来发表一下你的评论吧 !