硅基光电子工艺中集成锗探测器的工艺挑战与解决方法简介

描述

锗(Ge)探测器是硅基光电子芯片中实现光电信号转化的核心器件。在硅基光电子芯片工艺中实现异质单片集成高性能Ge探测器工艺,是光模块等硅基光电子产品实现小体积、低成本和易制造的优先选择。硅基光电子芯片集成Ge探测器主要挑战在于热预算兼容、金属污染防控及工艺结构的匹配三个方面。

据麦姆斯咨询报道,联合微电子中心有限责任公司研究团队探讨了硅基光电子芯片集成Ge探测器在实际工艺中遇到的挑战和解决思路。相关研究内容以“硅基光电子工艺中集成锗探测器的工艺挑战与解决方法”为题发表在《数字技术与应用》期刊上。

硅光集成Ge探测器简介

数据中心内使用光纤通信以及由硅基光电子芯片封装的光收发器是一个非常有吸引力的选择,在短距离互连中可以显著降低收发器模块的功耗、成本和尺寸。硅基光电子芯片基于成熟的CMOS集成电路工艺技术、可在晶圆上大规模集成,成本低,产量大,且在重复性和良率上表现优异。同时依靠先进的封装技术及相关产业的基础条件,为大规模制造硅基光电子收发器模块提供了成熟的生产解决方案。

PIN光电探测器是硅基光电子芯片中的核心器件之一,其较PN节探测器多了一层I型本征层作为产生光电流的吸收光辐射区,从而实现小结电容,短渡越时间和高灵敏度。在高速光通信中,不仅依赖于芯片之间的通信,还需要实现芯片上组件之间的通信,然而,大多数信号处理,特别是数据存储仍然是以电信号的模式存在,这意味着实现光信号到电信号快速转换的PIN光电探测器在发射器和接收器上是必要的。

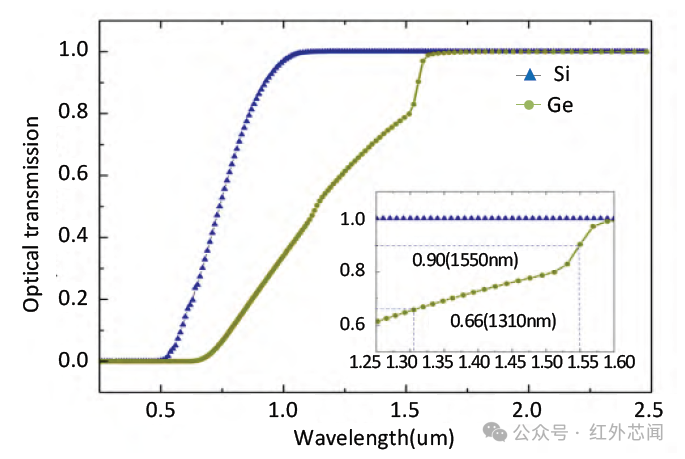

如图1所示,硅对1100 nm以上波长透明,在通信波段可以实现较低损耗的光信号传输,但不适合用于光电探测器制造。Ge的带隙为0.67 eV,同时是直接带隙,在近红外波段有着较高的吸收系数,是工作波长为1310 nm(O波段)和1550 nm(C波段)的光电探测器首选的吸收材料。Ge的光电探测器可在高频下工作,响应度高,同时Ge与硅基CMOS集成电路制造工艺兼容,被广泛用于光电探测器的制造。

图1 根据光学常数计算的厚度为500nm的Si和Ge的透光率

长期以来,硅基光电子以SOI(绝缘层上硅)为主要集成平台,利用该平台可实现高密度的多种硅光无源器件和有源器件集成。硅基光电子芯片集成Ge探测器同样是基于SOI平台,由于Ge熔点较其他半导体材料低,集成时首先就要解决其热预算兼容的问题。Ge选择性外延工艺温度较高,在金属段集成易造成污染,同时其为半金属,要避免与其他工艺的交叉污染,需要综合考虑金属污染防控问题。最后为了不影响其他器件设计及性能,工艺结构也必须匹配。

集成Ge探测器的工艺挑战与解决方法

热预算兼容

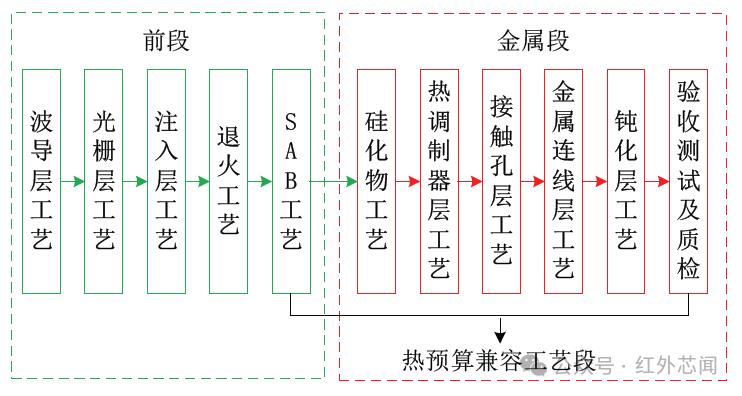

先进半导体工艺会对其热工艺制程进行严格的控制,以避免过多的热预算造成掺杂离子的过度扩散,从而导致器件性能退化或失效。在硅基光电子工艺中集成Ge探测器时,还需要考虑工艺对Ge材料的兼容问题。如图2所示,为了实现有源器件的电学功能,常规的注入工艺之后,需要对其掺杂离子进行退火激活,其典型的退火工艺温度约1000 ℃,但Ge的熔点仅有938 ℃,如果在注入退火工艺之前集成必然会造成Ge探测器熔化失效,Ge工艺必须在注入和退火工艺后进行。

但将Ge工艺整合在注入之后需要解决注入Si损伤问题。高能量剂量的注入会对Si造成损伤,导致Ge外延时产生大量缺陷甚至出现无法外延的情况。通过长时间的低温退火,或者生长一层薄的热氧然后通过稀氢氟酸清洗可以修复Si损伤,并获得高质量Ge器件。

图2 硅光工艺流程示意图

在另一方面,Ge外延同样是一个热过程,其会造成已注入离子的再次扩散,特别是离子半径小的元素,比如B,其扩散过程会更加剧烈,有导致有源器件性能退化的风险。降低Ge工艺温度可以避免掺杂离子的过度扩散,但会导致Ge器件中螺位错无法有效消除,这些位错是由于Ge和Si之间约4%的晶格失配引起,其会生成少数载流子,导致暗电流增加。Ge外延工艺温度需要综合考虑Ge探测器和其他有源器件的性能,寻找一个最佳平衡点。

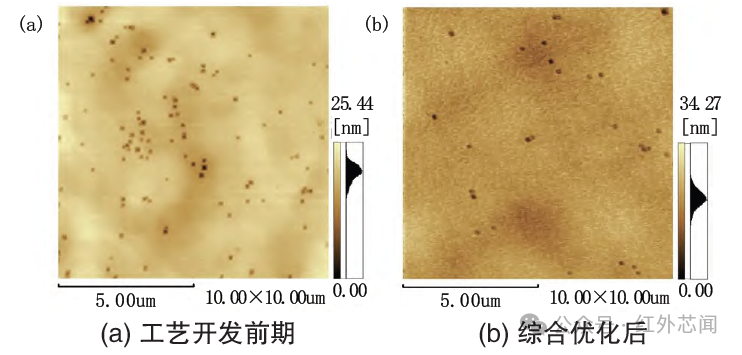

此外,综合考虑Ge外延工艺的热预算,提前对有源器件设计,注入工艺和掺杂离子选择做针对性的优化同样可以避免Ge探测器集成对其他有源器件的影响。如图3所示,通过原子力显微镜(AFM)表征了工艺开发前期及综合优化后Ge外延薄膜的位错分布,其位错密度由10⁸ /cm² 减少到10⁷ /cm²数量级,在保障其他器件性能的同时,有效地降低了Ge探测器中暗电流的产生。

图3 AFM下外延Ge中的位错分布

金属污染防控

金属污染对于半导体工艺是致命的,会造成可靠性和良率的降低,器件失效,甚至是给生产线带来不可逆转的损害。对于Ge探测器而言,金属离子扩散进入Ge晶格后,会形成缺陷,产生中间能级,导致探测器暗电流增大。将Ge探测器集成控制在金属材料相关工艺之前可以最大限度地避免金属段设备对Ge器件的污染。

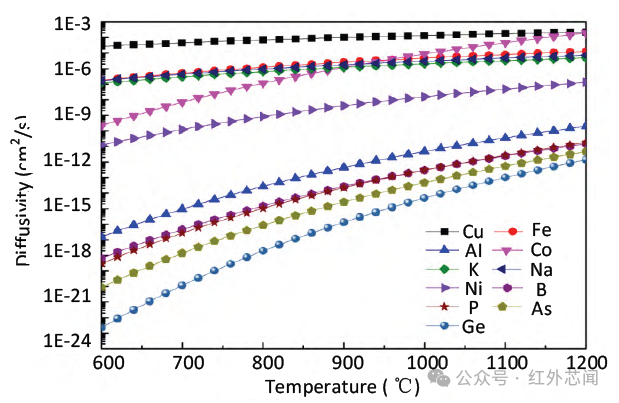

更重要的,Ge外延工艺是一个相对高温过程,超过金属Al的熔点,如果在金属Al工艺之后进行Ge集成,会造成器件失效,同时带来严重的设备交叉污染风险。此外,如图4所示,金属离子在晶圆中的扩散系数会随着温度呈指数变化,在高温过程中,作为降低接触电阻的金属硅化物元素,如:Co或Ni会扩散到硅光器件的各个位置,形成光吸收中心或者P-N节漏电流,从而进一步造成硅光器件光损耗异常甚至失效。

图4 不同元素扩散系数随温度变化曲线

工艺结构匹配

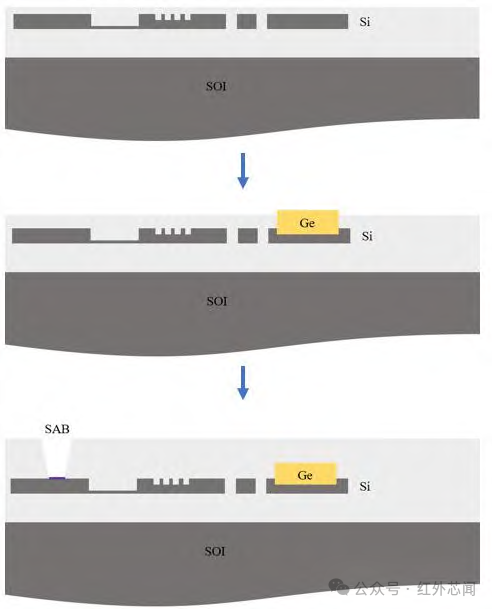

考虑到Ge探测器集成需要在完成离子注入退火后以及金属段之前,同时由于Ge是一种半金属,还要避免Ge的交叉污染,需要尽可能靠近金属段,综合考虑工艺架构匹配,将探测器集成与SAB(Salicide Block,自对准硅化物区域阻挡层)工艺段前为最优。首先可以通过SAB阻挡层将Ge探测器保护起来;其次SAB为最靠近金属段的光刻层,可以最大限度地避免Ge交叉污染。SAB主要用于降低接触孔和器件之间的接触电阻。如图5所示,在完成硅光前段工艺之后,SAB工艺之前,沉积一层氧化硅作为Ge外延生长的硬掩模,通过光刻和刻蚀将Ge器件图形转移到硬掩模上,这个过程中,为了器件性能的稳定性,对刻蚀深度的一致性有较高要求。

图5 硅基光电子芯片集成Ge探测器示意图

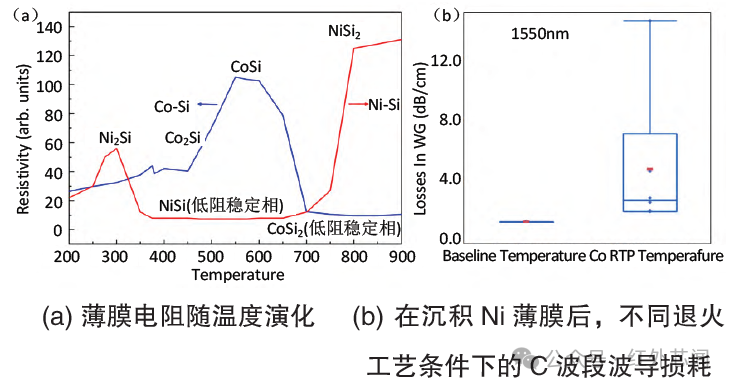

如图6(a)所示,为了进一步提升器件性能,通过采用工艺温度较低的镍的硅化物(NiSi,工艺温度约400℃)替代工艺温度较高的钴的硅化物(CoSi₂,工艺温度约800℃),来降低后续工艺温度对探测器的和其他硅光器件的影响。如图6(b)所示,采用Ni作为生成硅化物的金属,分别采用Ni和Co工艺的退火条件得到C波段的波导损耗,其中,Ni工艺退火条件的波导损耗在1.4 dB/cm左右,数据收敛;而Co工艺退火条件的波导损耗明显偏高,严重影响硅基光电子芯片性能。

图6 Ni-Si和Co-Si工艺对比

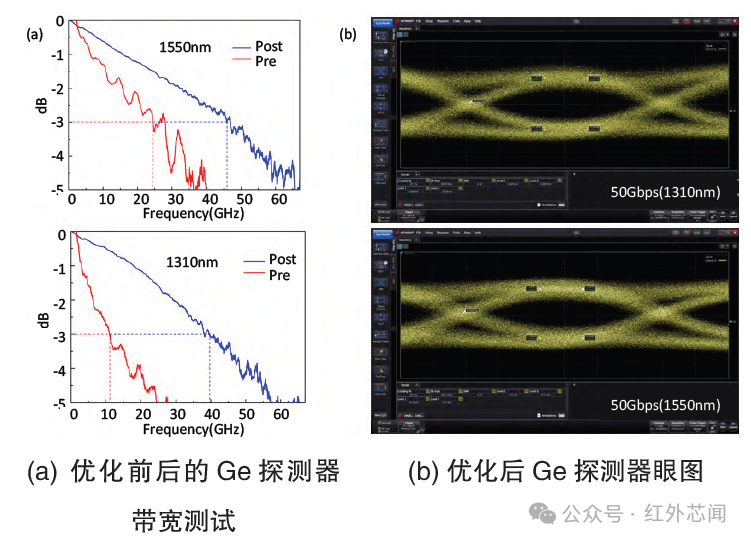

研究人员在CUMEC的中试线上开发了硅光SOI集成Ge探测器工艺,通过不断对Ge集成工艺和设计的迭代优化,实现了Ge探测器的工艺集成,其TEM(透射电子显微镜)截面图如图7所示,并对其器件性能进行了表征,其性能表现优异。图8展示了优化后Ge探测器性能提升。

图7 Ge探测器TEM截面图

图8 优化后Ge探测器性能

结语

全球各地的数据中心呈爆发式发展,硅基光电子芯片有望大幅降低其成本与功耗,其核心器件Ge探测器的集成主要面临三个方面的工艺挑战:热预算兼容、金属污染防控及工艺结构匹配,将探测器集成在SAB工艺段前是解决该挑战的关键。通过综合优化器件和工艺设计,寻找最佳Ge外延温度,并对其金属污染进行严格管控以及采用对硅光器件更为友好的Ni金属硅化物方案等,实现了高性能的Ge探测器的工艺集成。

论文信息:

DOI: 10.19695/j.cnki.cn12-1369.2023.08.46

审核编辑:刘清

-

单片光电子集成技术2011-11-15 3733

-

硅基光电子集成芯片2021-07-27 2774

-

光电子集成芯片2022-02-15 1571

-

光电探测器的主要噪声源及其成因2023-09-01 1347

-

集成光电智能探测器SOC研究2009-12-19 646

-

中国科学院近红外硅基光电探测器研究获进展2020-11-09 3331

-

半导体锗光电探测器与非晶硅基板上的非晶硅波导单体集成2021-12-24 2857

-

红外波段的硅基锗锡探测器2022-07-10 2047

-

垂直锗硅光电探测器完整的器件级多物理仿真2022-09-21 3006

-

基于硅光技术的光模块工艺2022-12-13 2124

-

混合硅基光电探测器的各项性能研究2023-04-23 3160

-

硅基锗PIN光电探测器的研究进展综述2024-04-25 4701

-

用于单片集成的硅基外延Ⅲ-Ⅴ族量子阱和量子点激光器研究2024-10-24 36478

-

新成果展示:发光-探测双功能AlGaN基集成光电子器件模型的开发与应用2025-03-03 952

-

聚智姑苏,共筑硅基光电子产业新篇 — “硅基光电子技术及应用”暑期学校圆满落幕!2025-07-11 1343

全部0条评论

快来发表一下你的评论吧 !