机器学习(ML)推理主要计算之存内计算芯片

人工智能

描述

01. 介绍

摘要:存内计算(CiM)已成为一种极具吸引力的解决方案,用于缓解冯-诺依曼体系结构中高昂的数据搬运成本。CiM 可以在内存中执行大规模并行通用矩阵乘法(GEMM)运算,这是机器学习(ML)推理中的主要计算。

然而,将存储器重新用于计算提出了以下关键问题:1)使用哪种类型的 CiM:鉴于模拟和数字的 CiM 种类繁多,需要从系统角度确定它们的适用性。2) 何时使用 CiM:ML 推理包括具有各种内存和计算要求的工作负载,因此很难确定 CiM 何时比标准处理内核更有优势。3) 在哪里集成 CiM:。每个内存级别具有不同的带宽和容量,这会影响到集成CiM带来的数据传输和局部性优势。

在本文中,我们将探讨如何回答这些有关 CiM 集成用于 ML 推理加速的问题。我们使用 Timeloop-Accelergy [1]、[2] 对 CiM 原型(包括模拟和数字基本运算单元)进行早期系统级评估。我们将 CiM 集成到类似 Nvidia A100 的基线架构中的不同级别的高速缓冲存储器,并为各种 ML 工作负载定制数据流。我们的实验展示了CiM 体系架构提高了能效,在 具有INT-8 精度的情况下,实现了能效比既定基线架构低 0.12 倍,在具有权重交错和重复的情况下,实现了高达 4 倍的性能提升。所提出的工作有助于深入了解应使用哪种类型的 CiM,何时以及在缓存层次结构中的哪个位置最优地集成它以加速GEMM运算。

机器学习(ML)应用已经在汽车、医疗保健、金融和技术等各个领域变得无处不在。这导致对高性能、高能效 ML 硬件解决方案的需求不断增加。

矩阵-向量乘法和通用矩阵-矩阵乘法(称为 GEMM)是卷积网络和transformers网络等 ML 工作负载的核心[3]、[4]。

由于此类计算是数据密集型,它们会产生很高的能耗成本,尤其是在诸如中央处理器(CPU)和图形处理器(GPU)等冯-诺依曼架构的计算处理器。而造成这种高能耗成本的原因是,在此类架构中,计算处理单元与存储单元分离,导致处理单元与存储器之间的存储器访问和数据移动成本高昂,这就是通常所说的 “存储墙 ”或 “冯-诺依曼瓶颈”。

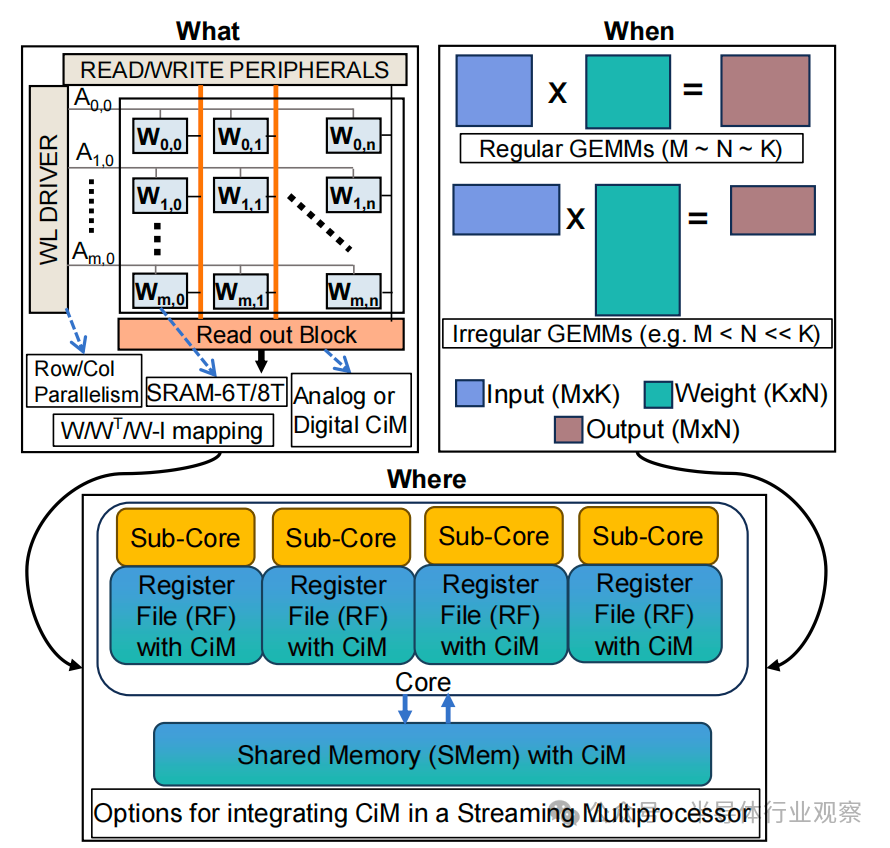

图 1. 概览图显示,要实现最佳的 ML 推理加速,需要了解各种 CiM 类型(What)、GEMM 形状(When)和内存级别(Where)的不同特性。

图 1. 概览图显示,要实现最佳的 ML 推理加速,需要了解各种 CiM 类型(What)、GEMM 形状(When)和内存级别(Where)的不同特性。

[5]。 为解决这一问题,人们提出了存内计算(CiM)范式,通过在内存中直接执行计算,以降低昂贵的数据移动成本,并提供高能效比解决方案[6], [7]。

将 CiM 集成到跨存储器层级的方法有很多:从 CMOS 片上高速缓冲存储器到 DRAM 或闪存 [8]-[10]。在这项工作中,我们重点关注在片上存储子系统中添加 CiM,因为这不需要激进极端的技术变革。虽然将 CiM 集成到缓存中的研究已经展开[11]-[13],但在系统层面对不同类型的 CiM 基元(或设计)的有效性,尤其是对 ML 推理的有效性进行全面评估的研究仍有待进行。我们的工作探索了在 GPU 的流式多处理器(SM)中将 CiM 集成到不同高速缓存级别、寄存器文件(RF)和共享内存(SMem)的好处(图 1)。GPU 由数百个 SM 组成,这些 SM 通过大型交叉条互连并通过L2级存储连接到 DRAM [14]。为了在存储器子系统中有效利用 CiM,需要确定 CiM 的最佳类型、何时使用以及在何处使用,以便进行 ML 推理。

什么类型的 CiM:根据计算类型,CiM 大致可分为模拟和数字计算两种 [15]-[21]。模拟 CiM 在存储器阵列内的模拟/混合信号域中执行乘法和累加(MAC)运算操作。为了实现不同 CiM 块之间的通信,需要使用数模转换器 (DAC) 和模数转换器 (ADC) 之类的外围电路,以减少模拟噪声对计算的影响。ADC 通常具有较高的面积、延迟和能耗成本,从而增加了整体模拟 CiM 的开销。相比之下,数字 CiM 通过执行比特逐位与/异或以及乘法运算,在数字域中执行所有计算。为了计算最终的 MAC 输出,需要执行多逐位操作,这可能会增加数字 CiM 的计算延迟。此外,存储器单元的类型(SRAM-6T/8T)、一次启用的字线或位线的数量以及存储器阵列中权重的映射方案等设计选择,也使得确定系统中最有效的 CiM 基本运算单元变得越来越具有挑战性。

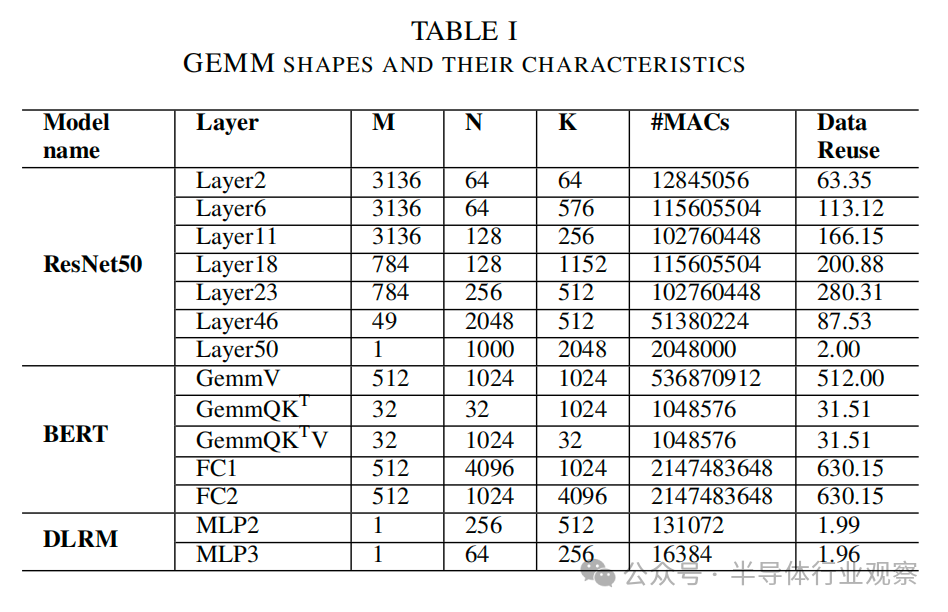

何时使用 CiM:ML 模型由各种 GEMM 的形状和大小组成。GEMM (M × N × K) 计算可视为将大小为 M × K 的输入矩阵与大小为 K × N 的权重矩阵相乘,得到大小为 M × N 的输出矩阵[22]。通过计算算术运算(浮点运算或 FLOPs)与内存访问(字节数)的比率,算术强度或数据复用可以了解 GEMM 计算对内存的依赖程度。图 2 显示了 GEMM 性能与算术运算强度之间的屋顶线表示。该图表明 并非所有的 GEMM 都需要 GPU 的全部功能,从而导致 SM 利用率不足。当采用 CiM 进行 GEMM 计算时,它有可能保持与标准计算范式相当的性能。2) GEMM 对计算和内存的要求范围很广。因此,目前还不清楚 CiM 在能耗和性能方面的优势何时会高于基线。

在何处集成CiM:由于 GEMM 具有规则的数据访问模式,并提供较高的时间局部性和空间局部性,因此矩阵以块或更小的tile为单位从主存储器获取到高速缓存中[23]。通常情况下,GPU 会优化其内存层次结构,以高效地重复使用tile数据,并在 SM 的子核中的数百个张量核上并行执行 GEMM 操作。基于 CiM 的硬件设计也能通过在内存阵列内启用多列和多行以及利用多个内存阵列的并行性来执行并行矩阵乘法。然而,每个内存层级在带宽和存储容量方面都有所不同(表五),这影响了数据复用机会以及重新利用 CiM 功能时的计算并行性。因此,找到一个能很好地利用局部性并提供最高 CIM 效益的内存级至关重要。

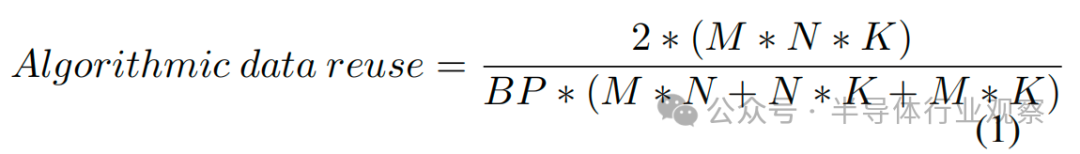

我们的方法为了充分利用和评估 CiM 相对于通用处理器的优势,我们考虑了一系列工作负载规格、内存级别和 CiM 特性。随后,针对给定规格选择最优数据流对于实现尽可能高的性能和能效非常重要。最优数据流通过在给定硬件资源上高效调度和分配 GEMM,减少内存访问次数,从而影响数据复用。GEMM 的算法数据复用可以用 MAC 运算次数除以矩阵总大小来计算。但需要注意的是,观察到的数据复用是由数据流决定的,因为它取决于存储器访问的实际次数。

在类似 Nvidia-A100 的基线架构中,分析评估基于 SRAM 的RF和 SMem 级模拟和数字 CiM 基元。

通过为给定的 CiM 架构和 GEMM 形状找到最优数据流,优化 CiM 带来的性能和能效提升。

从能耗/性能的角度详细解答各种 GEMM 形状的 CiM 的类型、时间和位置的选择。

本文其余部分安排如下:第二节将我们的工作与过去的其他研究区分开来。

下一节(III)介绍了这项工作的相关背景。第四节详细介绍了用于实验的 CiM 基本计算单元集。

下一节(V)重点介绍了主要收获、结果和讨论,最后一节是结论。

02. 相关工作

虽然已有研究考虑了 CPU 中的缓存内计算,但还没有研究将 GPU 内存重新用于计算。例如,Duality 高速缓存[11]架构重新利用了服务器级至强处理器的末级高速缓存来加速数据并行应用。他们还扩展了系统堆栈,开发了类似于 CUDA 的单指令多线程(SIMT)编程模型,用于在缓存中执行浮点和整数算术运算。MLIMP [12] 通过为多层内存处理系统开发并发任务调度程序,扩展了图形神经网络的 二元缓存(Duality Cache) 概念。他们提出了基于内存类型(位串行存储 SRAM/忆阻器ReRAM/动态存储器 DRAM)的任务调度和内存分配算法。另一方面,这项工作的重点是分析将 GPU 不同层次的内存重新用于 ML 推理的好处。我们之所以考虑 GPU,是因为 GPU 在加速 GEMM(推理任务的核心计算)方面具有广泛的优势。此外,GPU 是可编程加速器,同样的编程模型有可能重新用于集成 CiM 的 GPU。

Livia [13] 还研究了修改 CPU 中的高速缓冲存储器,以尽量减少不规则数据访问的整体数据搬运。它提出了一种系统架构,可在存储器层次结构的不同位置动态调度任务和数据。相比之下,我们的重点是关注高度规则的工作负载(GEMM),并确定 CiM 基本计算单元提供的并行性是否能与高速缓存层次结构提供的局部性优势相匹配。

To-Pim-or-Not[25]是第一个提出如何以及何时在不同应用中使用存内处理(PIM)问题的工作。它侧重于开发一个软件框架,以确定何时以及如何有效地将计算卸载到 PIM,同时分析性能优势和卸载成本之间的权衡。然而,这项工作的范围仅限于新兴的通用 DDR 存储系统,从而造成了对基于 SRAM 的 CIM 基本计算单元的理解上的空白。我们的工作通过考虑在GPGPU 的高速缓存层次结构中的运用 CiM基本计算单元,从而填补了这一空白。最近另一项关于内存中模拟与数字计算基准测试的工作 [26],基于固定的模拟 CiM 和数字 CiM 设计(称为模板),开发了一种量化能耗模型。然而,CiMMacros基本运算单元在外围电路方面差异很大,使用模板限制了 CiM Macro基本运算单元的设计选择。此外,它也未提及在具有可配置数据流选项的系统中的 CiM 延迟或性能评估。我们利用 Timeloop 模型 [1] 方法对不同 CiM 基本运算单元的系统进行分析评估。Timeloop 考虑了具有算术单元和内存层次结构的通用架构模板。

03. 背景

A.GEMM 在 ML 工作负载中的重要性

机器学习工作负载由各种神经网络组成,从卷积、全连接到Transformer和推荐模型。矩阵-向量乘法和矩阵-矩阵乘法是这些神经网络计算的核心[3], [4]。在本文中,我们将此类乘法统称为通用矩阵-矩阵乘法或GEMM(M×N×K)。M、N 和 K 用来表示矩阵的维数(图 1),其中 K 是约简维数。

通过使用 im2col 将输入和权重特征图的卷积操作转换为矩阵-矩阵乘法,可以将卷积神经网络 (CNN) 作为 GEMMs来 实现[22]。im2col 或图像-列转换将三维卷积操作转换为 GEMM (M,N,K),其中K代表输入和权重之间 MAC 操作的约简维度,M 代表此类约简或卷积的总数,N则根据输出通道的数量决定。与其他层相比,CNN的初始层通常具有更大的输入特征图,适用于较大的数据集,如ImageNet。最后一层是分类器,本质上是全连接(FC)层。它由矩阵向量乘法组成,可以看作是GEMM的一种特例。同样,Transformer网络模型根据初始层的输入嵌入计算查询矩阵(WQ)、键矩阵(WK)和值矩阵(WV),可视化为相同形状的 GEMM。此外,Transformer网络模型由其他 GEMMs 组成,如logit(QKT)、注意力(QKTV)和输出(WO)计算,然后是FC层。另一方面,推荐模型采用多层感知器(MLP),从稠密特征池和用户偏好中预测项目[27],基本上由 FC 层组成。表I列出了 GEMM 的形状,代表了各种ML工作负载的形状和大小。

B.基于 SRAM 的存内计算基本计算单元

与逻辑运算相比,内存访问的成本较高[28],因此很多人提出在片上 SRAM 中执行计算[29]。这些 CiM Macros的设计方式可以基于模拟或数字以各种方式设计。另一个关键因素是所使用的 SRAM 单元类型。这些单元的晶体管数量各不相同,常见的有 6T [20]、8T [17] 和 10T [30] 单元。此外,CiM Macros的输入数据存储或应用于 CiM 计算的方式也各不相同。例如,输入可以存储在 CiM Macros本身,也可以从外部缓冲器应用到 CiM Macros。

在数字CiM中,乘法和累加运算是通过位串行逻辑门在数字域中进行的。这种逻辑单元通常置于 CiM macro的外围电路中 [15]、[18]、[19]。数字 CiM macro的计算并行程度通常取决于macro中添加的逻辑资源量。然而,在数字 CiM 设计中添加更多逻辑电路会导致显著的晶圆面积开销[18],从而影响性能/能耗-面积的权衡。另一方面, 模拟CiMmacro通过字线输入比特来执行 MAC 运算,同时将权重值存储在CiM macro中 [16], [17]。输出生成为位线上的模拟电压或电流,其需要通过模数转换器(ADC)将其转换为数字信号,以实现macro之间的通信鲁棒性。值得注意的是,模数转换器是模拟CiMmacro的主要面积/延迟/能耗的瓶颈[31]。已有的技术试图通过更窄的输出精度或新颖的ADC电路设计来摊销 ADC 的成本,以获得更好的能效/性能 [16]、[17]。值得一提的是,数字 CiM 可与最先进的晶圆制造技术工艺节点相兼容匹配 [19],而模拟 CiM 则不可以,在这种先进的技术节点上,ADC会出现明显的噪声 [32]。

如前所述,CiMMacros包括各种 SRAM 单元类型。CiM Macros通常采用 8T(Transistor) 单元,因为它们具有解耦的读写端口,可将读取干扰问题降至最低[15],且噪声容限高于 6T 单元。基于 8T 的 CiM 可同时支持多条字线,从而实现更多并行 MAC 操作并提高能效。另一方面,6T 单元由于结构紧凑面积小,已成为常规SRAM 设计的技术标准。。从而为了减少 8T 单元的面积开销,人们提出了基于 6T 的 CiM设计。为了避免基于 6T 的 CiM macro的读取干扰问题,目前提出了几种电路技术 [16]、[18]、[20]。例如,为了执行基于 6T 的模拟 CiM,[16]、[20] 在共享相同位线的一组 6T 单元中添加了一个本地计算单元块。在一列中有多个组,其中不同组中的两个单元不共享同一位线。需要注意的是,在计算过程中,每个本地计算单元块只激活一个 6T 单元,以避免读取干扰。除了基于 6T 和 8T 的 CiM之外,一些报道过的macro还采用了其他单元类型(如 10T [30]),它们可以在单元内执行更复杂的计算(如脉冲神经网络的内存内加法和膜电位更新),但同时会导致更大的面积开销。

CiMmacro的输入方式也各不相同。输入数据可以在计算之前存储在 CiM macro中[15],也可以在 CiM运行过程中从外部缓冲区流进macro[17]。输入存储/数据流会对相应的 CiM macro产生不同的映射/数据流约束,从而导致不同的最优数据变化。

此外,在这些研究中还出现了不同的输入/输出精度,这给比较带来了挑战。为了进行公平比较,我们在这项工作中将输入/输出精度固定为 8 位整数。值得一提的是,不同的CiMmacro由于其独特的计算性质,可能会在macro级别上强加某些数据流 [15], [16]。

C.高速缓存层次结构中的数据流优化

GEMM 由于其规则的数据访问模式而表现出很高的空间和时间局部性。为了利用这种局部性,GPU 通过分片(或分块)输出矩阵和并行执行分片计算来实现 GEMM [23]。对于给定的数据流,循环因子解释了这种分片的大小,而循环顺序(数据流循环表示中的 M、N、K 顺序)决定了在给定存储器级别上分片的复用。 算术强度或数据复用可以计算为运算次数除以从存储器中提取的矩阵的总大小::

假设每个矩阵从主存储器访问一次,其中 BP 为位精度。

存储器访问的次数取决于矩阵如何被划分成片以及不同矩阵维度的获取顺序,这称为数据流。因此,观察到的数据复用可能与算法上的数据复用不同。

GEMMs 的性能受到其算法运算强度和硬件资源的限制。算术强度低的 GEMM 受存储器带宽的限制,而算术强度高的 GEMM 则受峰值性能的限制。cuDNN 和 cuBLAS 等软件库可用于决定tile大小,以便在给定 GEMM 形状下实现尽可能高的性能。tile越大,数据复用率越高。数据复用的增加可降低带宽要求,提高效率。然而,选择较大的tile可能会减少可并行运行tile的数量。这种减少有可能导致性能降低。

鉴于在 GPU 上优化 GEMM 的实现是为了获得最佳性能,因此为 CiM 集成架构实现最优数据流也很重要。在探索数据流搜索空间和选择最优数据流方面有多项研究。SCNN [33] 是最早为深度神经网络(DNN)引入数据流优化的著作之一。他们提出了一种输入固定数据流,即输入激活保持静态,允许其乘以每个输出通道所需的所有滤波器权重。此外,Timeloop [1] 提出了一种低成本映射器和模型,用于探索 DNN 和 GEMM 的数据流搜索空间。它将输入问题的大小建模为嵌套循环,从而可以评估数据复用的机会,并在不同架构和工作负载之间进行高效映射。Maestro [34] 是另一种工具,它提出了一种分析成本模型,利用以数据为中心的方法评估数据流中的成本效益权衡。ZigZag [35]也通过将搜索范围扩大到不均衡调度机会来探索 DNN 加速器的设计空间。

04. CiM 架构构建

为了估算不同 CiM 基本计算单元的能耗和性能,所有评估都使用 TimeloopAccelergy 框架 [1]。我们选择 Timeloop/Accelergy 基础架构是因为:1.它是一种快速分析模型,在研究项目中广泛用于早期设计估算;2.它提供了一种映射器,可为给定架构选择最佳数据流;3.它是一种灵活的工具,过去曾用于模拟 CiM 的建模[36]。

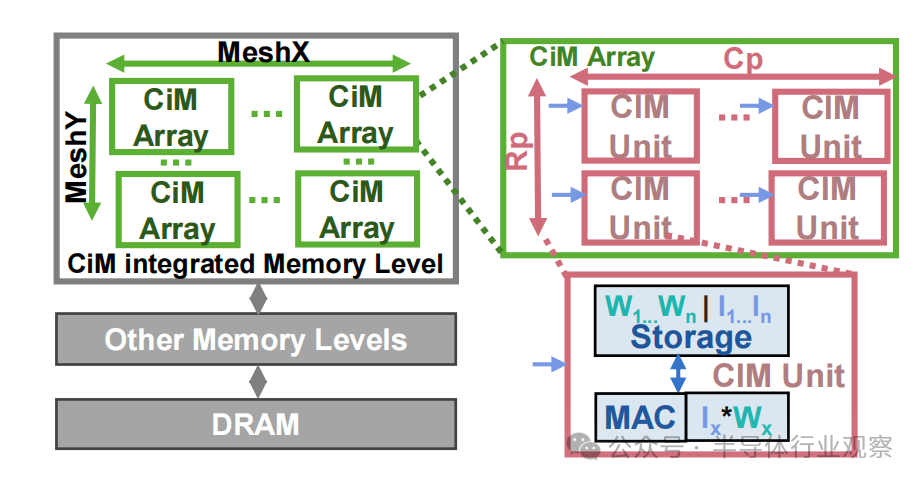

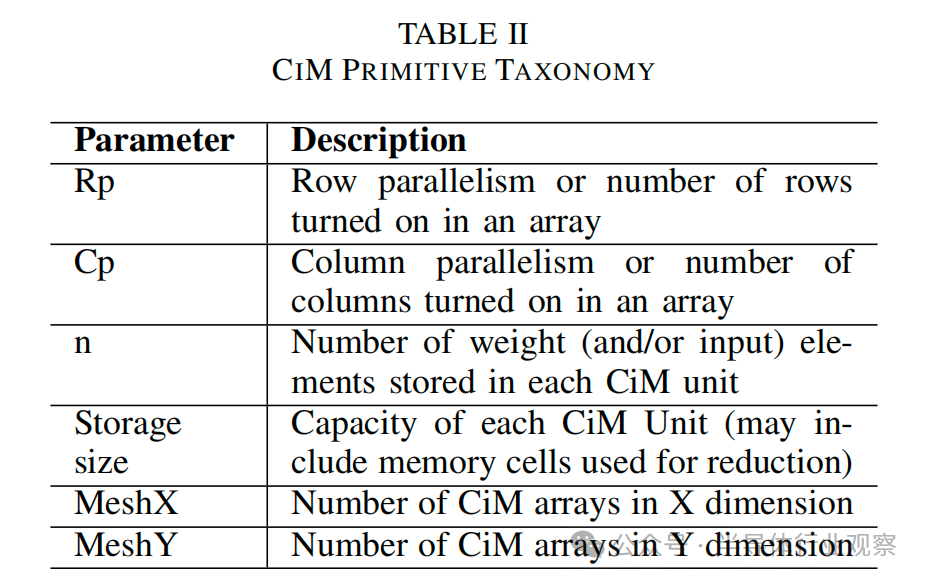

该框架将架构、约束、映射配置和能耗表文件作为输入。为了进行评估,我们创建了单独的架构模板文件,用于在RF和 SMem 层面集成 CiM(图 1)。如图 3 所示,这样的架构模板将运算单元块在存储器级别替换为 重新设计使用的CiM 的模块。这种 CiM 集成存储器级由多个 CiM 阵列(MeshX、MeshY)组成,取决于存储器的大小和容量。每个 CiM 阵列是一个 CiM 单元网络,一次可计算一个 MAC。CiM 单元的数量取决于阵列中同时开启的行数(Rp)和列数(Cp)。因此,所有 CiM 单元都可以并行执行 MAC 运算。由于 CiM 阵列中的所有列/行通常不会同时打开,因此 CiM 阵列的这种顺序性以时间循环因子 (n) 的形式体现(参见图 6)。这种 “并行输出-顺序输入 ”模板方法(图 3)可同时捕捉模拟和数字信号。图 3)同时捕捉了基于模拟和数字的 CiM 类型。表 II 详细列出了 CiM 架构模板中使用的参数。

图 3. 用于在 Timeloop 中表示 CiM 基本计算单元的架构模板文件框图。内存级被重新组合为计算级,表现为多个 CiM 阵列的网络。每个 CiM 阵列由可并行操作的单个 CiM 单元组成,每个 CiM 单元一次计算一个乘法累加 (MAC) 运算。CiM 单元的存储空间可能只包含权重,也可能包含权重和输入,具体取决于 CiM 基本计算单元的原始映射约束。

图 3. 用于在 Timeloop 中表示 CiM 基本计算单元的架构模板文件框图。内存级被重新组合为计算级,表现为多个 CiM 阵列的网络。每个 CiM 阵列由可并行操作的单个 CiM 单元组成,每个 CiM 单元一次计算一个乘法累加 (MAC) 运算。CiM 单元的存储空间可能只包含权重,也可能包含权重和输入,具体取决于 CiM 基本计算单元的原始映射约束。

根据原始 CiM 硅原型测得的性能数据,向 Accelergy 提供了 CiM 能耗表。由于原型在电源电压和技术方面存在差异,因此根据已完成的缩放工作[37],对能耗数据进行了缩放,以匹配 1V 电源的 32nm 技术。在 Timeloop 架构模板中假设频率为 1GHz,通过计算周期的延迟来捕捉 CiM 基本计算单元工作频率的差异。下一节将介绍如何调整约束配置,以获得每个输入规格的最优数据流。

05. 演进

A.实验设置

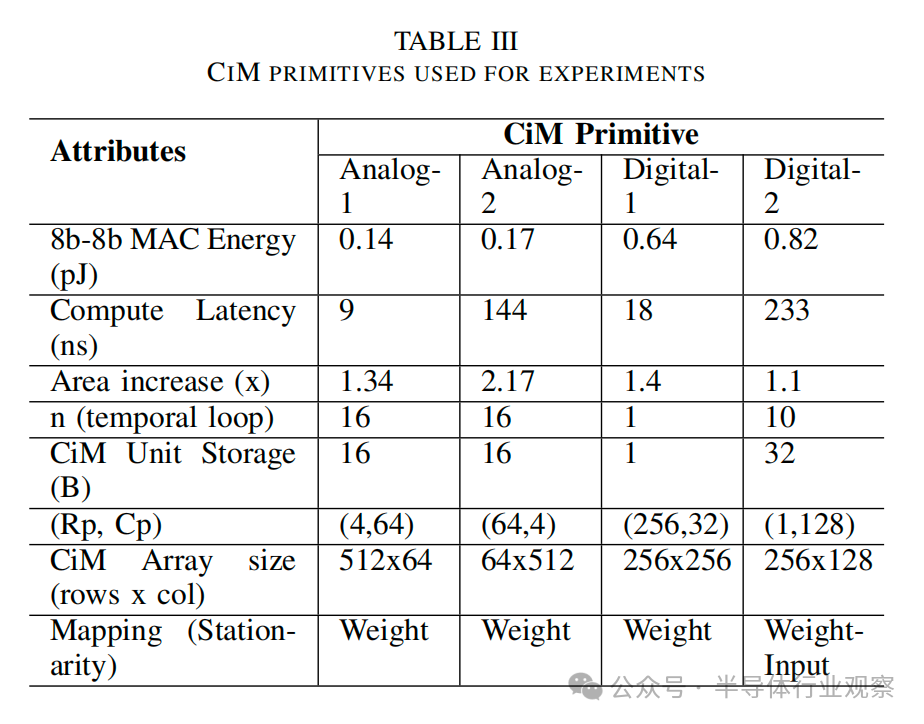

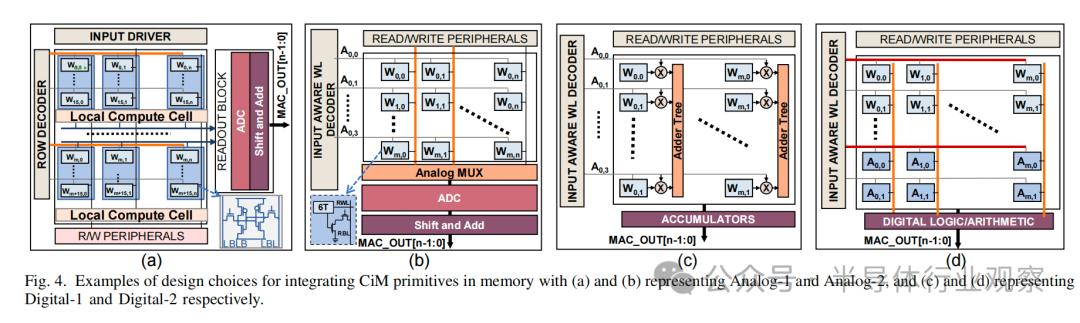

1) Cim 基本计算单元:我们为模拟/混合信号和数字CiM选择了两种最先进的基于 SRAM 的基元,如图 4 所示。这些基本计算单元涵盖了一系列不同的参数,详见表 III 和下文说明。

如图4(a)所示,Analog-1 [16] CiM基本计算单元由4个存储体组成,每个存储体有4个128x64 SRAM6T单元块。它采用转置映射技术,向多个列提供输入。这种配置产生256个(4×64) CiM单元,每个单元有128b (16×8b)存储空间。每个单元可以在9个周期内执行8b-8b MAC操作,同时处理2bit个输入并激活8行权重位。然而,由于每个组共享的ADC数量有限,因此该基本计算单元的时间循环因子设置为16。

图 4(b) 所示的模拟-2[17] 基本计算单元采用可重新配置的 ADC 设计,有 8 个阵列,每个阵列(64×64)存储不同的权重位,每个计算周期有 4 个 ADC 输出。这种设计产生了 256 (64×4)CiM 单元,每个单元能在144个周期内执行 8b-8b MAC,包括位串行延迟和从65纳米到 32 纳米的缩放调整。每个CiM单元包含 8×(64÷4) 个权重位,由于ADC的限制,这些权重位需要按顺序依次计算。这种基元的单次计算能耗较低,但由于其可重新配置的特性,面积开销较大。

图 4(c)所示的 Digital-1 [18]采用全数字设计,将输入输送到每一行,并使用加法器树在每一列执行 MAC 运算。这里每个 CiM 单元通过组合存储在 8 列中的权重比特来计算1个8b-8b MAC。加法器树的减少产生了面积开销,但导致 18 个周期的计算延迟。

图4(d)中的Digital-2[15]基本计算单元显示了输入和权重都映射到同一列的设计。这种配置允许每个CiM单元(包括单列)执行大约10个8b-8b MAC操作。然而,每个操作都需要233个周期,这归因于过程中涉及的多个加法。尽管面积开销很小,但由于在列中分配一些数组位以减少输出,因此计算并行性受到限制。

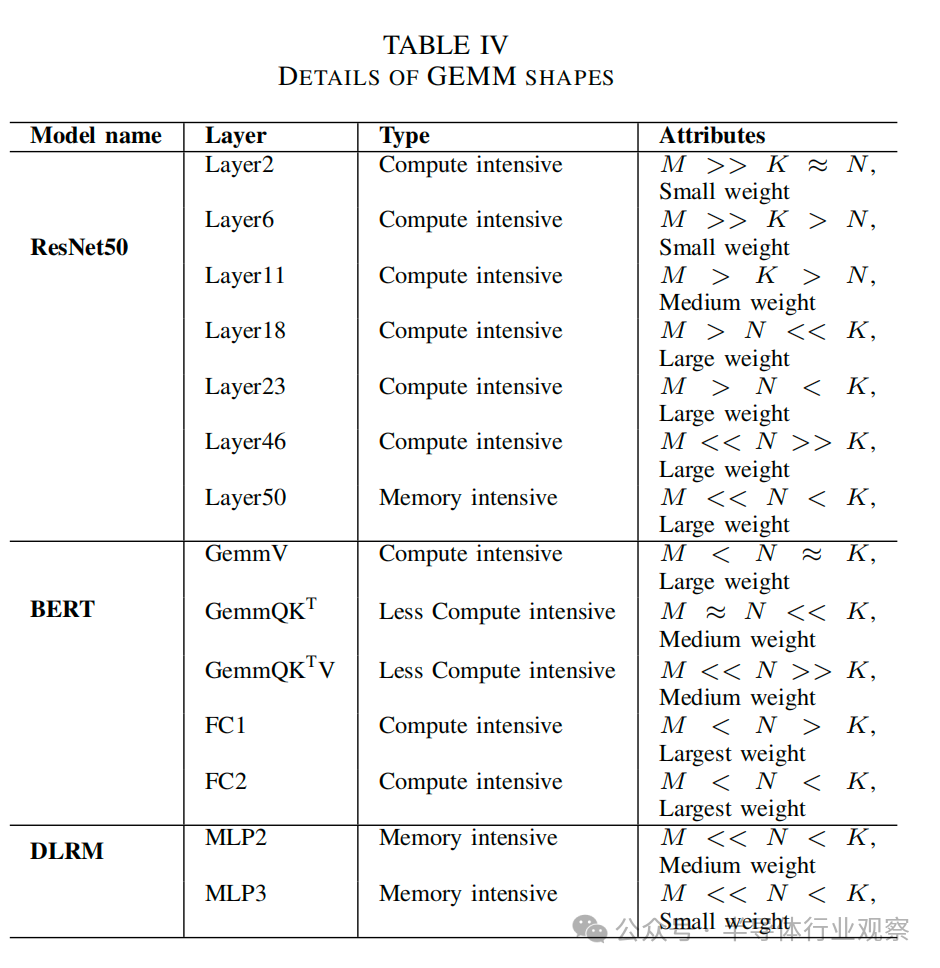

2) GEMM形状:我们从ResNet50[38]与ImageNet[39] 、序列长度等于1024的 BERT-medium[40]和DLRM[27] 等常用ML模型中提取了各种GEMM形状。我们根据表 IV 所列的 GEMM 形状的独特属性对其进行了剪枝,以涵盖不同的权重大小、形状和计算性质。如图 2 所示,计算密集型 GEMM 位于屋顶线表示的平顶下方。它们的数据复用率较高,这意味着每次内存访问的计算次数较多。另一方面,内存密集型GEMM位于带宽受限的屋顶线下方,以内存访问而非计算为主。表中计算密集度较低的GEMM技术上属于计算密集型区域。不过,它们的数据复用程度中等,形状偏斜。

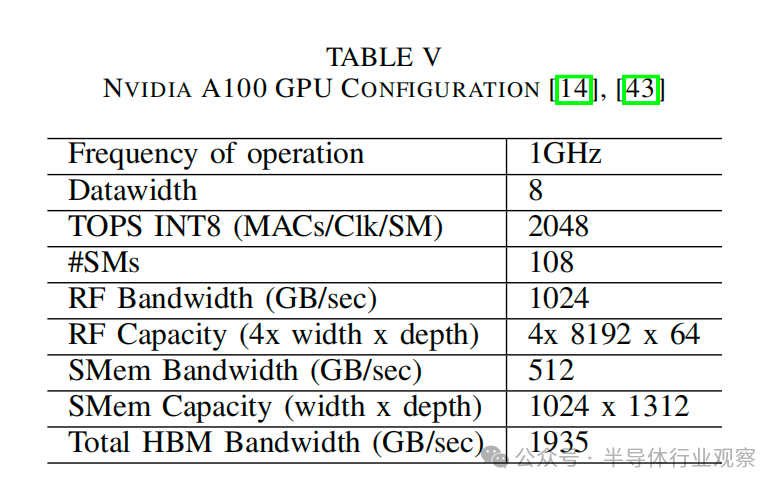

3) 基准:我们假设采用单个SM基准架构,与最新GPU(Nvidia A100)的规格一致,详见表 V。所有实验都是在INT-8精度、权重固定数据流和等面积约束下使用Timeloop/Accelergy 框架进行的。之所以选择 INT-8,是因为它在 ML 推理任务中是可接受的精度[41]、[42]。等面积假定,通过调整容量,CiM 整合后的内存级面积保持不变。 由于A100由108个SM组成,我们大约假设1个SM架构的总HBM带宽为10%。

B.数据流的影响

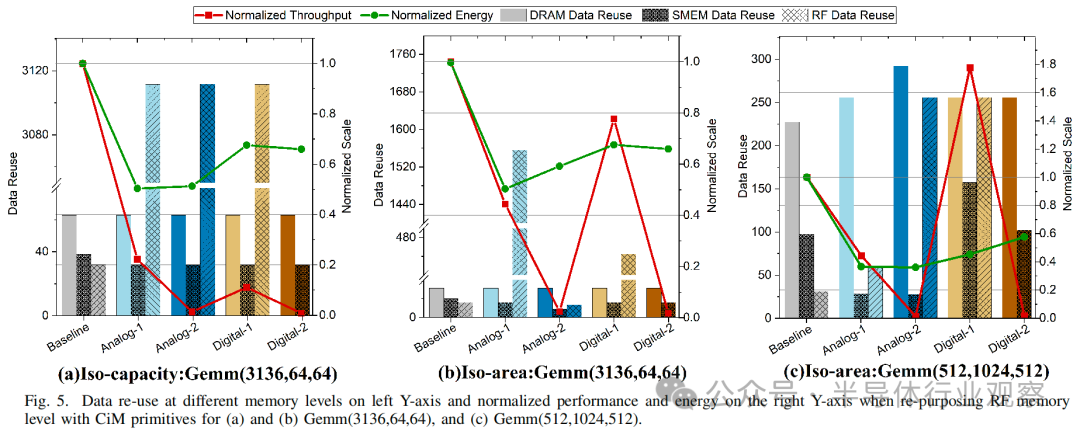

在本小节中,我们将简要讨论在寄存器文件RF中集成了CiM的两种GEMM形状,以强调不同的基本计算单元如何利用数据复用的机会。通过为每个基本计算单元设置约束文件,使用timelloop映射器找到最优数据流。图5显示了CiM级别的样本数据流,其中在约束文件中根据CiM类型设置了突出显示的参数。为了最大限度地提高性能,我们设置了映射的约束,以便在CiM单元中并行完成最大的计算,即使用权重交错。其他优先级是最大化映射权重的输入数据复用,并在有利的情况下允许权重重复。

当权重(N × K)矩阵较小,且 M 明显超过 N 和 K 时(图 5(a)中为 Gemm-3136 × 64 × 64),权重可以与CiM 集成在寄存器文件 RF存储器。这里,每个CiM基本计算单元由4096个CiM单元组成。基线已经在DRAM上实现了最高的数据重用(≈63,见表I),并可以跨CiM基础计算单元进行维护。然而,CiM 可以通过重复使用存储在 SMem 中的整个输入tile(M×K),更好地利用寄存器 RF及的输入数据重复利用率(≈3112)。这就降低了 CiM 的内存访问次数,从而将总能耗降低了 0.50 倍-0.67 倍。就吞吐量而言,CiM 的吞吐量受到了严重的影响,仅为基线吞吐量的 1%-22%。高计算周期 CiM 基本计算单元的计算周期比基线高 1 个周期,这直接影响了最终吞吐量,即使使用权重交错映射也是如此。因此,在等容量限制条件下, 由于并行性有限,不可能达到基线吞吐量。

如图 5(b) Gemm-3136x64x64 所示,在等面积限制下,CiM 的吞吐量损失可以部分抵消。这些限制允许在每个基本计算单元的面积开销允许的范围内拥有尽可能多的 CiM 单元,从而扩展到 4096 个 CiM 单元以上。尤其是Digital-1 基本计算单元,通过复制权重,其吞吐量达到了基线吞吐量的 77%。由于写入 SRAM 单元比访问 DRAM 消耗更少的能量,因此权重复制能以最小的能量成本提高吞吐量[6]。需要注意的是,重复的次数受 CiM 单元数量和向 CiM 单元广播输入的上层存储器容量的限制。

当权重矩阵过大而无法放入内存(图 5(c)Gemm-512x1024x512)且 M ≈ K 时,与基线相比,CiM 基元可利用 DRAM 中更高的数据复用率。这就减少了最后一级访问,节省了更多能耗(是基线的 0.36-0.57 倍)。在吞吐量方面,较小的输入矩阵(M×K)减少了对共享内存容量的限制。这意味着所有 M 个维度都可以存储在 SMem 中,用于映射 K 个维度,因此,如果有足够的 CiM 单元,就可以进行更多的权重复制。Digital-1 利用这一机会 实现高于基线的吞吐量。Analog-2 和Digital-2 的吞吐量最低,因为它们的性能受到高计算延迟的限制。此外,面积开销和映射限制也限制了它们的吞吐量。Analog-2 的面积开销较大,限制了同一面积内可容纳的 CiM 单元数量。Digital-2 有一个固有的面积开销,这是由于在同一列中映射输入和部分输出位的限制造成的,这进一步限制了可以并行操作的 CiM 单元的数量。

基于同样的思路,我们确保所有工作负载都以最佳方式映射,并在接下来的小节中讨论不同 GEMM 形状、CiM 类型和存储器级别的结果,以深入了解 “什么”、“何时 ”和 “何地 ”的问题。

C.性能结果

图 7(a)和图 7(c)分别比较了在寄存器文件 RF和 SMem 级集成 CiM 时观察到的性能。

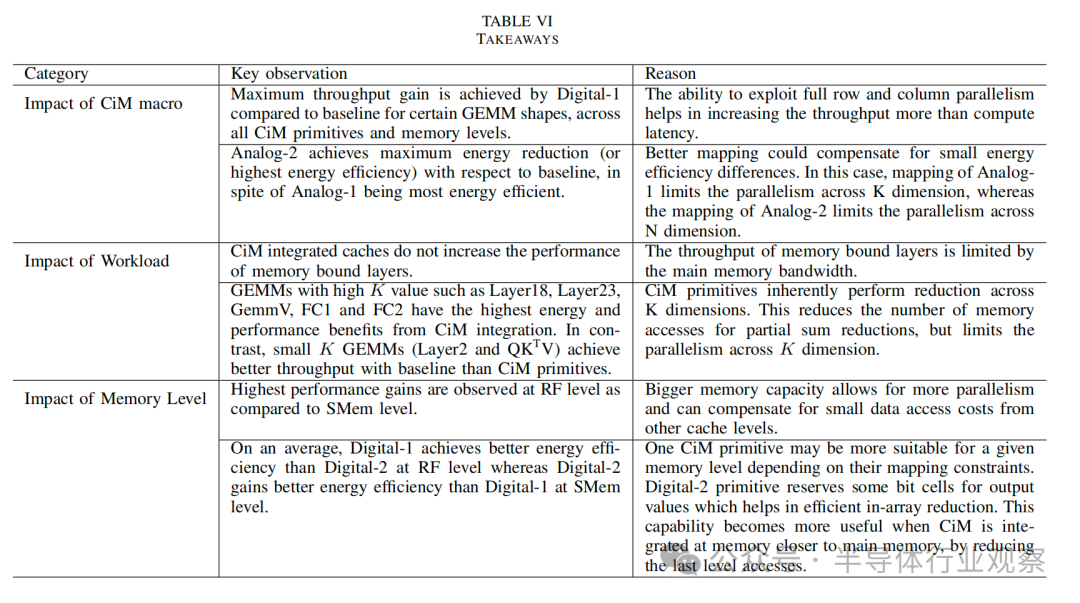

What:比较不同的CiM基本计算单元,Analog-1具有较小的计算延迟(9个周期)的其显示的性能范围为基线吞吐量的22%到100%。另一方面,Digital-1(计算延迟为 18 个周期)的吞吐量可高达基线吞吐量的 450%,总体上接近基线吞吐量,但某些 GEMM 除外(在 “何时 ”一节中讨论)。这意味着,在 CiM 设计中,对于吞吐量而言,利用全行和全列并行性的能力比实现尽可能低的延迟更为重要。不过,也不能完全忽视延迟,正如Analog-2 和Digital-2 基本计算单元的较低性能所描述的,计算延迟分别高达 144 和 233 个周期。

When: 与其他 GEMM 形状相比,具有较大权重矩阵的计算约束/密集层(Layer6、Layer18、Layer46、GemmV、FC1 和 FC2)在使用 CiM 基本计算单元时性能最高(在寄存器文件RF级重新使用时,最低为基线的 78%)。少数受计算约束/密集的 GEMM,特别是 K 值较小的 Layer2 和 QKTV,在所有 CiM 基元中的性能都不理想,分别只达到基线吞吐量的 39% 和 47%。这种较低的性能可归因于 Digital-1 的较低性能,这源于对 K 维度的映射限制。CiM 架构有权重 (N×K) 映射,以减少 K 维度上的多个部分和,从而限制了小 K 维度的并行性。基线则不存在此类限制,因此在此类 GEMM 中可获得更高的性能。同样重要的是,由于数据复用有限,CiM 基元的最高性能不会超过存储约束层(Layer50、MLP2、MLP3)的基线。

Where: 考虑到所有 CiM 基本计算单元的最高性能,在寄存器文件RF级观察到的最大吞吐量(≈400%)明显高于在 SMem 级观察到的吞吐量(≈170%)。这可归因于 SMem 的面积(164KB)小于单个内核中的 4 个 RF 实例(256KB),这使得相同面积中的 CiM 单元更少,从而限制了可实现的最大吞吐量。这种行为的一个反常现象是,由于内存宽度和高度限制的不同,映射器在 SMem 而不是RF上找到了利用率更高的更好映射。例如,尽管在SMem层级计算时存在带宽节流,但 MLP3 在 SMem 和 Analog-1 上的性能比在RF上高出≈50%。

D.能耗结果

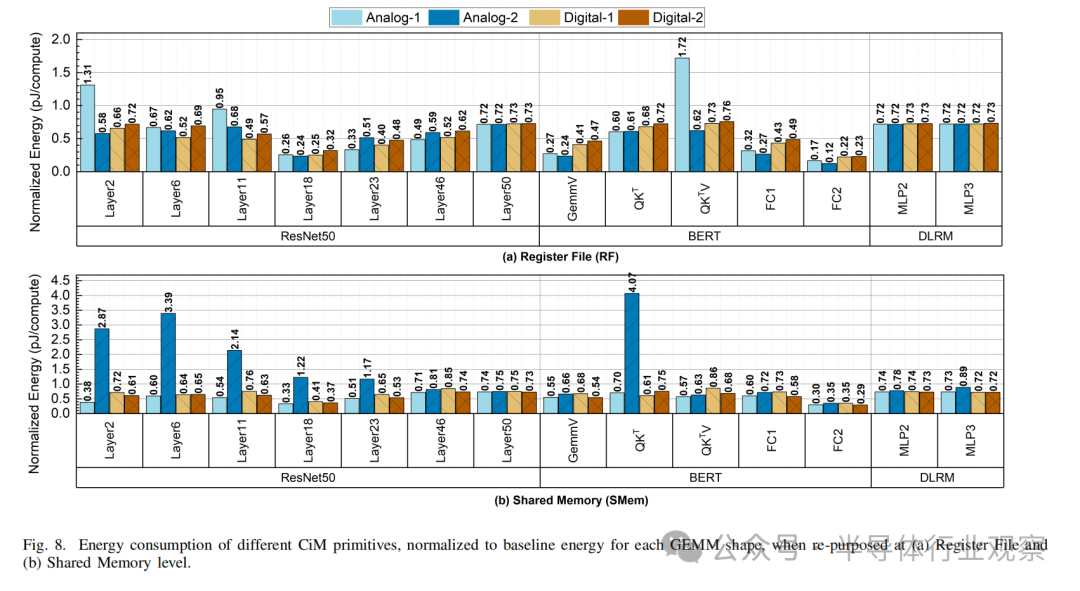

根据图 8(b) 和图 8(d) 所示的能耗,我们可以得出以下结论:

What:在能效方面,CiM 基本计算单元没有明显的优胜者。虽然 Analog-1 和 Analog-2 显示出最佳的能效,FC2 层的能效分别是基线能效的 0.16 倍和 0.12 倍,但 QKTV 层和 QKT 层的能效也分别高达基线能效的 1.7 倍和 4 倍。另一方面,Digital-1 和 Digital-2 基元的能耗始终呈下降趋势,分别为基线能耗的 0.22 倍至 0.86 倍和 0.23 倍至 0.75 倍。这表明,如果考虑到主内存,TOPS/W 最高的基本计算单元(本例中为 Analog-1)不一定是最节能的。对于无法映射所有权重(高 K 或高 N)的基本计算单元(取决于基元类型和内存级别),由于输出值的时间还原次数增加,总能耗会大于基线。举例来说,Analog-2 在 K 较大时表现较差,尤其是在 SMem 时,因为设计将 N 维并行化,并将 K 限制在 64。当权重矩阵较小时(例如,模拟-2-SMem 的 QKTV,其中 N 》》 K),效果会很明显,因为基线可以有效地减少部分和,并且不需要对主存储器级进行大量访问。SMem 的 Digital-2 也拥有较少的 CiM 单元,但与模拟系统不同的是,它允许将 K 维映射到同一阵列中的不同列。

When:我们观察到第 18 层、第 23 层、GemmV、FC1 和 FC2 的能耗降低幅度最大,分别为基线能量的 0.24 倍、0.33 倍、0.24 倍、0.27 倍和 0.12 倍,尤其是在寄存器文件RF层重新使用时。所有这些层的 K 值都很高,这说明当部分的求和降维的数量较多时,CiM 基元的能量效益最大。对于存储约束层(Layer50、MLP2 和 MLP3),所有 CiM 基元都表现出类似的优势,能耗降低了 30%,因为总能耗主要来自 DRAM 访问。

Where:由于更大的面积和更多的实例,寄存器文件 RF比SMEM具有更多的CiM单元,这通常导致更低的存储器访问或能耗。例如,对于 QKT 层,与 SMem 相比,Analog-2 从 RF 计算中获益最多。在 SMem 和 RF 中添加 CiM 后,总能耗分别从基准能耗的 4 倍降至 0.6 倍。同样,对于 GemmV、FC1 和 FC2 层,与 SMem 相比,RF 的Analog-1、Digital-1 和Digital-2 能耗分别约为 0.5 倍、0.6 倍和 0.8 倍。不过,从不同 GEMM 形状的平均值来看,根据基本计算单元设计和 GEMM 形状的不同,一种 CiM 基元可能更适合特定的存储器层。例如,Analog-2 基元的面积开销较大,在寄存器文件 RF层集成时的能耗总是低于 SMem。对于其他基元,SMem 的能耗可能低于 RF 的能耗,如 Layer2(M》》N≈K)。另一个例子是,与寄存器文件 RF相比,Digital-2 在 SMem 下的平均能效更高。

E.讨论与未来工作

启示: 随着 ML 模型的增大和存储器层次结构的发展,性能和能效增益的绝对数字可能会发生变化。不过,我们预计在等面积限制下,这些启示(表 VI)将保持不变。这些启示取决于分析评估,考虑到:1)性能收益由计算延迟和计算并行性决定;2)能效收益取决于内存访问和计算成本。对于 CiM 基元,并行性反过来取决于 CiM 基元的映射约束、存储器容量和面积开销。例如,Digital-1 CiM 基元的面积开销与 Analog-1 大致相同,而计算延迟几乎是后者的两倍。不过,由于映射约束更灵活,允许全行/列并行,Digital-1 实现了更高的并行性。另一方面,CiM 在能耗方面的优势取决于内存访问次数的减少和 CiM 单元固有的更高能效。数据流在减少内存访问方面发挥着重要作用,因此也能最大限度地提高 CiM 的效益,这一点在分析中也得到了考虑。

假设:我们的评估以 Timeloop 中使用的分析模型为基础,假定架构简化,内存子系统完全流水线化。在这种架构中,如果没有带宽限制,一个内存级访问的延迟会被其他内存级访问所掩盖。带宽限制取决于内存访问的总次数和该内存级的带宽。它假定所有访问都是合并的,并且不考虑诸如内存库冲突、有限的未命中处理缓冲区容量以及内存中的其他架构优化等影响。但它仍能捕捉到不同 CiM 基本计算单元的大致性能,有助于了解它们在系统级的影响。

将 CiM 集成到内存子系统的方法有多种。等容量集成 CiM 可以提供更高的并行性,但代价是增加晶圆面积。将 CiM 集成到等容量内存中会影响高速缓冲存储器的容量。这可能会进一步影响 SM 的基线吞吐量。不过,我们的工作设想了一种具有异构内核的架构,系统架构中既有 CiM SM,也有非 CiM SM。此外,我们在所有方案中都假设了权重固定的数据流,因为它是最常用的数据流。

在 CiM 数据流中增加更多灵活性可能会带来更大的设计空间,这仍然是一个有待探索的开放式搜索空间。此外,最近的研究[44]、[45]已经展示了浮点 CiM 加速器,扩大了内存中的计算范围。不过,这项工作中的所有实验都假定了 INT-8 精度,包括基线中的 INT-8 精度,以使其包含各种 CiM 基本计算单元。此外,我们仅评估了 ML 工作负载中的单个 GEMM 操作,以估算可能的最大性能和能效收益。对于端到端分析,一种方法是扩展 Timeloop,使其包括层融合等功能以及非 GEMM 操作的成本开销。层间评估还要求Timeloop考虑前一层的输入、权重和输出在内存层次结构中的位置,而当前版本不支持这一功能。需要注意的是,CiM 集成架构还会产生编程成本开销,在最终确定设计方案时应考虑到这一点。

未来的可能性:为了克服 ADC 模块影响模拟基本计算单元计算并行性的面积和延迟瓶颈,可以考虑采用无 ADC 模块的模拟基本计算元[46]。无ADC 模拟基元只采用读出放大器作为外围电路,将部分和从阵列转换为 1 位输出。这样的低面积开销基本计算单元可以在相同的内存区域内实现更多的 CIM 单元。这将进一步有助于通过更高的并行性实现更高的性能,同时大幅改善能耗。模拟基本计算单元的一个注意事项是计算精度的损失。无模数转换器 ADC的设计可能会因激进的硬件量化而导致较大的精度损失。不过,研究[47]表明,利用量化感知训练技术 QAT 可以将精度降低到最低程度。

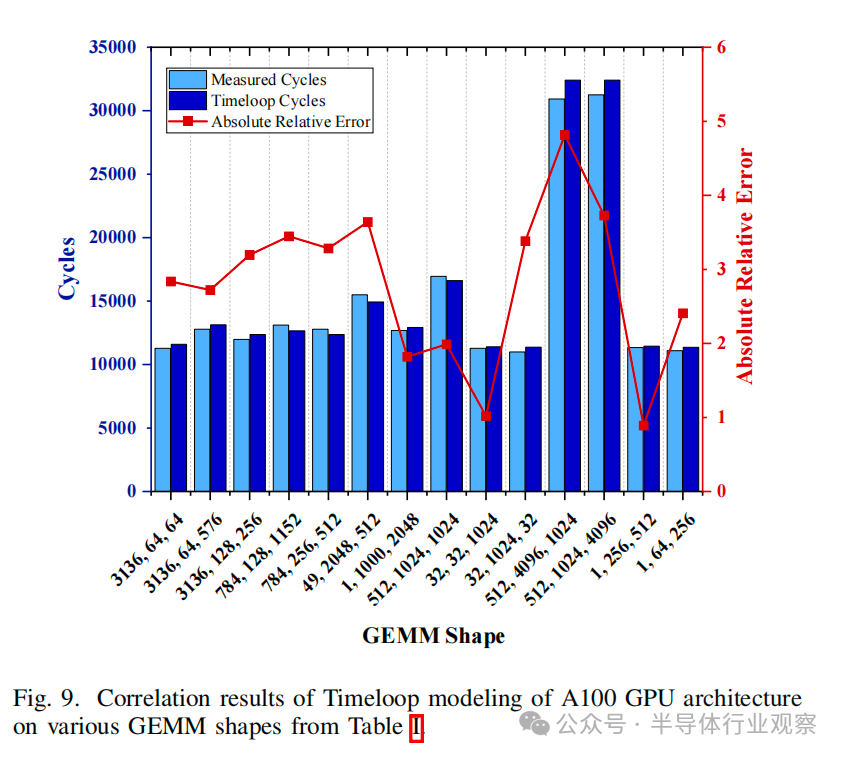

将 CiM 集成到内存子系统中的另一种方法是增加存储器级别或改变存储器技术以包括新兴的器件设备。此类研究不在本文研究范围之内。不过,我们的方法可以针对此类分析和新的 CiM 基本计算单元进行扩展。该分析还可以扩展到一个以上的 SM 架构,以包括 SM 间通信或网络成本。完整的类 A100 GPU 模型将有 108 个 SMs,可用于映射更大的模型。图 9 显示了 Timeloop 中 GPU 完整模型版本与表 V 中规格的性能相关性,图中使用 CUTLASS 3.2 [48]在 A100-80GB 上运行了测得的 GEMM 内核。然而,全 GPU 模型的设计空间会爆炸,数据流搜索时间也会成倍增加。评估全 GPU 类模型将需要进行优化或采用新方法,才能在如此大的设计空间中有效找到最优映射。

06. 结论

我们在 GPU 架构的片上高速缓冲存储器中集成了存内计算(CiM)。我们的实验全面分析了 CiM 在加速基于机器学习(ML)推理任务的通用矩阵乘法(GEMM)工作负载方面的优势。特别是,基于等效面积的分析评估得出了以下结论:

相比之下,虽然模拟基本计算单元达不到 Digital-1 的高性能水平,但它们在能效方面表现出色,能耗仅为基线能耗的 0.12 倍;数字基本计算单元紧随其后,最佳节能效果为基线能耗的 0.22 倍。CiM 在能效和性能之间的这种权衡可以使 GPU 受益,尤其是当 GPU 以较低频率运行以管理功耗时[49]。

When:调查表明,数据复用率高、K(》 M)值大的计算约束/密集层在性能和能效方面从 CiM 中获益最大。例如,BERT 模型中的全连接层(FC1、FC2)。相反,数据复用率低、K 值(《《 M)较小的计算绑定 GEMM 在使用基线时通常能获得更高的吞吐量,但在使用 CiM 时则显示出能耗优势。在我们的分析中,使用 Image net 数据集的 ResNet50 的初始层(如第 2 层和第 11 层)就是这样的结果。同样,偏斜 GEMM 在 K 》》 N 的情况下,能耗降低,吞吐量相当,但当 K 《《n 《=“” span=“”》时,性能下降。受内存限制的 GEMM(如 ResNet50 和 DLRM 中的全连接层)仅在 CiM 中显示出能耗优势,而吞吐量却没有提高。

Where:此外,研究结果表明,在集成 CiM 时,存储器容量比存储器层次结构中的层数更重要。存储器容量越大,权重重复的性能就越高。然而,映射约束和计算延迟等 CiM 特性仍会限制高内存容量带来的性能和能耗效益。

总之,这项工作对整个片上存储器层次结构中 CiM 基本计算单元的能耗、面积和性能之间的权衡进行了全面评估。我们相信,我们的工作为了解基于 SRAM 的 CIM 在实现可比性能的同时缓解能耗问题的潜力提供了重要见解。反过来,我们的方法也有助于优化基于 CiM 的 ML 推理架构。

致谢作者感谢 2021 年提供的北美 Qualcomn 创新奖学金为本项目提供资金,并感谢 Ramesh Chauhan 在项目初始阶段提供的投入。部分研究还得到了由 DARPA 和 SRC 资助的 7 个 JUMP 中心之一 CoCoSys 的资助。作者还要感谢 Aayush Ankit 的头脑风暴和讨论会议。

审核编辑:黄飞

-

jf_36592665

2024-12-06

0 回复 举报您好,请问这篇论文的相关参考文献在哪里啊 收起回复

jf_36592665

2024-12-06

0 回复 举报您好,请问这篇论文的相关参考文献在哪里啊 收起回复

-

jf_39752290

2024-09-07

0 回复 举报你好,请问这篇论文题目叫什么啊? 收起回复

jf_39752290

2024-09-07

0 回复 举报你好,请问这篇论文题目叫什么啊? 收起回复

-

知存科技启动首届存内计算创新大赛2024-11-21 1292

-

存内计算原理分类——数字存内计算与模拟存内计算2024-05-21 6063

-

存内计算技术工具链——量化篇2024-05-16 2642

-

知存科技WTM存内计算芯片原理分析2023-05-11 3649

-

什么是存内计算2022-08-08 5897

-

存内计算并不满足于现有的算力2022-05-11 3949

-

三星基于HMB的存内计算芯片有何亮点?2021-02-19 4073

-

深度学习推理和计算-通用AI核心2020-11-01 3585

-

用于边缘计算的机器学习技术介绍2019-01-15 3393

-

量子计算与量子机器学习的解析2018-01-24 7023

全部0条评论

快来发表一下你的评论吧 !