高增益LC谐振放大器的设计

模拟技术

描述

采用分立元件设计了一个3级单调谐放大器,可用于通信接收机的前端电路,通过合理分配各级增益和多种措施提高抗干扰性,具有中心频率容易调整、稳定性高的特点。电路经实际测试表明具有低功耗、高增益和较好的选择性。

本文设计的放大器具有增益和中心频率可调、低功耗、选择性好的特点。

1 电路原理及设计思路

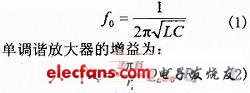

高频小信号调谐放大器对中心频率的信号具有最大放大能力,中心频率为:

式(2)中,ri为晶体管的输入电阻,QL是回路的有载品质因素,RL是晶体管集电极等效负载电阻,如果负载电感带中心抽头则需要将下一级电路的输入电阻折合到前级的负载电阻。选用高β值的晶体管,提高晶体管的静态工作点,提高回路的等效品质因素均可提高增益。

不过QL太高会使通频带太窄,反而可能引起自激,降低放大器的稳定性。

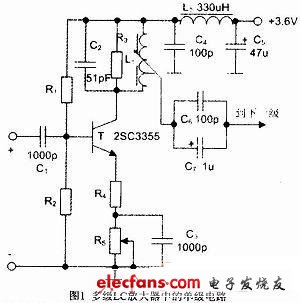

实际设计中,为了提高放大器增益,通常采用多级单调谐放大电路级联。n级相同放大器级联后的带宽和矩形系数为:

从式(3)、(4)可以看出,3级放大器的带宽约是单级的一半,矩形系数是3.74。多级放大器的带宽和矩形系数比单级放大器都要小。说明多级电路选择性更好,但电路也趋于不稳定。

减小带宽和矩形系数的值可以提高电路的选择性,由式(3)、(4)分析,增加QL和电路级数n可以满足要求,前者可以通过提高电感的绕制工艺实现,但如果QL太高则容易引起自激,不利于放大电路的稳定;n增加则增加了电路的复杂性,不但使电路元器件增加,而且调试过程加倍繁琐。本设计采用3级单调谐电路,制作和实测结果令人满意。

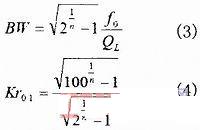

2 电路设计过程

单级电路图如图1所示。晶体管使用2SC3355,该晶体管具有特征频率高(6.5GHz)、结电容小的优点,可以保证所设计电路的稳定性。先设计静态工作点,电源电压3.6V,假设R1=75kΩ,晶体管T的基极电压是R1和R2的分压,为确保晶体管T在放大状态,考虑到低功耗,VB可设为1.0V左右,R2=33kΩ。射极电阻R4和R5的串联构成串联电流负反馈,起到稳定直流工作点的作用。R4取1kΩ,R5使用2kΩ的多圈电位器,通过调整其值可以调整静态工作点,一方面可改变增益,另一方面可调整放大器的稳定性。旁路电容C3取1000pF,以减小对交流增益的影响。电容C2(51pF)确定后,根据公式(1)计算电感值,我们自行绕制了带中心抽头的可调电感,用φ0.18mm的漆包线在中周骨架上饶14匝,7匝处抽出,通过电容耦合回路接入下一级放大器,回路谐振频率在15MHz附近,使用中间抽头的电感器可将较大的前级放大器输出阻抗与后级电路较小的输入阻抗相匹配。R3并联在LC谐振回路两端降低了回路的Q值,可有效防止电路自激,当然这样也降低了选择性和电路总增益。实际R3值的选择需要在增益和稳定性上取折衷值。单级放大器增益调节范围10~30dB。

放大器的电源退耦滤波和级间耦合回路设计是个难点,同时也是重点考虑的问题,如果设计不当,则多级电路很容易产生自激振荡。电源滤波采用π型非对称电路,可以有效抑制高频信号对直流电源的影响,该滤波电路的位置很重要,须靠近晶体管集电极并处于晶体管和电源之间。级间耦合电路采用两个电容的并联,可以有效消除自激和提高电路的稳定性。在放大器输入端需要设计阻抗匹配电路,将信号源内阻与放大器输入阻抗相匹配。输出端与负载之间接匹配电路可以提高传输到负载上的功率。阻抗匹配电路的设计使用Smith圆图,采用L型匹配网络。

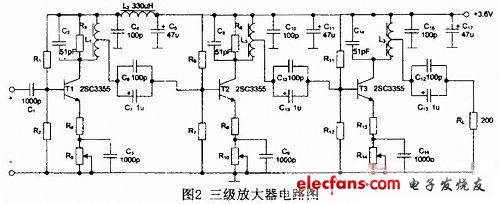

当采用多级电路耦合时,为了确保放大器的稳定性和选择性,实际调试时可将第一级电路的谐振频率设为稍低于15MHz,第二级电路的谐振频率调为15MHz,第三级电路的谐振频率稍高于15MHz,多级联调时用扫频仪可很快完成调试。特别要说明的是,每级放大器均需要单独设计电源滤波和退耦网络,而且每级放大电路的静态工作点均不同,需要实际调试确定。三级放大器完整的电路如图2所示。

3 测试结果

测试线采用一端Q9接口,一端SMA接口的高频屏蔽同轴电缆,经使用高频信号发生器AS1054和示波器TDS2012B测试,当输入信号15MHz,1mVrms时,三级放大器的电压增益分别是25dB、28dB和28dB,200Ω负载上的电压增益可达81dB,改变输入信号幅度,输出电压最大可达1V rms而无明显的波形失真,此时的电源功耗仅为75mW。用数字合成扫频仪SP31000测试放大器的谐振曲线,带宽280kHz,矩形系数为4.8,表明放大器具有低功耗、高增益、良好的稳定性和较好的选择性。

-

Hangsir

2015-07-11

0 回复 举报式2 被水印挡了... 收起回复

Hangsir

2015-07-11

0 回复 举报式2 被水印挡了... 收起回复

-

基于AD603数控高增益宽带放大器的设计2010-05-04 4786

-

高增益放大器2011-10-17 3391

-

三运放放大器怎么提高增益和CMRR?2020-03-11 4722

-

高增益带宽运算放大器2009-09-28 2613

-

高增益GPS LNA放大器2009-11-04 1963

-

CW系列高增益放大器电路图2011-06-27 1782

-

高增益跨导型运算放大器设计2012-02-08 1194

-

VCA810高增益调节范围宽带可变增益放大器2015-12-01 1664

-

C波段高增益放大器的设计2016-01-04 756

-

MEMS谐振器中高增益跨阻放大器设计2017-01-03 1354

-

基于宽带高增益的放大器设计2017-03-05 863

-

D-LC谐振放大器(D题)2017-07-21 1368

-

怎样设计一个低噪的高增益放大器?2023-10-12 2541

-

单调谐放大器负载阻值变化会对放大器增益及通频带宽带来怎样的影响?2023-10-20 3113

-

lc谐振放大器分为哪两种 谐振放大器原理是什么2024-01-25 3376

全部0条评论

快来发表一下你的评论吧 !