什么是内存语义?CXL是如何划分语义的

描述

随着人工智能大模型,高性能计算(HPC),大数据和搜推等业务的兴起,原本以Web服务为主要应用的数据中心也开始关注这些新业务所带来的需求变化,例如通过紧耦合计算网,提供更高的带宽和更低的延迟。而在紧耦合计算网中,是否支持丰富的内存语义成为了关键。

但究竟什么是内存语义,业界一直没有一个清晰的定义,有的人说Infiniband(IB)的RDMA语义就是内存语义,也有人说消息语义也是内存语义,也有人说访问内存的语义是内存语义,也有人说Load/Store语义是内存语义,众说纷纭,我们下面来看看Wikipedia是怎么定义内存语义的:

Memory Semantics(From Wikipedia)

Incomputing and parallel processing, memory semantics refers to the process logicused to control access to shared memorylocations, or at a higher level to shared variables in the presence of multiplethreads or processors.

Memorysemantics may also be defined for transactional memory, where issues related tothe interaction of transactions and locks, and user-level actions need to bedefined and specified.

可以看出,维基百科认为内存语义是针对多线程针对共享内存区进行的操作,又或者是针对内存的访问操作等。

为了更好的解释什么是内存语义,我们先来看看什么是语义以及IB中是如何划分语义的:

什么是语义?

通常来说,语义就是互联中用于交互的一个或者多个操作的组合,通常在事务层(TransactionLayer)中定义。(IB没有事务层,所以IB在传输层中定义了语义)

IB语义划分

IB介绍了两种语义,分别是ChannelSemantics(通道语义)和Memory(RDMA)Semantics(内存语义/RDMA语义)

其中,Channel Semantic包括Send/Receive操作;RDMA语义包括RDMA WRITE,RDMA READ和ATOMIC操作;

IB语义划分依据猜测

从IB提供的具体操作来看,Send/Receive,RDMA_Read,RDMA_Write和ATOMIC操作实际上都是针对内存的操作,所不同的是,Send/Receive操作的请求端不知道响应端会将数据写到哪里,即请求端在发送Send请求时,不需要填写目标地址。但实际上,最终这笔数据还是写到响应端的内存中去了。所以严格意义上说,Send/Receive操作仍然属于内存相关操作,只不过IB希望与另外三种操作做出区分。于是Send/Receive操作被赋予了新的名称,被称为Channel Semantics,意思就是在通道的一端你只管send数据就好,具体数据去哪了,通道的另一端会负责处理。

RDMA_Read,RDMA_Write和ATOMIC操作有一个共同点就是三种操作都需要指定响应端的虚拟地址,通过响应端的地址翻译,获得最终响应端的内存地址。这三种操作在IB标准中被划分在了RDMA语义下,也被称为内存语义,但从上述分析来看,这里将RDMA语义称为内存语义,有一点概念放大的嫌疑。

下面我们对比的看看CXL是如何划分语义的:

CXL语义划分

CXL介绍了三大类语义,包括I/O语义,缓存协议语义和内存访问语义,即CXL.io, CXL,cache和CXL.mem。其中,CXL.io语义与PCIe语义类似。

CXL语义划分依据猜测

CXL提供了非常丰富的事务层操作,我们可以把CXL链路以及两端抽象成下面的模型:

下面我们看看CXL链路要支撑CXL Point A和B进行哪些交互,简单起见,我们只关注请求类型:

CXL.Cache

| Point A | CXL.T1/T2 | CPU L3 |

| Point B | CPU L3 | CXL.T1/T2 |

| x86指令 | N/A | Load/Store |

| 设备指令 | Load/Store | N/A |

| 请求类型 |

Read Read0 Write Read0-Write |

Snp* |

| 空间类型 |

主存 HDM-D HDM-H HDM-DB |

主存 HDM-D HDM-H |

| 内存属性 |

Cacheable Uncacheable |

Cacheable |

CXL.mem

| Point A | CXL.T2/T3 | CPU HA |

| Point B | CPU L3 | CXL.T2/T3 |

| x86指令 | N/A | MOV |

| 设备指令 | N/A | Load/Store |

| 请求类型 | BISnp* |

MemRd* MemWr* MemInv* etc |

| 空间类型 | HDM-DB |

HDM-D HDM-H HDM-DB |

| 内存属性 | Cacheable |

Cacheable Uncacheable |

CXL.io

| Point A | CPU Core | CPU Core | CPU Core |

| Point B | CXL.T1/T2/T3 | CXL.T1/T2/T3 | CXL.T1/T2/T3 |

| x86指令 | MOV | IN/OUT | MOV |

| 请求类型 | MRd/MWr | IORd/IOWr | CfgRd/CfgWr |

| 空间类型 | 内存空间->PDM | 64KB I/O空间 | 内存空间->配置空间 |

| 内存属性 | Uncacheable | N/A | Uncacheable |

| Point A | CXL.T1/T2/T3 | CXL.T1/T2/T3 | Host |

| Point B | Host | CXL.T1/T2/T3 | Host |

| x86指令 | N/A | N/A | MOV |

| 设备指令 | Load/Store |

Load/Store DMARd/DMAWr |

N/A |

| 请求类型 | MRd/MWr | MRd/MWr |

UIOMRd UIOMWr |

| 空间类型 | 内存空间-主存 |

内存空间->PDM 内存空间->GFAM |

内存空间->GFAM |

| 内存属性 |

Cacheable Uncacheable |

Uncacheable |

Cacheable Uncacheable |

什么是Load/Store指令?

通常来说,Load/Store(L/S)指令是处理器核对内存空间的访问操作,包括Load操作,将数据从内存空间读到处理器核内的寄存器中;以及Store操作,将处理器核内寄存器的数据写到内存空间中。

x86架构中,对内存空间访问的指令典型的是MOV指令;ARM架构中,对内存空间访问的指令典型的是LDR/STR;因为有不少的空间被映射(mapping)到了内存空间,即采用内存空间的访问指令,所以Load/Store指令不但能够访问实际的内存,也可以访问其他的一些设备,以及设备空间,例如BIOS ROM,南桥的寄存器,PCIe设备上的内存等等。

什么是DMA操作?

如果我们在两个物理地址间搬移数据,而不需要CPU介入的话,我们就称这种操作是DMA操作。这其中最重要的是DMA引擎,它具备一些寄存器接口,高级别的DMA引擎可能配备了硬件队列,用于描述搬移数据和地址的相关信息。从最终效果上来看,一次DMA操作等同于两次Load/Store操作,即先通过Load操作将数据从物理地址A读到DMA引擎,然后再通过Store操作将数据从DMA引擎写到物理地址B。

容易混淆的概念:

Load/Store是处理器的一种指令,例如x86的MOV指令,该指令会产生对内存空间的访问。现代计算机系统中,内存空间并不都指向具体的内存(DRAM)。也包括BIOS ROM,PCH寄存器空间,PCIe配置空间等,所以Load/Store最好说成是内存空间访问指令或语义。

内存空间访问和内存访问有什么不同?

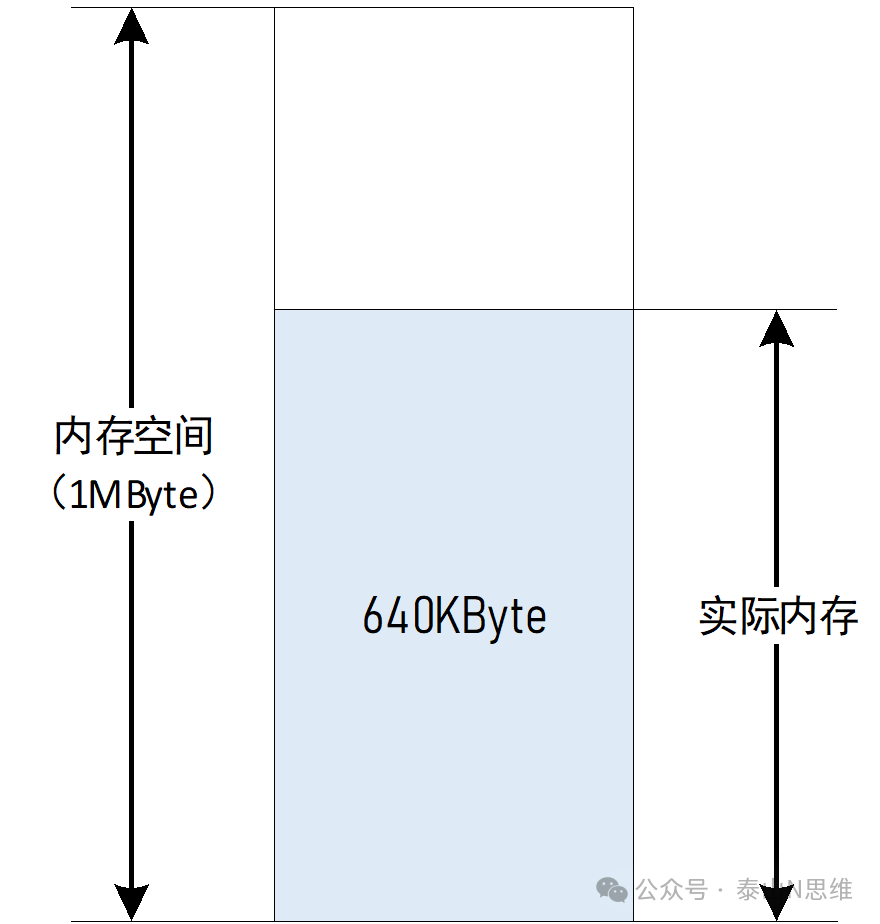

内存空间是指处理器通过遍历其地址线的排列组合,能够通过Load/Store指令访问的最大的物理地址空间。例如某款处理器的地址线能够支持1MByte的内存空间,但实际上内存只有640KByte,如下图所示:

我们以x86处理器为例,CPU可访问的主要空间包括:

| 处理器访问空间 | 处理器访问指令举例 |

| 内存空间(48-bit或者52-bit) | MOV |

| I/O空间 (16-bit) | In/Out |

| 配置空间 (28-bit) | MOV or In/Out |

| 其他空间(MSR,CPUID等) | RDMSR/WRMSR, CPUID ... |

其中,配置空间因没有独立的指令,访问该空间可通过I/O空间实现(Legacy方式,16M空间),也可以通过内存空间进行访问(256M空间),不同的空间将使用不同的指令进行访问。

结语

通过上面的分析可以看出,内存语义的定义在不同的上下文中的确不是特别固定。比较主流的观点有:

内存语义是指某种事务层的操作,其操作对象是具体内存实体的。该定义的代表是IB的RDMA语义。

内存语义是指专门针对内存实体操作的语义,与IO语义不同,这种上下文中的内存语义是不提供类似IO语义那样的保序操作。例如对于非同地址的内存读写操作,是没有序的要求。该定义的代表是CXL.mem。

术语:

PDM: Private Device Memory:传统PCIe设备上的内存资源,以及通过CXL.io访问的内存资源(CXL设备),该设备资源不支持Host Writeback操作

HDM:Host-managedDevice Memory:设备上的内存资源,该资源被映射在Host缓存一致性地址空间,该资源支持Host Writeback操作,包括HDM-D,HDM-H以及HDM-DB三种类型

HDM-D:HDM-DeviceCoherent:该内存可被CXL.cache或类似语义进行管理

HDM-H:HDM-Host OnlyCoherent:该内存只被Host使用并管理

HDM-DB:HDM-DeviceCoherent with Back-Invalidate:该内存被共享给了多个Host,并通过CXL.mem的Back-Invalidate通道进行缓存一致性维护

L/S:Load/Store:处理器对内存空间的访问操作,可操作实际内存,设备配置空间(MMCFG),设备资源空间(MMIO)等。

References:

PCIExpress Base Specification Revision 6.2

CXL_3.1Specification Release_FINAL.pdf

InfiniBand_Architecture_Specification_Volume_1_R1.7

审核编辑:黄飞

-

基于OWL属性特征的语义检索研究2010-04-24 1829

-

Verilog 硬件语义2015-10-18 3515

-

语义机器人2016-03-10 5673

-

求助:关于语义网本体构建,恳请大神帮忙2016-04-26 1935

-

NLPIR大数据语义智能分析平台先精准分词才语义分析2018-08-27 4626

-

NLPIR语义分析是对自然语言处理的完美理解2018-10-19 2945

-

IOT语义互操作性2021-07-27 1537

-

CXL内存协议介绍2022-11-01 3154

-

语义网详解2009-08-04 2992

-

基于语义向量表示的查询扩展方法的应用设计2017-12-12 836

-

基于语义的文本语义分析2017-12-15 1124

-

语义分割算法系统介绍2020-11-05 7892

-

PyTorch教程-14.9. 语义分割和数据集2023-06-05 1443

-

图像分割与语义分割中的CNN模型综述2024-07-09 3303

-

图像语义分割的实用性是什么2024-07-17 1618

全部0条评论

快来发表一下你的评论吧 !