高速串行I/O轻松实现,GTP/GTX工作原理详解

描述

关于作者

Abhijit Athavale

Abhijit Athavale是Xilinx公司连接功能解决方案部市场营销经理,其职责包括为公司的高速串行和并行连接功能产品完成战略开发、产品定位和营销计划。自1995年加入Xilinx以来,他担任过营销、应用和软件工程方面的多种职务。之前,Athavale曾任Meltron公司研发工程师之职,主要设计通信产品。他拥有印度旁尼大学电子工程学士学位和德克萨斯农业大学电子工程硕士学位。他是一名很有造诣的演说家和作家,发表了数篇论文。

I/O性能极限输入/输出( I/O)在计算机和工业应用中一直扮演着关键角色。但是,随着信号处理越来越复杂,I/O通信会变得不可靠。在早期的并行I/O总线中,接口的数据对齐问题影响着与外部设备的有效通信。并且,随着更高的传输速度在数字设计中日渐普及,对信号延迟的管理也变得困难重重。

针对I/O的数字设计解决方案数字电路设计者采用了一系列方法来提高信号速度和消除I/O问题。例如,采用差分信号处理来提高芯片间的通信速度。信号同步、源同步和自同步之类的设计方法改善了内部IC(集成电路)通信,在满足计算机行业所需速度的前提下,提供了可靠的输入/输出。

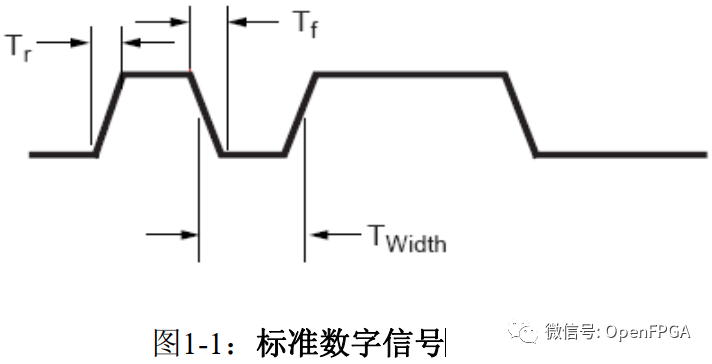

千兆位级串行技术介绍图1-1为典型的数字信号。

注意图中列出的时间测量值:

TR = 20 ps

TF = 20 ps

TWIDTH = 0.10 ns

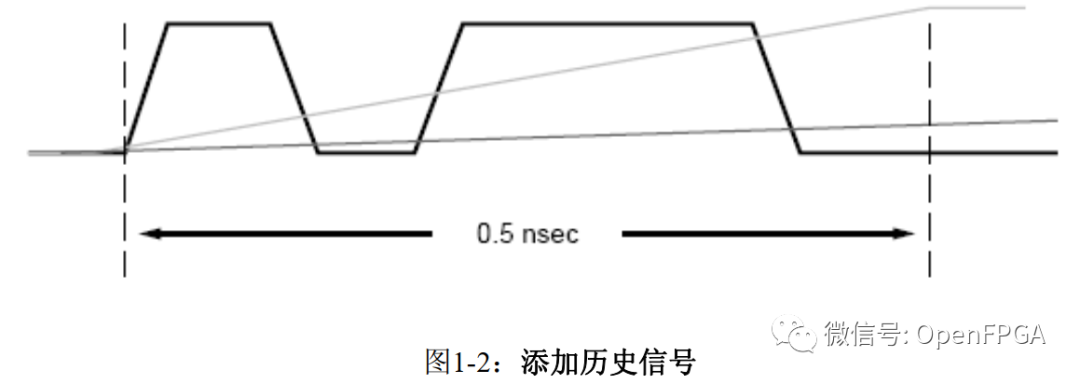

这些值描绘出了一个变化很快的波形。图1-2添加了作为参考的历史信号,以便说明该波形的变化有多快 。

大多数信号的上升时间甚至不能在这个信号的五个比特周期内结束。那么,为什么要讨论这个信号呢?因为它代表了数字 I/O 领域最热门的潮流——千兆位级串行通信。

这类信号在市场上引起轩然大波。它被广泛采用,从局域网( LAN)设备到尖端医疗成像设备,再到先进的战斗机技术,不一而足。千兆位级信号迅速成为延伸信息化时代的关键因素。为了解这一飞速发展的科技进步技术,让我们首先回顾一下I/O设计的历史。

设计考虑

通常设计工程师都处于进退两难的境地。一方面,他希望能坚持使用已经过验证的、可靠的解决方案,因为这些方案的结果可靠并能够预见。另一方面,他也必须努力改进各项参数性能,如:数据流、引脚数、电磁干扰(EMI)、成本和背板效率等。那么,他会考虑使用千兆位串行输入/输出(I/O)吗?

千兆位串行I/O的优势

千兆位串行I/O的主要优势是什么?答案是:速度。在从片内/片外、板内/板外或盒内/盒外获取数据时,没有什么技术可以超过高速串行链路。这种技术的线速范围为1Gb/s~12Gb/s,有效负载范围为0.8Gb~10Gb,因此可以进行大量的数据传送。由于引脚数较少、没有大量的同时开关输出(SSO)问题、 EMI较低且成本较低,所以高速串行就成为了理所当然的选择。当需要进行大量数据的快速传输时,使用千兆位级收发器(MGT)是个不错的方法。让我们首先分析一下千兆位串行I/O的优势。

MGT:千兆位级收发器——千兆位级串行器/解串器(SERDES)的别名。接收并行数据,并允许在串行链路上进行大带宽数据传输。

最大数据流

某些大型可编程逻辑器件具有20个或更多个10Gb串行收发器,可以实现总带宽为200Gb/s的输入和输出。不过那只是极端情况,我们来看一个应用实例,它向我们展示了串行I/O的速度是如何帮助系统架构师、电路板设计师和逻辑设计师的。

缺点是什么?

在我们认为千兆位级串行I/O技术出色的近乎不真实之前,来看看它的弊端吧。设计中,首先我 们必须密切注意信号完整性问题。例如,有个供应商报告说,他们第一次试图将高速、千兆位级串行设计用于某种特定应用时,失败率为90%。为了提高成功率,我们可能需要进行模拟仿真,并采用更复杂的新型旁路电路。事实上,我们甚至需要对旁路电路进行仿真和建模。而且,阻抗控制的 PC(印刷电路)板、高速连接器和电缆的费用较高。我们必须处理数字仿真中的复杂性和时基较小的问题。并且,在利用预设协议的时候,必须为集成过程计划时间,并且为协议的开销安排额外的逻辑电路或 CPU 时钟周期。

千兆位I/O用于何处?

起初,千兆位级串行器/解串器(SERDES)仅局限于用在电信行业和少数缝隙市场(如广播视频)。如今, MGT应用出现在电子行业的各个角落——军事、医疗、网络、视频、通信等等。

MGT也可以用于背板或机箱之间的PCB上。对于电子行业的发展前景而言, MGT至关重要。下面是采用千兆位级SERDES的行业标准示例。

• 光纤通道(FC)

• PCI Express

• RapidIO串行

• 先进交换互连(Advanced Switching Interface)

• 串行ATA

• 1-Gb以太网

• 10-Gb以太网(XAUI)

• Infiniband 1X、 4X、 12X

芯片到芯片SERDES最初用于盒间通信。但是,因为它能出色地处理同一块电路板上的芯片间通信,因而在市场上引起了轰动。先前,芯片间通信仅采用并行技术。用于串行化和解串行化的逻辑门数量远远超过了因引脚数目减少而节省的逻辑门数量。

但是,采用深亚微米结构,就可以在极小的芯片上获得数量惊人的逻辑门电路,从而使SERDES也能够以极低的芯片成本实现。除此之外,对I/O带宽日益增长的需求使得SERDES迅速成为进行芯片间大量数据传输的合理选择。使用SERDES进行芯片间通信具有如下好处:

• 引脚数:更小、更经济的封装。

• 引脚数:PCB层数减少。

• 更小的封装:电路板更小、更经济;设计更紧凑。

• SSO:较少的引脚和差分信令消除了SSO问题。

• 功耗:通常,高速串行链路的功耗要小于并行链路。这一特点在一些有源偏置/终端的高速并行标准,例如高速晶体管逻辑(HSTL)中尤为明显。

• 内含控制线路:通常,并行接口除了数据线外,还需要一些控制线和使能线。大多数协议下使能和控制性能都可以嵌入到串行链路中。

还是老规矩,原文很长 很长 很长。。。。

链接: https://pan.baidu.com/s/1K0AVtbrwTJ7SzXbwnUWTWQ

提取码: jx35

审核编辑:黄飞

-

FPGA设计之GTP、GTX、GTH以及GTZ四种串行高速收发器2020-11-20 22403

-

RocketIO高速串行接口2014-03-01 3549

-

问一下路过的FPGA大神,ADI的参考设计用的高速通道是GTX,GTH,怎么移植到高速通道是GTP的FPGA里?跪求!!!2018-05-07 5616

-

轻松实现高速串行I/O (FPGA应用设计者指南)2020-01-02 5424

-

轻松实现高速串行IO2020-01-28 3250

-

MGT,GTP,GTX之间的区别是什么?2020-03-10 3487

-

在Virtex-5/6 GTP / GTX收发器中如何实现JTAG2020-06-18 1932

-

请问GTP和GTX兼容吗?2020-07-31 2520

-

如何利用FPGA中的高速串行I/O去实现嵌入式测试?2021-04-13 2364

-

怎么实现RocketIOTM GTP在串行高速接口中的位宽设计?2021-05-28 1507

-

RocketIOTM GTP在串行高速接口中的位宽设计2010-07-22 478

-

实现千兆位串行I_O的相关技术2012-04-01 1148

-

Virtex-7 2000T GTX收发器实现高速串行性能2018-11-22 4654

-

基于Virtex-5 RocketI0TM GTP收发器实现串行高速接口的开发应用2021-06-24 4174

-

GTX/GTH/GTY/GTP/GTZ/GTM有什么区别2022-08-02 11042

全部0条评论

快来发表一下你的评论吧 !