深入赛灵思Kintex-7 FPGA内部:透视HKMG技术

PLD技术产品创意

描述

电子发烧友网讯:终于逮到机会评估前沿高端新技术。在众多的革新性工艺技术中,赛灵思和台积电首次将高K金属栅极(HKMG)技术应用到FPGA中尤其是其中的佼佼者。现在就让电子发烧友网带领大家从赛灵思的工艺革新发展历史到目前代表行业领域最高科技的Kintex-7 FPGA内部架构,这是令人兴奋的一次高科技之旅。

赛灵思的工艺革新史

赛灵思早在1984年就利用无晶圆商业模式制造出赛灵思首颗芯片,代工厂商为Seiko 和 Monolith。当他们从65nm工艺节点转入较低节点时,赛灵思和UMC, Samsung 及Toshiba 寻求合作生产 FPGAs。直到现在,赛灵思采用台积电的HKMG工艺不但用于领先的FPGAs的Kintex-7系列产品,也囊括了很多其他即将来临的产品设备,包括Artix-7和 Virtex-7 FPGA系列和Zynq-7000 EPP系列。这一决定将赛灵思所有产品推向进入到28nm节点时代。

FPGAs 产品家族的Kintex-7系列采用了台积电28nm高性能低功耗(HPL)工艺节点技术来进行设计封装制造,为客户提供低功耗和高性能体验。它的市场战略目标为下一代广播电视点播系统和下一代无线网络等等应用领域。

Kintex-7组件能被配置到支持多空中接口,如LTE, WiMAX, WCDMA以及为PCI Express (Gen1/Gen2)提供八通道内置设计需求。Kintex-7 FPGA家族拥有领先的可扩展赛灵思架构,可对前一代产品(40-nm) Virtex-6 FPGAs进行简便地移植使用。

谈及到移植的问题,众多的晶圆厂从65-nm节点的主要基于多晶硅门和应变工程过渡到到高K金属门栅极绝缘层,伴随着技术难度的加大和高成本,每次过渡都充满着潜在性危险。

回首HKMG工艺技术,Intel凭借45-nm后栅极工艺最先进入到金属门。台积电是第二个晶圆代工厂能提供后栅极金属门工艺的厂商。Intel的竞争者——AMD,直到现在才为其32-nm工艺节点引进后栅极金属门工艺,据信,这是因为日本松下公司为其首次金属门工艺采用金属门重叠多硅结构。

赛灵思选择较为简单的HKMG工艺降低来自高功耗(HP)或低功耗(LP)28nm工艺所带来的风险。选择高性能,低功耗(HPL)HKMG技术可有效规避产量和漏电等异常事件发生。

选择HPL方案,赛灵思可以更好的在进行FPGA设计时处理复杂和昂贵的静态电源管理方案,使得能专注于开发具有统一标准的7 系列 FPGAs架构(如Artix-7 和 Virtex-7)。这些统一的架构为开发者带来了许多好处,在FPGAs家族中不同的产品中可向上或向下移植兼容,客户代码和IP及普通模块(RAM, DSP, I/O,时钟,互连逻辑,存储器接口)复用。

深入赛灵思Kintex-7 FPGA内部

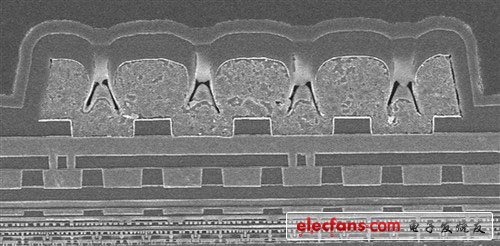

台积电的HPL NMOS 和 PMOS晶体三极管在Kintex-7 FPGA中,如下图所示。两个晶体管被用作后栅极工艺,TiN/HfO2/oxide栅极绝缘层被堆积在第一层。

台积电HPL NMOS (左) PMOS (右)

多晶硅被剥离,不同的金属门被堆积到NMOS和PMOS门区域。

Kintec-7 FPGA门布局设计

高逻辑密度为Kintex-7 FPGAs设计的一大特色,内部设计为478,000个逻辑单元。其他特色包括:三十二个串行传输速度高达12.5 Gb/s高性能连接收发器,34Mb RAM和1,920 个DSP分割区,DSP性能高达2,845 GMACS以及16通道双通道12位多相串行ADC。

——电子发烧友网版权所有,转载请注明出处!

-

Kintex-7 FPGA数据表下载2021-05-21 1015

-

使用Kintex-7 FPGA实现最佳的每瓦性能2018-11-28 3579

-

全球第一款28nm产品— Kintex-7 FPGA的 10Gbps 眼图演示2018-06-05 5386

-

Xilinx赛灵思FPGA技术及应用线上公开课2017-04-10 3965

-

Chipworks拆解基于台积电28nm HPL工艺的赛灵思Kintex2017-02-11 3745

-

基于赛灵思Kintex-7 FPGA设计或硬件原型的快速部署方法2017-02-10 2664

-

7系列FPGA芯片-赛灵思的“雄韬伟略”2012-09-21 15488

-

选择赛灵思(Xilinx)FPGA 7系列芯片的N个理由2012-09-06 4417

-

全新赛灵思(Xilinx)FPGA 7系列芯片精彩剖析2012-08-08 3648

-

赛灵思Kintex-7 FPGA 系列芯片简介2012-06-12 17106

-

WP373-赛灵思推出Virtex-7,Kintex-7,Artix-7三大全新系列FPGA2012-01-17 1584

-

Xilinx推出基于28nm Kintex-7 FPGA 的全新目标参考设计和全新开发基板2012-01-09 2034

全部0条评论

快来发表一下你的评论吧 !