易灵思Jtag_bridge_loader生成-v2

易灵思Jtag_bridge_loader生成-v2

描述

Efinity版本:2023.1及以前版本。

易灵思器通过jtag bridge烧写flash时需要自己生成一个jtage birdge文件。jtage bridge 工程的目的是为了打通JTAG与flash的连接。

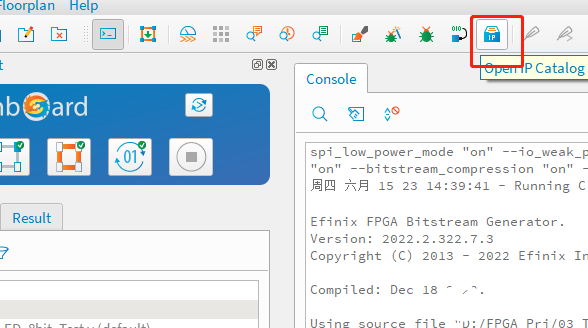

(1)打开IPM

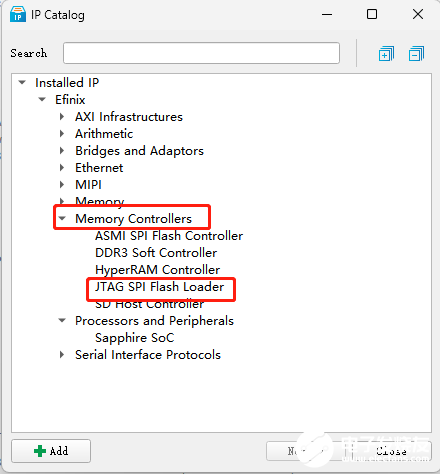

(2)选择Memory Controllers --> Jtag spi flash loader

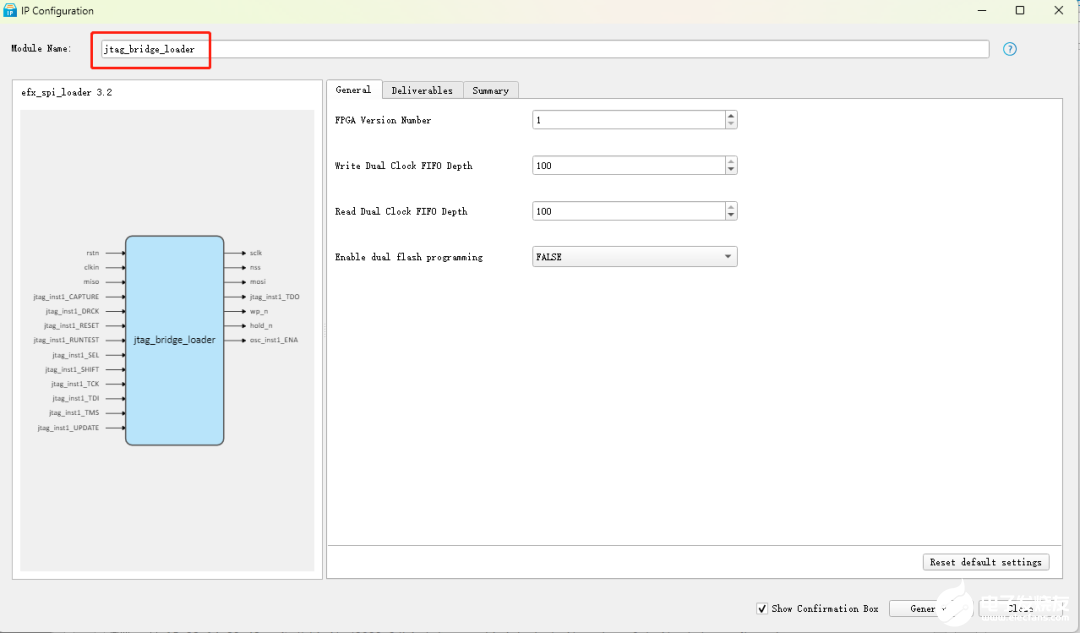

(3)随便命个名。可以考虑把fifo深度加大。

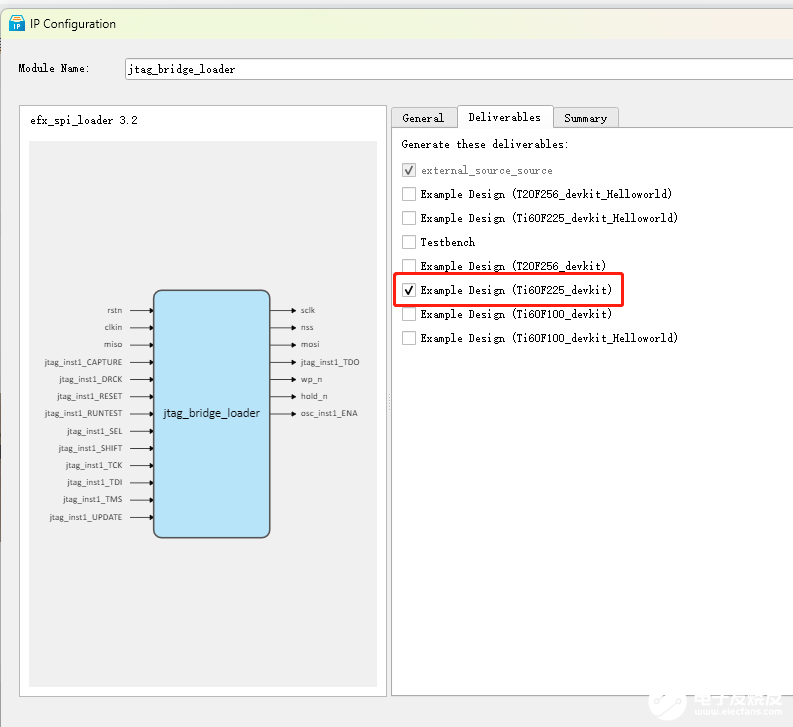

(4)在Deliverables界面根据自己的需要选择相应的demo,如果没有找到自己想用的器件就选择相近的生成之后自己修改器件 。

(5)生成IP之后,会在IP目录文件夹下生成一个example design,打开该工程。

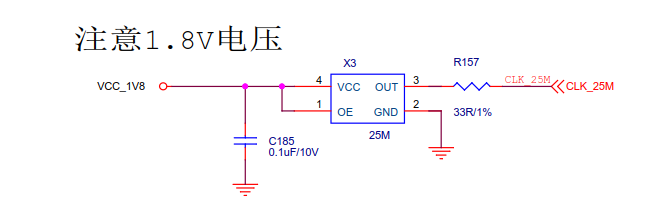

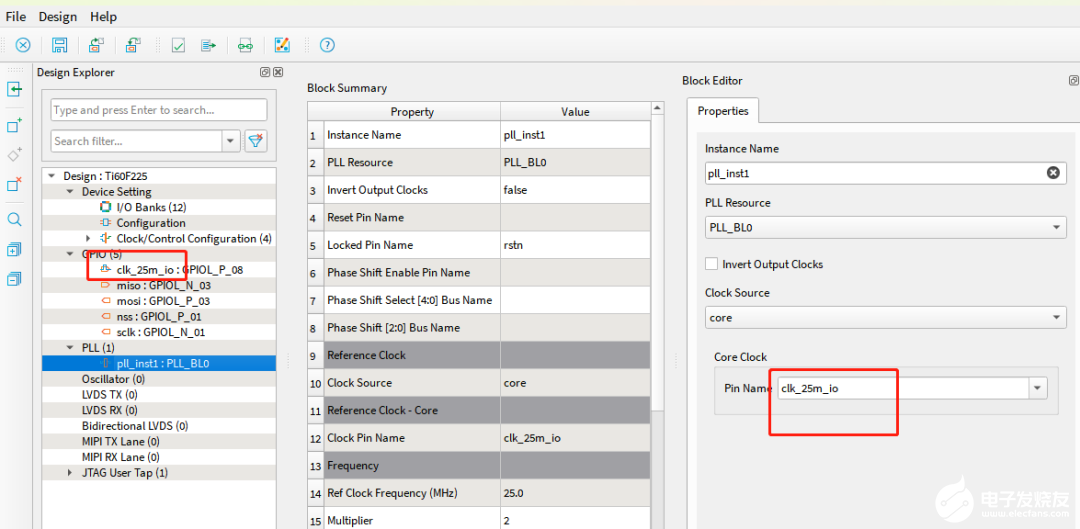

这里需要说明的是,如果是Trion系列FPGA因为没有片内晶振,所以需要外部提供,这时要打开interface Designer然后自己指定电路板上提供的时钟。比如在demo板上有一个外挂25M晶振,参考用法如下图。

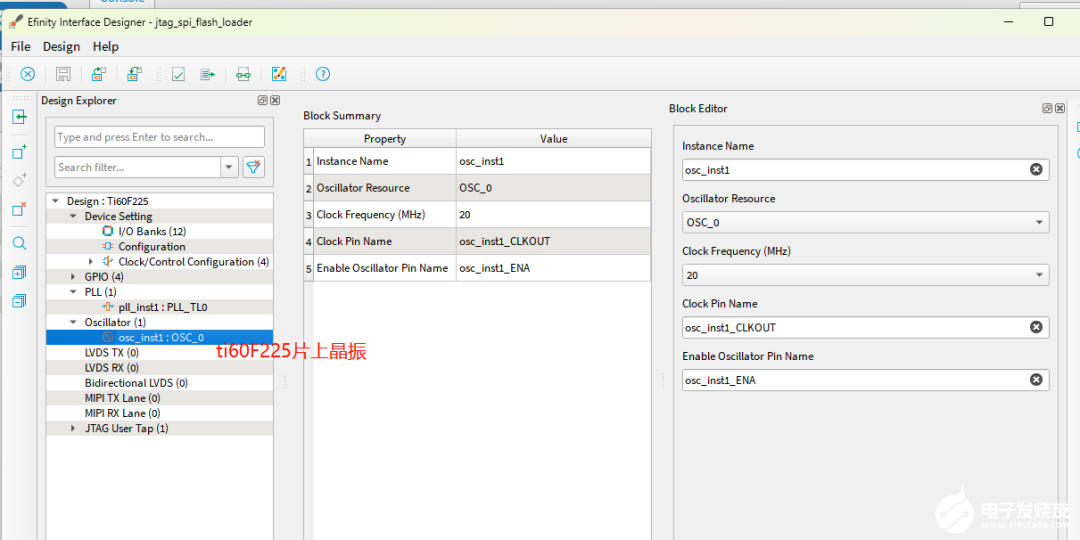

如果是钛金系列,可以使用片上晶振可以用作PLL的参考时钟,生成demo时也是默认使用片上晶振。所以只在编译即可使用。

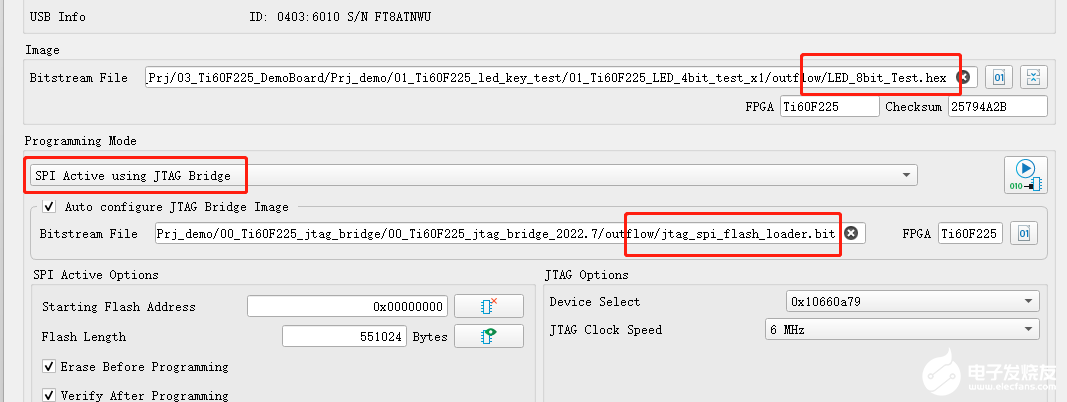

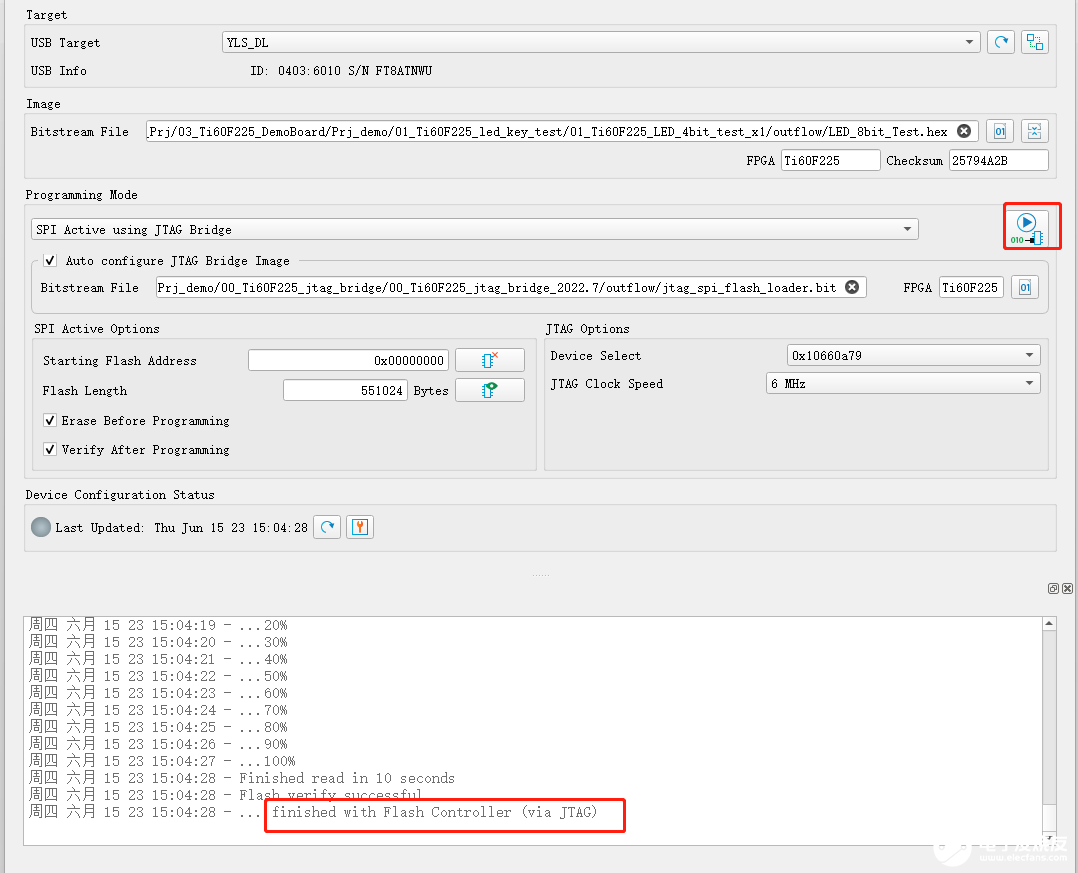

(6)配置程序时,选择SPI Active using JTAG Bridge。在Auto configure jtag bridge Image栏选择生成的bit文件。上面的Image栏选择自己的工程hex数据流。

(7)烧写。点击start,烧写完成后会提示finished with Flash Controller(via JTAG)表示烧写成功。

Efinity版本:2023.2

可能有人在想为什么别的厂家的烧写的时候不需要生成bridge文件呢,那是因为他们已经提前做好了。在2023.2版本及以后易灵思也对钛金器件进行了相应的支持。

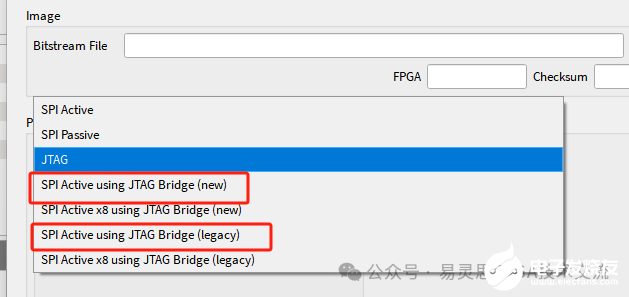

打开programmer,并选择Programming Mode可以看到,2023.2已经支持Jtage Bridge(new)和(legacy)两种方式,其中legacy方式就是指2023.1及以前的版本的使用的方式,需要自己生成bridge工程。而new这种方式是易灵思内部提供了相应的bridge文件,以我的电脑为例,在C:Efinity2023.2pgmflititanium路径下。而且客户只要选择new这种方式软件也会默认自动选择对应器件的bridge文件。而且这种方式的birdge文件烧写程序的速度要比lgeacy方式的快很多。

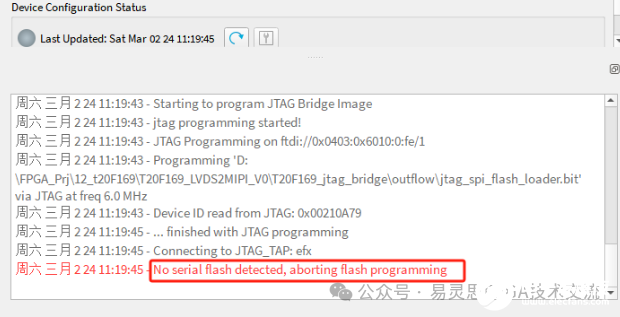

另外有一点要强调一下,是否可以用2023.2自带的birdge文件用于老版本的烧写从而把速度提上来呢?结论是不行的。如果这样操作就会报No serial flash detected,aborting flash programming的错误。

对于trion器件,因为没有内部晶振的原因,所以必须要指定外部时钟管脚,所以暂时还没有提供相应的工程。

打完收功,操作比较简单,不啰嗦。如有问题欢交流。

-

易灵思下载器驱动安装-v22024-10-16 3065

-

易灵思JTAG写入Flash工程的创建过程和烧写操作2022-03-09 7320

-

Kinect v2(Microsoft Kinect for Windows v2 )配置移动电源解决方案2022-01-05 889

-

微雪电子ST-LINK/V2 STM32仿真器简介2019-12-20 11581

全部0条评论

快来发表一下你的评论吧 !