可处理高数据率的创新型串行总线测试方法

高速串行测试

描述

目前高性能集成电路方面正在发生的架构改变将影响半导体产品的方方面面,包括从设计到终测和封装。这一变化背后的驱动因素有两个:(1)不断增加的数据带宽需求;(2)功率管理方面的需求。这两方面的需求正在驱使设计师对出入IC的数据传输方式作出根本的改变。

设计工具和制造工艺已经改进到可用逻辑门数量已经不再是片上系统(SoC)性能的限制因素了。相反,性能限制因素主要是向芯片“内核”传送数据的速度,以及功率管理和热管理。过去,可以通过增加并行总线带宽来传送较大的数据量,但这种方法在功耗、引脚数量、封装以及PCB成本等方面都有缺点。

实际上由于互联层之间的电容和电感特性,在现有的并行总线上传输高速数据时还面临一些其它限制。当线上的数据率高达约1Gbps时,上升时间、抖动、通道间和分布式时钟摆率特性等这些并行总线设计中固有的问题将开始成为关键的限制因素。

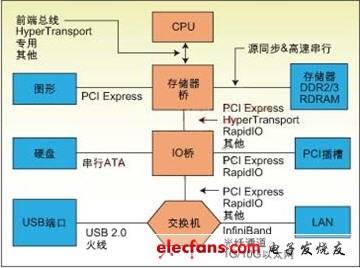

这些限制因素激励着数据通信领域的数字设计工程师门在十年前就开始考虑串行技术。通过在为数不多的串行信道(图1)上实现非常高的数据率,他们发现数据量和功率预算要求都能得到满足。高速串行总线(HSSB)的很多物理性能与并行总线不同。主要的差别包括:

对于发送和接收等量的数据来说所需的连接点数量更少

串行总线为点对点连接,而传统的并行总线则是多点对多点连接

串行总线为单向的数据通道,而传统的并行总线则是双向

串行总线的电压摆幅小,可以支持更高速率的数据传输

串行总线采用差分信号,克服了影响低电压摆幅的共模噪声

与传统的并行方式相比,串行的定时和数据捕获方式有根本不同

图1:采用高速串行总线的PC架构。

高速测试方面的挑战

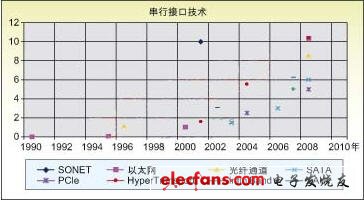

在以不是太高的成本通过HSSB提供这些呈指数式增长的传输速率方面测试公司将扮演关键的角色。像PCI Express I和II、HyperTransport 2.0和3.0、XAUI、XDR、RapidIO以及 InfiniBand这些高速接口将被越来越多地用来提供更高的数据率(图2)。但是,高速数据总线带来了一些很大的测试挑战,在这里,传统的功能测试和简单的可测性设计(DFT)方法学不再适用。在高端自动测试设备(ATE)平台上的传统“功能”测试流程能够提供很全面的测试覆盖,但这些经过生产验证的方法存在较大的缺点,比如成本较高,测试编程复杂。此外,每个引脚的成本随着高速数据应用中总线速率的升高而升高,这也使得传统的功能测试方法渐不可行。

图2:到2010年数据率将超过10 Gbps,因此测试行业需要创新的测试方法来克服高速总线方面的挑战。

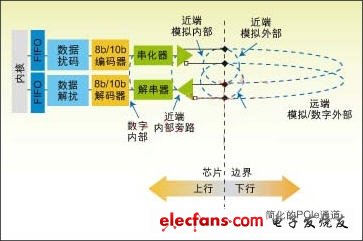

于是制造商们又转向能够实现更全面和成本优化的高速总线测试的环回技术(即:利用设备本身提供测试数据然后接收返回到设备的数据进行确认)。图3 给出了一个简化的PCI Express通道以及可能不同的环回位置,从有助于晶圆探测的纯内部环回点,到被测器件(DUT)外面的环回位置。环回测试非常有效,不过实现的方式也非常重要,因为要考虑高速信号的典型损耗预算。损耗预算决定了可接受的信号劣化的程度,它通常需要考虑三个因素,即发射器,接收器和内部互联,所有这几项都将劣化信号的“眼图”,从而影响测试覆盖率。

图3:在简化的PCI Express单通道中可能的环回位置。

迄今为止,像“近端环回”这类替代性DFT技术已经为高端消费电子和运算应用方面的测试设备带来了良好的成本效益(通过ATE中的简化编程和降低投资)。目前的近端环回技术简单并具成本效益,不过在解决像抖动、信号变化以及导致测试不完整甚至漏测的协议性能等问题方面却无能为力。近端环回技术可以通过在I/O引脚之间创建通路而被设置到被测器件中。但是,在覆盖率方面,其固有的低成本和简单性将大打折扣。它没有参数测量,缺乏信号控制,具有较低的与信号完整性或误码相关的故障发现概率等。例如,一个简单的内部环回,或负载板环回,将使一个边际接收器“隐藏”在强健发射器的阴影中,并通过环回测试。在较低的速率上都存在这些不确定性的时候,如果许诺3Gbps以上的覆盖率将是冒险的方式。于是,半导体制造商需要寻找新的DFT技术来对影响器件和系统性能的关键变量实现灵活全面的测试。

远端环回的优点

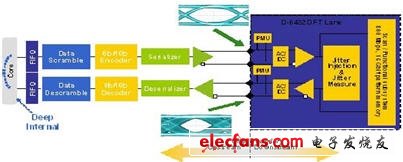

处于两种极端之间,像远端环回这样的创新技术将DFT的灵活性与较深入的功能测试诊断结合在一起。这种远端环回在Credence Systems公司的Sapphire D-6432DFT仪器中得到了有效实现。Sapphire D-6432DFT仪器是业界首套高速串行总线方面的集成测试解决方案。该方案结合了全速环回测试、抖动测量、注入测量,还有扫描/功能测试以及直流参数测量,所有功能都位于一个单独的插件中。更好的是,它提供了带有可编程信号劣化功能的远端环回,这为测试工程师赋予了很大的灵活性,使得他们可以将DUT DFT/图形产生器插入到尽可能远的上游端。其结果是实现了更高的测试覆盖率(与其他环回方法相比)。图4中显示的是利用DUT主图案(master pattern)产生器在一个单独的PCI Express通道上的一个简单实现,其中D-6432DFT提供远端环回。

图4:利用内部DUT DFT实现数据包产生、带可编程信号劣化功能的远端环回可以完成高速通道的端到端测试。

D-6432DFT提供了比同类产品高四倍的密度,为制造商提供了一项突破性的DFT方法,从而大大减少了半导体器件的总成本和上市时间。与需要数倍投资却仅能测试有限几个通道的其他方案不同,D-6432DFT整合了大量的功能,可以在一台仪器上测试多达16个环回对。这套仪器是与微处理器制造商Advanced Micro Devices (AMD)公司合作制造的,该公司的工程师们将获奖的Sapphire平台与D-6432DFT整合在一起,加快了该公司最新型产品的测试时间和上市时间。各地生产线上在用的D-6432DFT仪器已有200多套,这些仪器基于验证过的Sapphire平台,其全球用户数量已达上百个。

利用D-6432DFT可以使DUT与智能的测试设备通信,从而首次实现了高速总线的生产级测试。测试工程师在编程信号劣化性能以便器件的发射和接收通道留出更多余量方面具有很大的灵活性,还能够在一个具有成本效益的生产环境中实现抖动容差和抖动传输方面的测试。

这类环回提供了以下一些重要优点:

提供了能够侧重电压和时间域眼图的信号控制

增加了对信号完整性和误码灵敏度的测试覆盖

仪器中整合了抖动注入和抖动测量

覆盖了损耗预算所有的三个部分

接收和发射通道可以被用来向内核逻辑和协议栈提供测试向量

可以访问器件引脚实现全面的直流参数测试

很明显,呈指数式增长的总线速度给电路板的设计到生产带来了根本转变。重要的是要记住绝大多数器件都还有其他一些信号,甚至符合传统接口标准的其它总线。一些器件同时使用几种由不同协议和信令规范支持的高速总线已经是常见的事情了。实际上,正是技术和时间域的结合才使得这些器件功能如此强大,也使设计、调试和测试变得更加困难。在快节奏环境中,通过提供创新产品和解决方案来帮助用户以更低的成本和更低的风险进一步优化和加速他们的最新测试技术,测试公司将扮演重要的领导角色。

- 相关推荐

- 热点推荐

- 串行总线

-

微处理器设计中集成串行总线的特性及比较2019-01-02 4786

-

基于USB总线的高速数据采集系统2009-04-11 20295

-

解决多总线系统级芯片测试问题的方法2009-10-13 4424

-

基于LabVIEW的CSDB总线信号测试2012-09-28 2716

-

通用SPI总线的FPGA实现方法2019-05-05 2000

-

测试蓝牙增强数据率产品的创新解决方案2019-09-11 1550

-

通用总线仿真测试系统2019-12-02 2157

-

高速串行总线的常用测试码型2011-01-04 4851

-

MCU低成本测试的数据串行压缩传输方法2011-09-01 664

-

串行总线的触发和分析2011-10-06 2780

-

一种新型的动态可重构总线时间同步方法2017-01-07 778

-

串行总线是什么?(优点和作用)2017-11-13 27089

-

通用串行总线USB技术演进及测试方案2021-03-30 980

-

并行总线和串行总线的区别2023-12-07 5764

-

使用低速串行总线的实时ADC原始数据采集方法2024-09-27 564

全部0条评论

快来发表一下你的评论吧 !