高介电常数栅电介质/金属栅极的FA CMP技术

EDA/IC设计

描述

高介电常数栅电介质和金属栅极技术(以下简称HKMG)使摩尔定律在45/32纳米节点得以延续。目前的HKMG工艺有两种主流整合方案,分别是“先栅极”和“后栅极”。“后栅极”又称为可替换栅极(以下简称RMG),使用该工艺时高介电常数栅电介质无需经过高温步骤,所以VT偏移很小,芯片的可靠性更高。因此业界在制造高性能芯片时更倾向于选择RMG工艺。然而,RMG工艺流程涉及更多的工艺步骤,面临更多的工艺难关和设计限制。难关之一就是平坦度极难达标。

典型的RMG工艺流程依次包括(图1):临时多晶硅栅极结构的形成,第一层间电介质(ILD0)氧化硅的沉积,ILD0化学机械研磨直至临时多晶硅栅极完全曝露,刻蚀去除多晶硅栅极,功函数材料的淀积,金属铝的沉积,以及金属铝的化学机械研磨。作为RMG工艺流程步骤之一,ILD0化学机械研磨对于HKMG结构的顺利形成至关重要。

由于栅极结构对尺寸控制要求非常严格(WIW和WID),如果缺少严格控制最终研磨厚度的工艺手段,将会带来一系列的工艺整合问题,比如:栅极电阻波动,栅极填充不足,源/漏极曝露等等。这些问题最终都会损害芯片性能。为了确保芯片的优良性能和可靠性,制造工艺必须严格控制WIW、WID以及WTW的厚度差异。

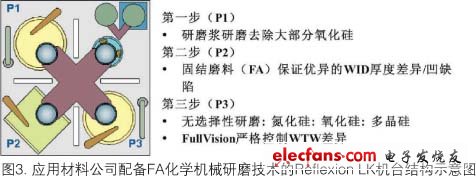

应用材料公司已经成功研发出一套在Reflexion? LK机台上实现的三步化学机械研磨工艺,以解决ILD0化学机械研磨过程中的WIW、WID和WTW厚度控制问题。第一步(P1),研磨移除大部分的ILD0电介质材料;第二步(P2),采用FA继续研磨,接触到栅极区域氮化硅层后停止;第三步(P3),栅极区域的氮化硅层被彻底磨掉,多晶硅栅极完全曝露。图2演示了在ILD0化学机械研磨过程中,沟槽区氧化硅研磨去除的全过程。

实验细节

应用材料公司的Reflexion? LK研磨机台包括一个FA研磨盘和两个标准的旋转式研磨浆研磨盘,使用可以控制5个独立区域压力的Titan ContourTM研磨头(图3)。FA研磨盘配有3M公司生产的SlurryFreeTM 固结磨料卷轴和SlurryFree P6900基底研磨垫。研磨浆研磨盘配有Dow Chemical公司生产的IC1010TM研磨垫和3M公司生产的研磨垫修复刷。P1使用Cabot公司生产的Semi-SperseR SS-12氧化硅研磨浆;P2使用FA研磨液;P3使用专用的研磨浆。

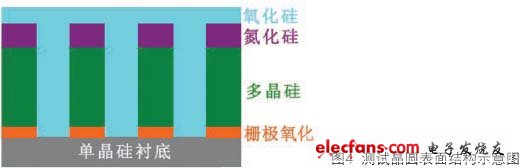

本文将统一使用一种简化的栅极结构(图4)以评估不同工艺的表现。栅极区域结构从上到下依次为:氧化硅/氮化硅/多晶硅/栅极氧化物/单晶硅,“沟槽”特指栅极与栅极之间的区域(结构为:氧化硅/单晶硅)。在尺寸大于50微米的测量区,薄膜厚度的测量使用Nanometrics公司的NanoTM 9010b。而对栅极尺寸小于100纳米的测量点,则需要通过扫描电子显微镜(SEM)进行纵切面观测。本文中,一部分样品通过机械劈裂的方式获得晶圆纵切面;另一部分样品使用聚焦离子束(FIB)局部切割晶圆露出纵切面。

结果与讨论

P3需要无选择性的研磨浆

因为P3之后的平坦度要求非常严格,P3的研磨倾向于使用无选择性研磨浆。该研磨浆在氮化硅、氧化硅和多晶硅上都有可观的磨率。首先,氮化硅的磨率必需足够高才能保证多晶硅栅极完全曝露。如果氧化硅的研磨率显著低于氮化硅和多晶硅,则可能导致沟槽区域明显凸起,并随着过度研磨而恶化。如果多晶硅的研磨率显著低于氮化硅和氧化硅,那么栅极和沟槽之间的高度差会对研磨不足或过度研磨非常敏感。使用无选择性的研磨浆将会减少由于P3研磨时间不同造成的栅极和沟槽之间的高度差变化。

P2 FA工艺可以降低P3之后沟槽氧化硅的WID厚度差异

FA工艺已被广泛应用于直接研磨浅沟槽隔离(STI)。FA可以选择性的停在氮化硅表面,并展现出优异的研磨平坦度和低的凹缺陷。与STI类似,ILD0的研磨也包括停在氮化硅表面的步骤。这种极低氮化硅损失和极低氧化硅凹缺陷的工艺特点使得FA成为ILD0研磨工艺中WIW和WID厚度控制的关键。在栅极密集区,由于特征尺寸很小,不论使用FA工艺还是高选择性的研磨浆(HSS)研磨工艺,凹缺陷一般都比较低(图5)。然而在外围区域,特征尺寸可能达到50微米以上,HSS研磨工艺一般都会产生明显的凹缺陷(>200?),而FA研磨工艺仍能保持低凹缺陷(<50?)。

因此,对比FA工艺和HSS工艺研磨后的沟槽氧化硅WID厚度差异,前者明显低于后者。由于P3使用无选择性的研磨浆,P2之后的高凹缺陷就会直接导致P3之后的沟槽氧化硅WID厚度差异也很高(图5)。从晶圆纵切面的SEM照片中可以清楚的看出P3之后的WID厚度差异。

FA优异的平坦度和凹缺陷表现

与HSS工艺相比,FA工艺能够明显降低沟槽氧化硅的WID厚度差异和凹缺陷,尤其在大特征尺寸区域。与此同时,FA过度研磨不会显著降低WIW和WID表现(图7)。图6对比了FA和HSS工艺在不同特征尺寸下的凹缺陷表现。当特征尺寸达到50微米时,凹缺陷的表现就会有明显差异。FA优异的凹缺陷表现使其成为RMG ILD0化学机械研磨工艺的关键步骤。

P2对于P3工艺的影响

图8-11中,所有SEM照片的拍摄角度均为45度。晶圆纵切面通过FIB切割方式获得。所有的照片使用相同的比例尺。图8比较了P2用HSS工艺研磨后的栅极密集区和200×200微米测量点的沟槽氧化硅厚度。栅极密集区和大尺寸测量区的厚度明显不同,表明存在显著的WID差异。P3的无选择性研磨浆工艺将很难修复P2造成的WID差异。如图9所示,如果P2使用HSS工艺,栅极密集区和大尺寸测量区的沟槽氧化硅厚度差异在P3之后仍然会很高。

相对于HSS,FA研磨后的WID厚度差很小。图10显示沟槽氧化硅在密集区和大尺寸测量区的厚度非常接近。这种低WID差异会被进一步保留至无选择性的P3之后(图11)。上述对比显示,FA有能力解决线路密度和尺寸不同造成的平坦度挑战,从而减少芯片设计规则中对于线路密度的限制。

用FullVision控制多晶硅厚度

持续稳定的多晶硅厚度控制是通过FullVision实时终点控制系统来实现的。该系统的可靠性和可重复性已在实际生产中得到证明。图12显示出FullVision终点控制系统的强大功能。在图12中,晶圆A和B都使用标准P3工艺研磨,并利用FullVision控制研磨终点;晶圆C和D的P3磨率低于标准磨率10%;晶圆C通过FullVision控制研磨终点,而晶圆D的研磨时间与晶圆A和B的研磨时间相同。上述四片晶圆的P1和P2研磨条件完全相同。

FullVision自动调整晶圆C的研磨时间来补偿P3磨率的下降。因此,晶圆A、B和C在P3之后的栅极多晶硅厚度差异小于5?。由于晶圆D没有使用FullVision终点侦测控制系统,而是使用与晶圆A相同的研磨时间进行研磨,因此晶圆D在P3之后的栅极多晶硅厚度与标准工艺条件的平均厚度相差高达25?。

使用无选择性的P3研磨浆会使工艺本身对P3磨率随研磨垫寿命的偏移以及上游步骤工艺的变化(比如氮化硅厚度改变,P2过度研磨程度等)非常敏感。FullVision可以通过自动调节研磨时间来应对生产过程中各种无法预测的偏移,从而确保稳定的WTW表现。

无论是在栅极密集区还是在大尺寸测量区,图13中的SEM纵切面图片都展示出均一的表面形貌。

结论

良好的WID、WIW和WTW厚度控制是制造基于HKMG技术的高性能逻辑芯片的关键。ILD0化学机械研磨工艺利用FA对不同尺寸大小和密度的芯片结构均提供优异的表面形貌和平坦度控制,并且通过使用FullVision实时终点控制系统进一步确保稳定的WTW厚度控制。

-

介电常数对雷达液位计的影响2025-01-28 1415

-

相对介电常数与介质损耗的关系2025-01-10 3543

-

介电常数的定义及应用 不同材料的介电常数比较2024-11-25 24810

-

影响介电常数的因素有哪些?2024-02-25 11981

-

相对介电常数和介电常数的关系2024-01-14 19356

-

介电常数用什么仪器测量?2023-03-24 2405

-

相对介电常数越大代表什么2021-08-10 36556

-

一文读懂HfTiO高栅介质GeMOS电容2021-03-29 863

-

介质的相对电介质常数和相对磁导率分参数设置2019-05-21 4029

-

电介质的介电常数是否影响绝缘性能?2019-03-07 10619

-

电介质介电常数大好还是小好_介电常数越大代表什么2018-03-07 318285

-

对介电常数测量的常用方法进行了综合论述2018-01-09 8451

-

低介电常数微波介质陶瓷基覆铜板的研究2017-09-19 3081

-

高介电常数介质对电容层析成像传感器灵敏场影响的研究2009-07-03 1317

全部0条评论

快来发表一下你的评论吧 !